Silicon slice optimal scheduling method and device

A technology for optimizing scheduling and silicon wafers, which is applied in the direction of comprehensive factory control, comprehensive factory control, electrical program control, etc., can solve problems such as unsatisfactory processing equipment, and achieve the effects of increasing productivity, improving execution efficiency, and increasing concurrency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

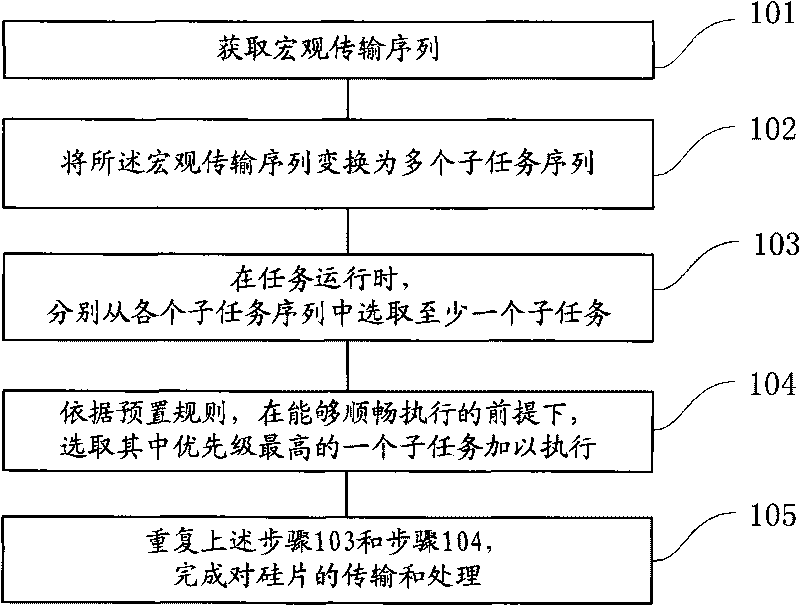

[0069] refer to figure 1 , which shows an embodiment 1 of a method for optimal scheduling of silicon wafers according to the present invention, which may specifically include the following steps:

[0070] Step 101, obtaining a macro transmission sequence (macro transmission sequence);

[0071] Step 102, converting the macro transmission sequence into multiple subtask sequences (or called multiple subtask sequences);

[0072] As specific to the device, the simplest transfer action is also completed by the transfer-related modules, so the execution actions in the macro transfer sequence can be further subdivided. For example, a transfer action can be divided into two subtasks: fetching and putting.

[0073] In the present invention, the macro transmission sequence calculated by the Scheduler module is further subdivided into smaller subtask sequences according to the execution actions of each module, and this series of subtask sequences is finally executed. In the present inv...

Embodiment 2

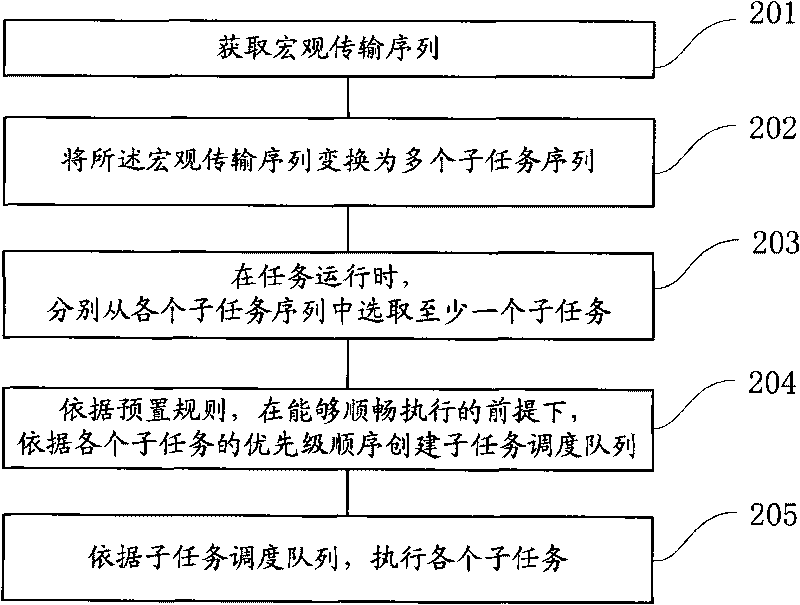

[0146] refer to figure 2 , shows Embodiment 2 of a method for optimal scheduling of silicon wafers according to the present invention, which may specifically include the following steps:

[0147] Step 201, obtaining a macro transmission sequence;

[0148] Step 202, converting the macro transmission sequence into a plurality of subtask sequences;

[0149] Step 203, when the task is running, select at least one subtask from each subtask sequence;

[0150]Step 204, according to preset rules, on the premise of smooth execution, create a subtask scheduling queue according to the priority order of each subtask;

[0151] Step 205: Execute each subtask according to the subtask scheduling queue.

[0152] This example and figure 1 The illustrated embodiments are basically similar, so the similarities will not be repeated. What needs to be emphasized in Embodiment 2 is that it is not like Embodiment 1, which performs a sorting judgment after each subtask is executed, and then execut...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More