Multi-bus protection outlet arbitration fault tolerance system and method

A fault-tolerant system and multi-bus technology, applied in the field of multi-bus protection export arbitration fault-tolerant system, can solve problems such as misoperation or refusal to operate, protection device refusal to operate, and the entire device cannot operate as required, so as to meet the correctness requirements and improve The effect of fault tolerance and guaranteed reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

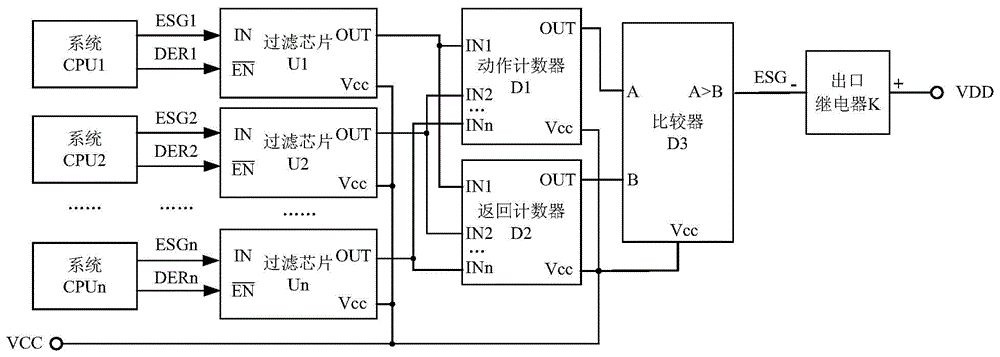

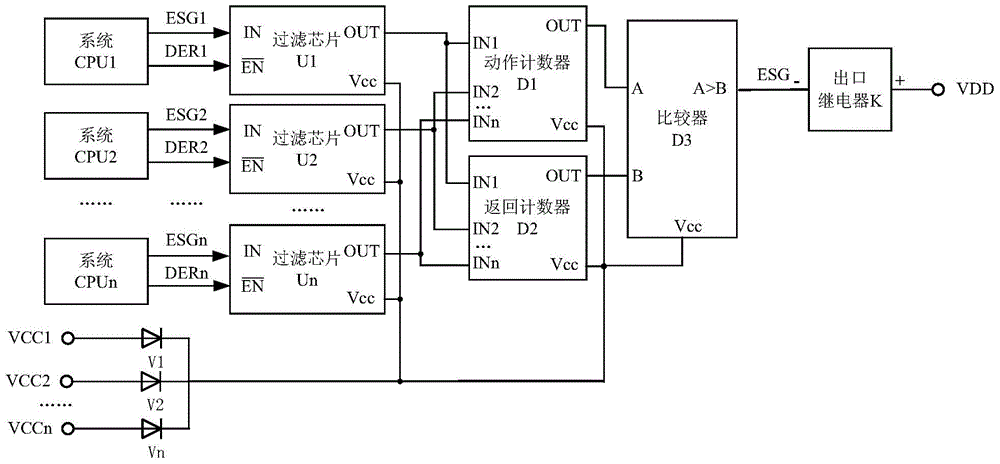

[0046] like figure 1 , In this embodiment, it is composed of CPU (CPU1, CPU2... CPUn), filter chips U1, U2... Un, action counter D1, return counter D2, comparator D3 and outlet relay K. System CPU1, CPU2 ... CPUn output protection exit signal ESG1, ESG2 ... ESGn connected to the input pin IN of the filter chip U1, U2 ... Un, system CPU1, CPU2 ... CPUn output fault signal DER1, DER2 ... DERn connected to the filter chip U1, The enable pins EN of U2 ... Un, the output pins OUT of the filter chips U1, U2 ... Un are respectively connected to the input pins IN1, IN2 ... INn of the action counter D1 and the pins IN1, IN2 ... INn of the return counter D2, The pin OUT of the action counter D1 is connected to the pin A of the comparator D3, the pin OUT of the return counter D2 is connected to the pin B of the comparator D3, and the output pin OUT of the comparator D3 outputs the control signal ESG and the export relay K The negative pole of the input terminal is connected, the positiv...

Embodiment 2

[0053] This embodiment is a special case of Embodiment 1. When the number of CPU systems is 3, the system can evolve into a three-bus protection export arbitration fault-tolerant system, such as Figure 4 As shown, it consists of CPU1, CPU2, CPU3, filter chip U1, filter chip U2, filter chip U3, action counter D1, return counter D2, comparator D3 and export relay K. The system CPU1 output protection exit signal ESG1 is connected to the input pipe IN pin of the filter chip U1, the system CPU1 output fault signal DER1 is connected to the enable pin EN of the filter chip U1, and the system CPU2 output protection exit signal ESG2 is connected to the filter chip U2. IN pin, the system CPU2 output fault signal DER2 is connected to the EN pin of the filter chip U2, the system CPU3 output protection export signal ESG3 is connected to the IN pin of the filter chip U3, and the system CPU3 output fault signal DER3 is connected to the EN pin of the filter chip U3 Pins, the OUT pin of the f...

Embodiment 3

[0056] This embodiment is a special case of embodiment 2. When the number of CPU systems is 2, the system is a dual-bus protection export arbitration fault-tolerant system, such as Figure 5 As shown, it is composed of CPU1, CPU2, filter chip U1, filter chip U2, action counter D1, return counter D2, comparator D3 and export relay K. The system CPU1 output protection exit signal ESG1 is connected to the IN pin of the filter chip U1, the system CPU1 output fault signal DER1 is connected to the EN pin of the filter chip U1, and the system CPU2 output protection exit signal ESG2 is connected to the IN pin of the filter chip U2. The system CPU2 output fault signal DER2 is connected to the EN pin of the filter chip U2, the OUT pin of the filter chip U1 is connected to the IN1 pin of the action counter D1 and the IN1 pin of the return counter D2, and the OUT pin of the filter chip U2 is connected to The IN2 pin of the action counter D1 and the IN2 pin of the return counter D2, the pi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More