Matrix Multiplication Acceleration Method for Heterogeneous Fusion Architecture

An architecture and matrix multiplication technology, applied in the field of matrix multiplication acceleration, which can solve problems such as difficult to meet the performance requirements of many-core accelerators

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

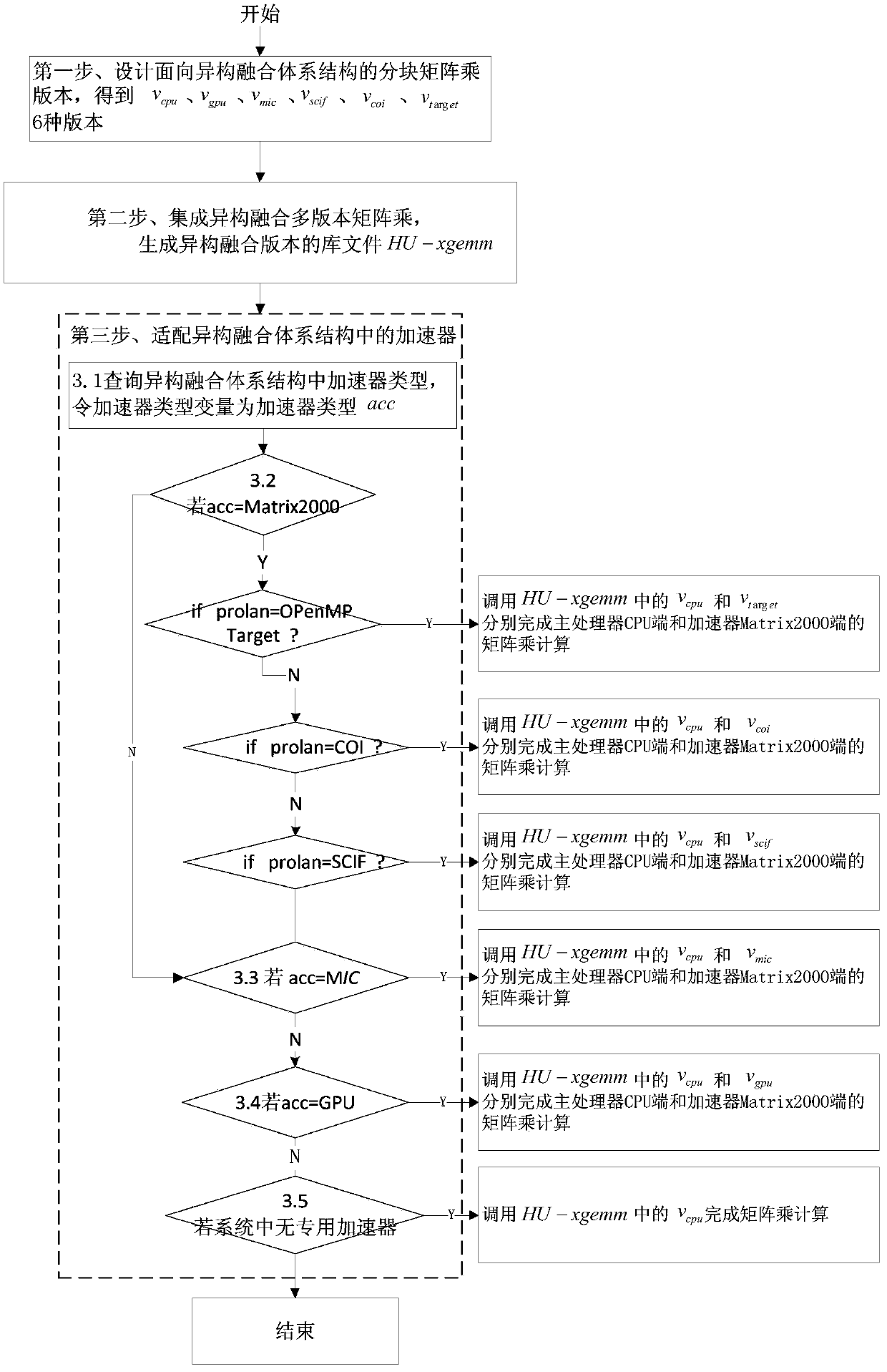

[0167] figure 1 It is an overall flow chart of the matrix multiplication acceleration method for general multi-core DSP of the present invention.

[0168] The steps of the present invention are as follows:

[0169] The first step is to design a block matrix multiplication version for heterogeneous fusion architecture, and get v cpu , v gpu , v mic , v target , v coi and v scif 6 versions, the specific steps are as follows:

[0170] 1.1 Configuration and initialization of heterogeneous fusion architecture, the specific method is:

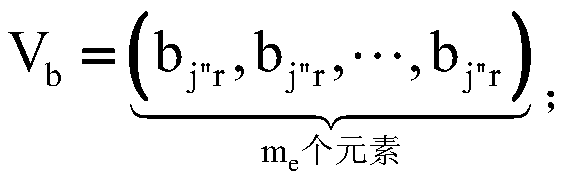

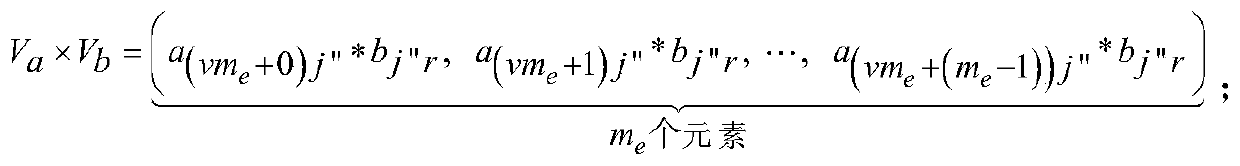

[0171] Define the dimension of matrix A to be M×K, the dimension of matrix B to be K×N, the dimension of matrix C obtained by multiplying A and B to be M×N, where M, K, and N are all positive integers; the pth row of A The qth column element is a pq , 0≤p≤M-1, 0≤q≤K-1, the element of row q and column t of B is b qt , 0≤t≤N-1;

[0172] 1.2 If the heterogeneous fusion architecture is only composed of CPU, initialize the CPU (using MPI progr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More