SRAM circuit yield analysis method based on non-Gaussian sampling

A technique of sampling distribution and Gaussian mixing, applied in electrical digital data processing, instrumentation, calculation, etc., can solve the problems of waste of sampling points and many iterations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

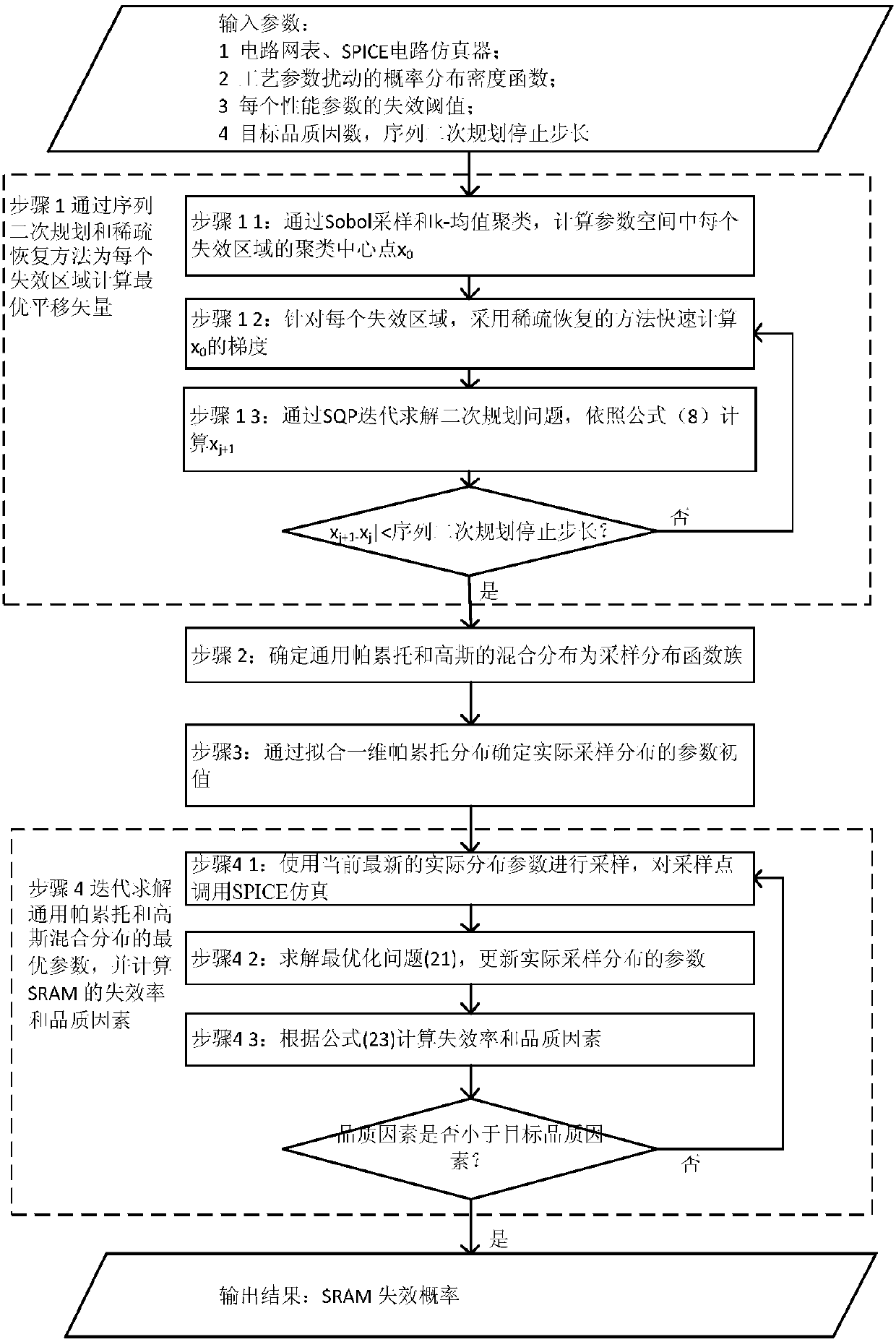

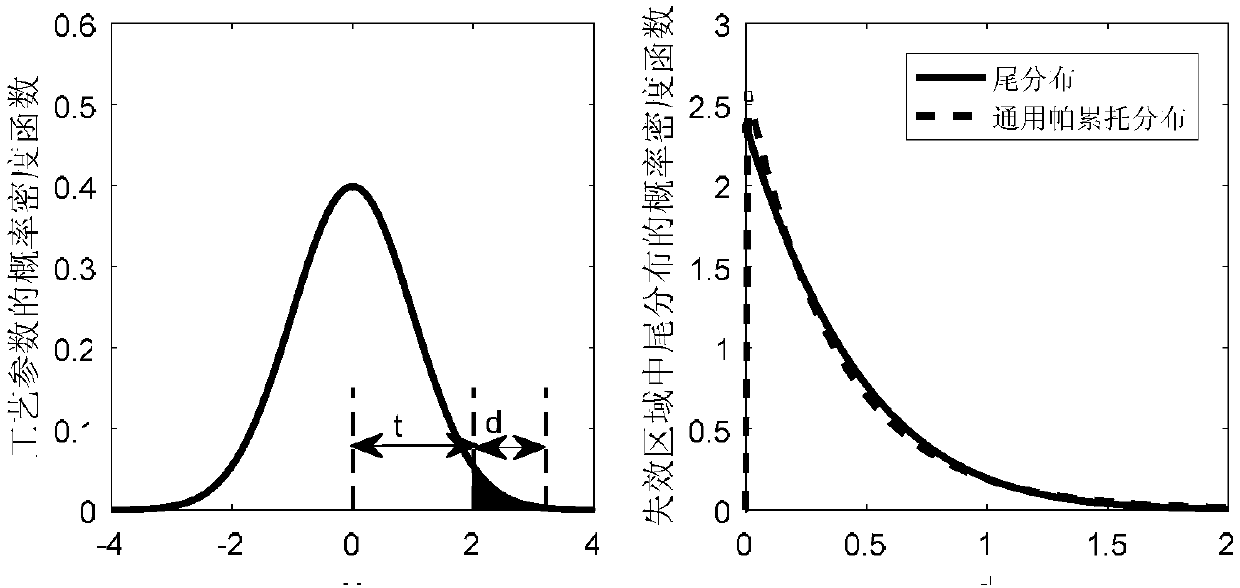

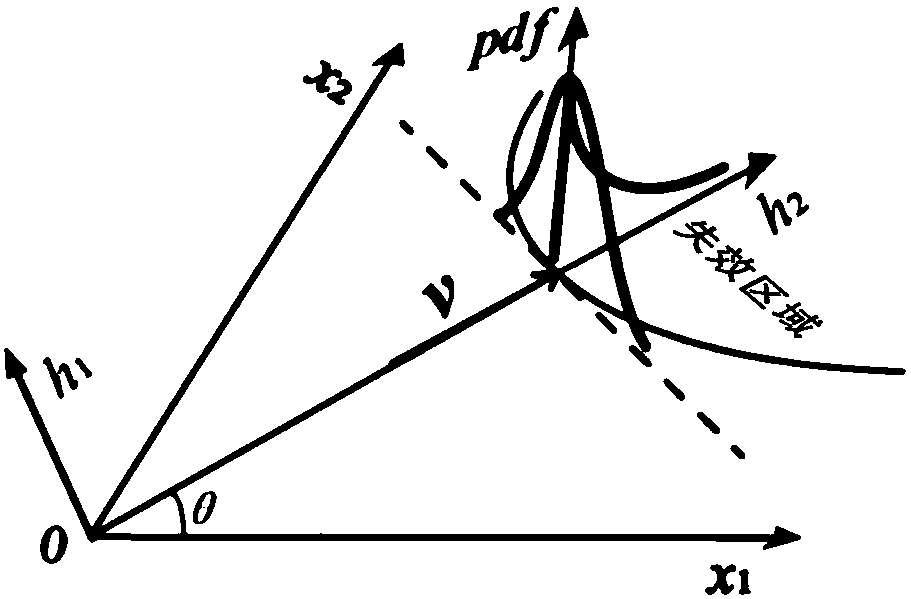

Method used

Image

Examples

Embodiment Construction

[0139] Now, the method of the present invention will be described through the implementation process of specific examples.

[0140] Implementation example 1

[0141] This example uses the Figure 5 circuit shown. Figure 5 It is a schematic diagram of an SRAM cell composed of 6 transistors under the 28nm process. In this example, the reading current I read as a performance indicator. The read current is defined as the current I on the two bit lines BL and I BL_ The difference between them directly affects the discharge speed of the bit line during the read operation. If the read current is less than a certain threshold, it is considered that the SRAM cell read failure.

[0142] Among the input parameters, the parameter space dimension D=6, and the target quality factor ρ=0.0865. The threshold voltages Vth1-Vth6 of the transistors M1-M6 in the circuit are disturbance process parameter variables.

[0143] In this example, the exact solution of the failure rate is 1.20e-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com