Wafer package map error correction system solution

An error correction system and wafer packaging technology, which is applied in the manufacture of electrical components, circuits, semiconductors/solid-state devices, etc., can solve problems such as chip testing failures, and achieve the effect of preventing wafer packaging failures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Wafer packaging map error correction system solution, aiming at the placement station of chip packaging, when the chip is captured, the bad products caused by the pairing of the actual wafer and the map are regarded as good products, which leads to the problem of chip test defect rate. The solution is as follows:

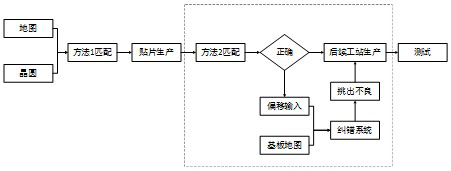

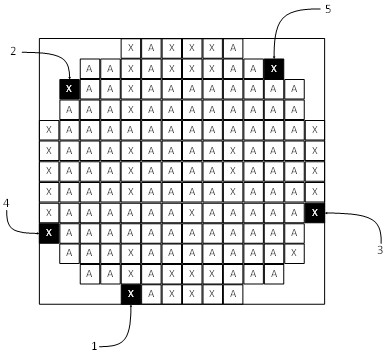

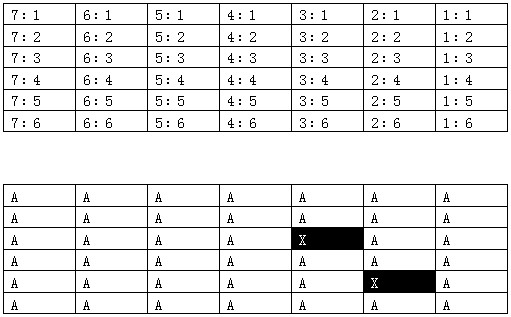

[0022] like figure 1 As shown, the map and the wafer are matched in method 1, and then enter the SMT production. At this time, the substrate map is added to the equipment machine, and the coordinates of each product on the substrate corresponding to the wafer map are recorded. At the same time, after the SMT production, enter the method 2 matching. If the matching is passed through method 2, the map and the wafer are matched correctly, and then enter the subsequent station for production, and then test; if the matching is not passed through method 2, the offset input is performed on the wafer map, and then enters the error correction system with the substrat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More