A Design Method of FPGA-based Steady-state Visual Evoked Potential Brain-Computer Interface System

A steady-state visual evoked and system design technology, applied in computing, mechanical mode conversion, computer components, etc., can solve problems such as frame drop, steady-state visually evoked potential light flicker stimulation, etc., to reduce requirements, save development costs, The effect of improving operating efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

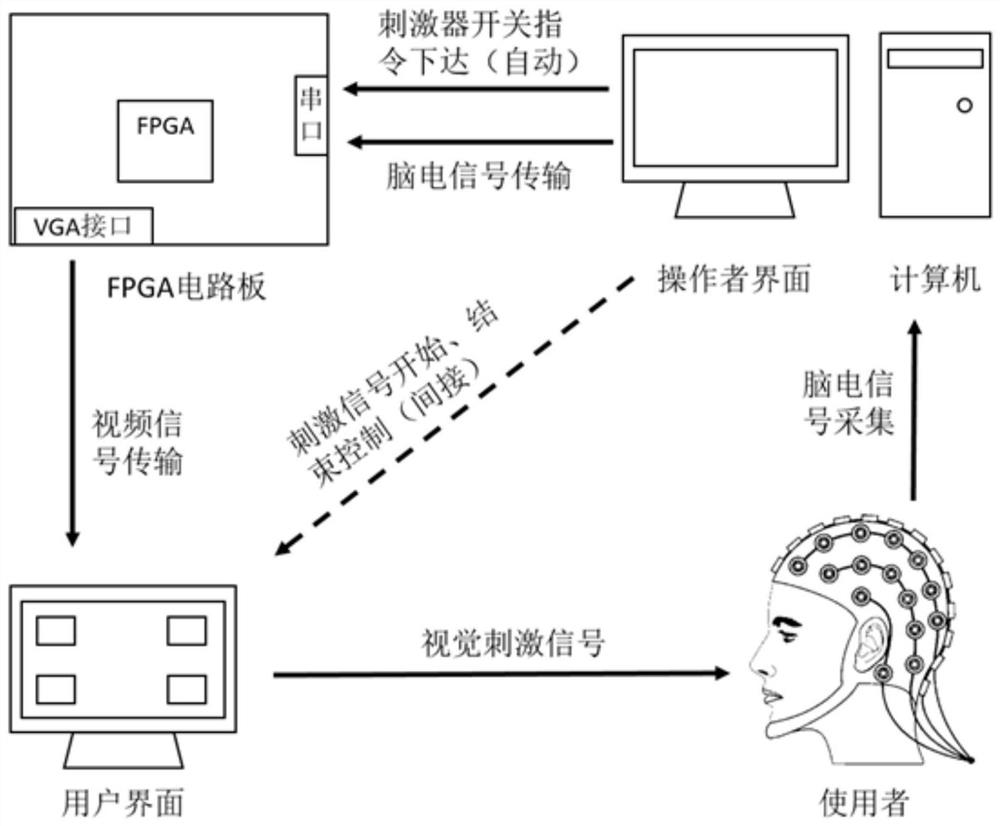

[0037] refer to figure 1 , a method for designing a steady-state visual evoked potential brain-computer interface system based on FPGA, comprising the following steps:

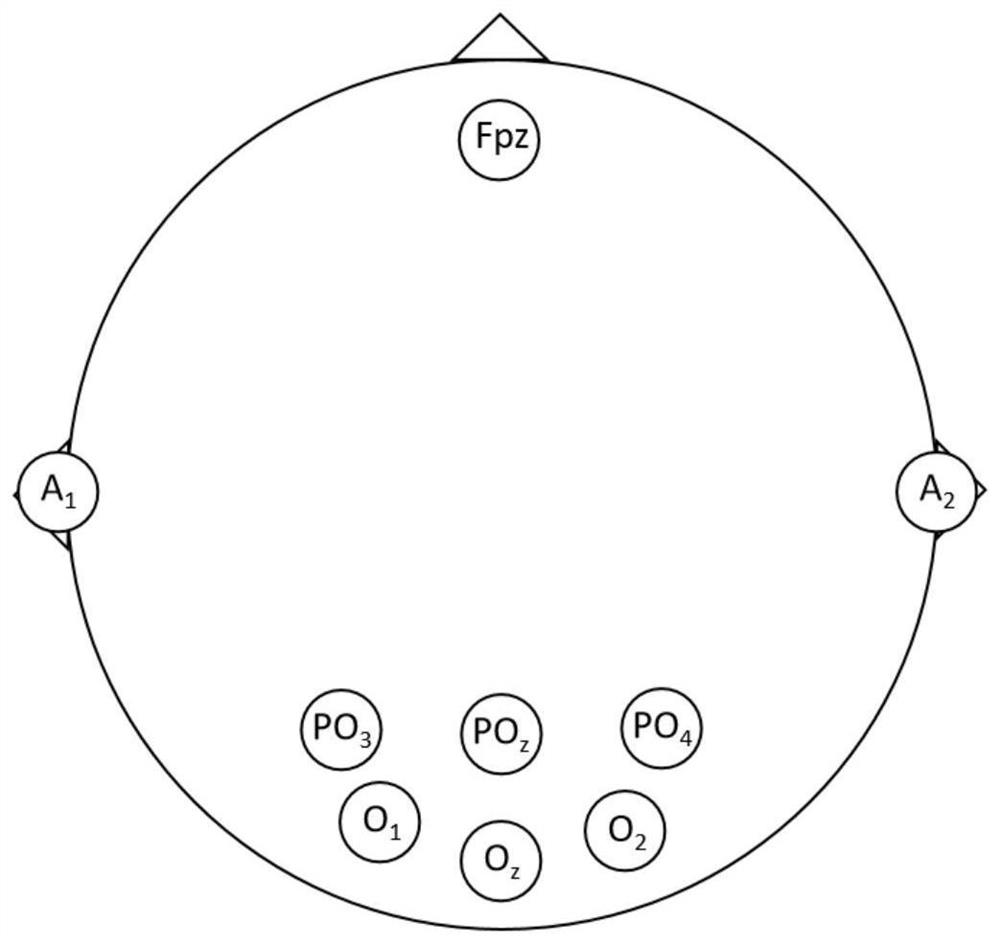

[0038] Step 1, such as figure 2 As shown, according to the international standard lead 10-20 system, the EEG signal measurement electrodes are placed on the PO of the visual occipital area of the user's head through the EEG cap. 3 、PO z 、PO 4 , O 1 , O z and O 2 Position, place the ground electrode at the Fpz position of the forehead, and place the ground electrode at any earlobe position A1 or A 2 The reference electrode is placed, and the measured EEG signal is amplified by professional acquisition equipment, converted from analog to digital, and then transmitted to the computer;

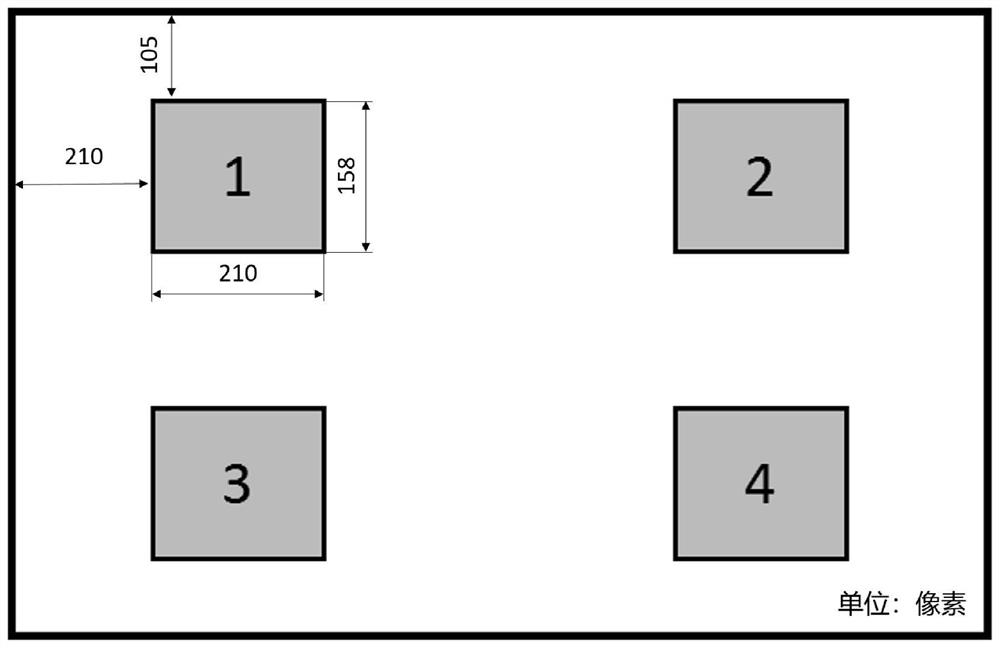

[0039] Step 2, refer to image 3 , present four steady-state stimulation units fli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More