Preparation method of salient points with different specifications and sizes

A bump and size technology, used in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as growing bumps of different sizes, and achieve the effect of reducing production costs and cycles and improving production efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

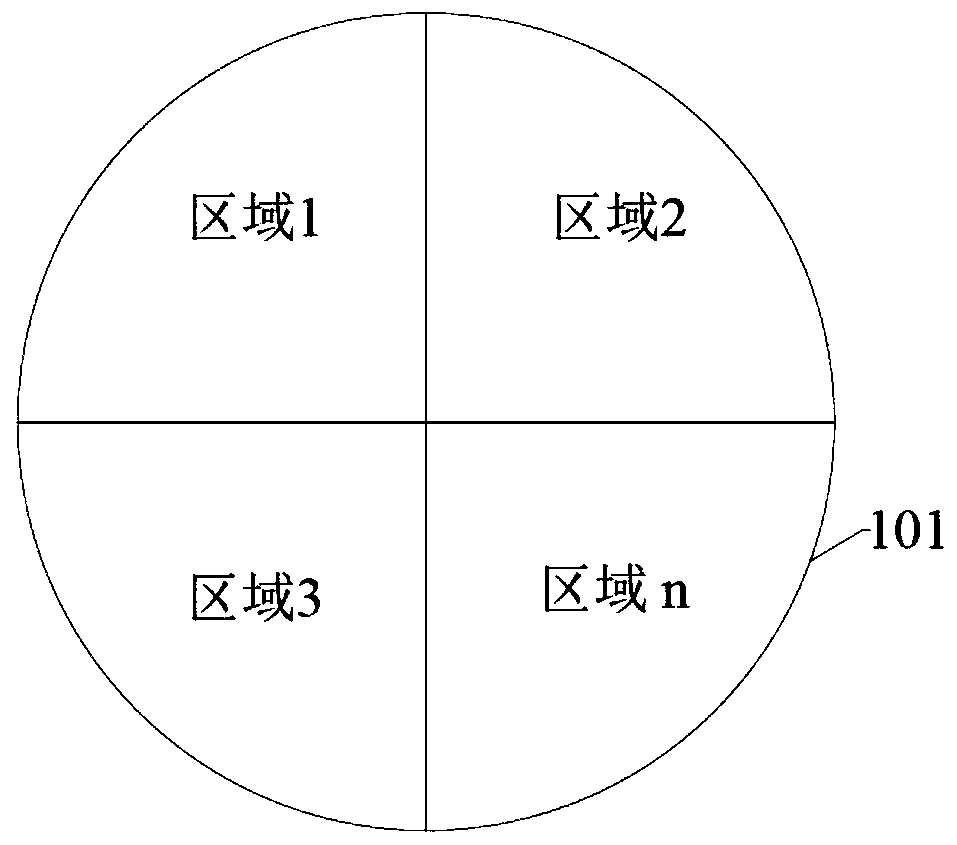

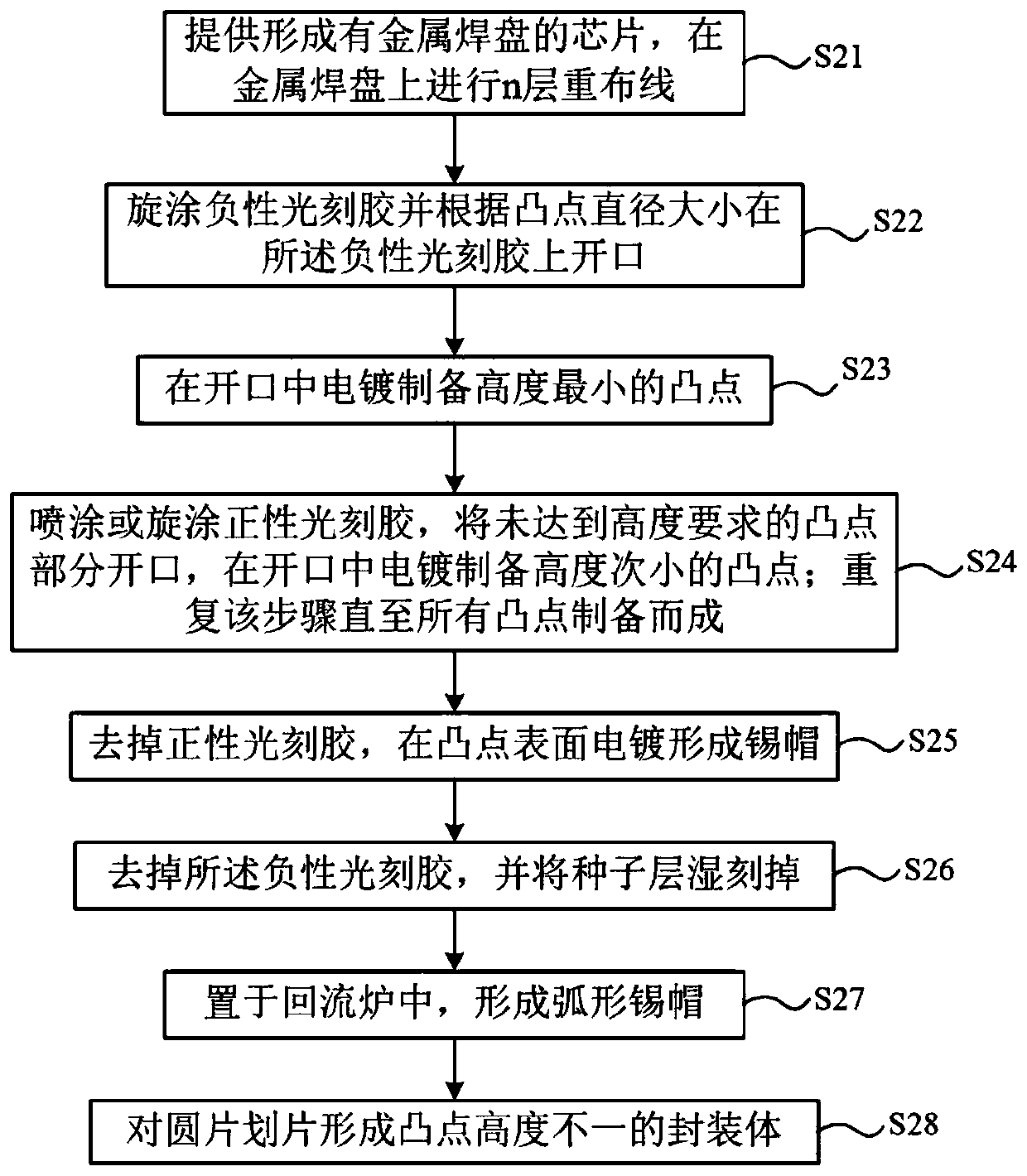

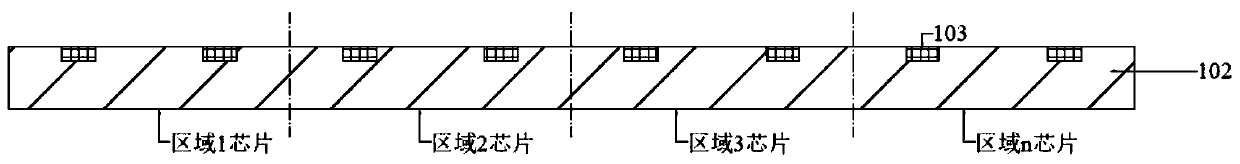

[0043] figure 1 It is an MPW wafer, including wafer 101, in which different chips are distributed in different regions, the size of the chip bumps in each region is the same, and the height of the chip bumps in different regions is different. The invention provides a method for preparing bumps with different specifications and sizes, and the process is as follows figure 2 As shown, including the following steps:

[0044] Step S21, providing a chip formed with metal pads, and performing n-layer rewiring on the metal pads;

[0045] Step S22, spin-coating a negative photoresist and make openings on the negative photoresist according to the diameter of the bumps;

[0046] Step S23, electroplating in the opening to prepare bumps with the smallest height;

[0047] Step S24, spraying or spin-coating positive photoresist, opening the bumps that do not meet the height requirement, and electroplating in the openings to prepare bumps with the next smallest height; repeat this step until all bum...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More