High-speed low-power-consumption SAR ADC capacitor mismatch self-calibration method and circuit

A capacitance mismatch and calibration circuit technology, applied in analog/digital conversion calibration/testing, electrical components, electrical signal transmission systems, etc., can solve the problems of low power consumption, capacitance mismatch, etc., and achieve the effect of low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The present invention will be further described below in conjunction with accompanying drawings and examples.

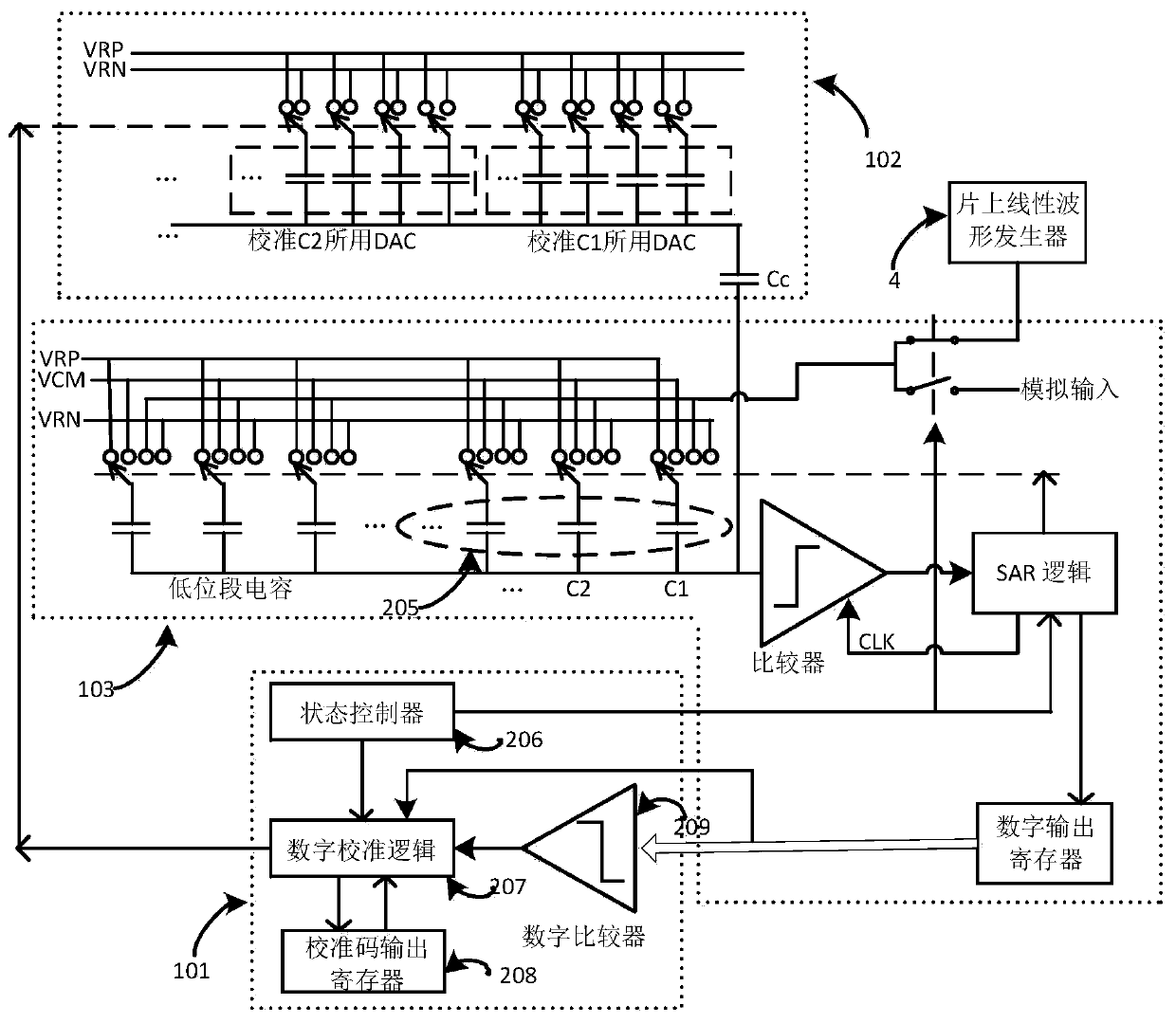

[0016] The present invention is a capacitance mismatch self-calibration method and circuit applied in a high-speed SAR ADC, and its circuit framework is as follows figure 1 As shown, the entire ADC circuit is mainly composed of a calibration circuit module 101 , a calibration capacitor module 102 , a SAR ADC core conversion module 103 , and an on-chip linear waveform generator 104 .

[0017] The SAR ADC core conversion module contained in the calibration circuit is a full-capacitance asynchronous clock SAR ADC, and its high n bits (C1, C2,...) need to be calibrated, and the value of n is related to the number of bits of the designed ADC, which needs to be calibrated The capacitance is 205; each capacitor that needs to be calibrated corresponds to the capacitance segment of different segments in the calibration capacitor module, and the calibration capacitor on...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com