HDP+FPGA-based compression and decompression reference performance verification method, system and device

A verification method and verification system technology are applied in the field of performance verification based on HDP+FPGA compression and decompression benchmarks, which can solve problems such as inability to effectively verify FPGA task load, and achieve the effects of improving test efficiency, ensuring product quality, and being easy to use.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] Specific embodiments of the present invention will be described below in conjunction with the accompanying drawings.

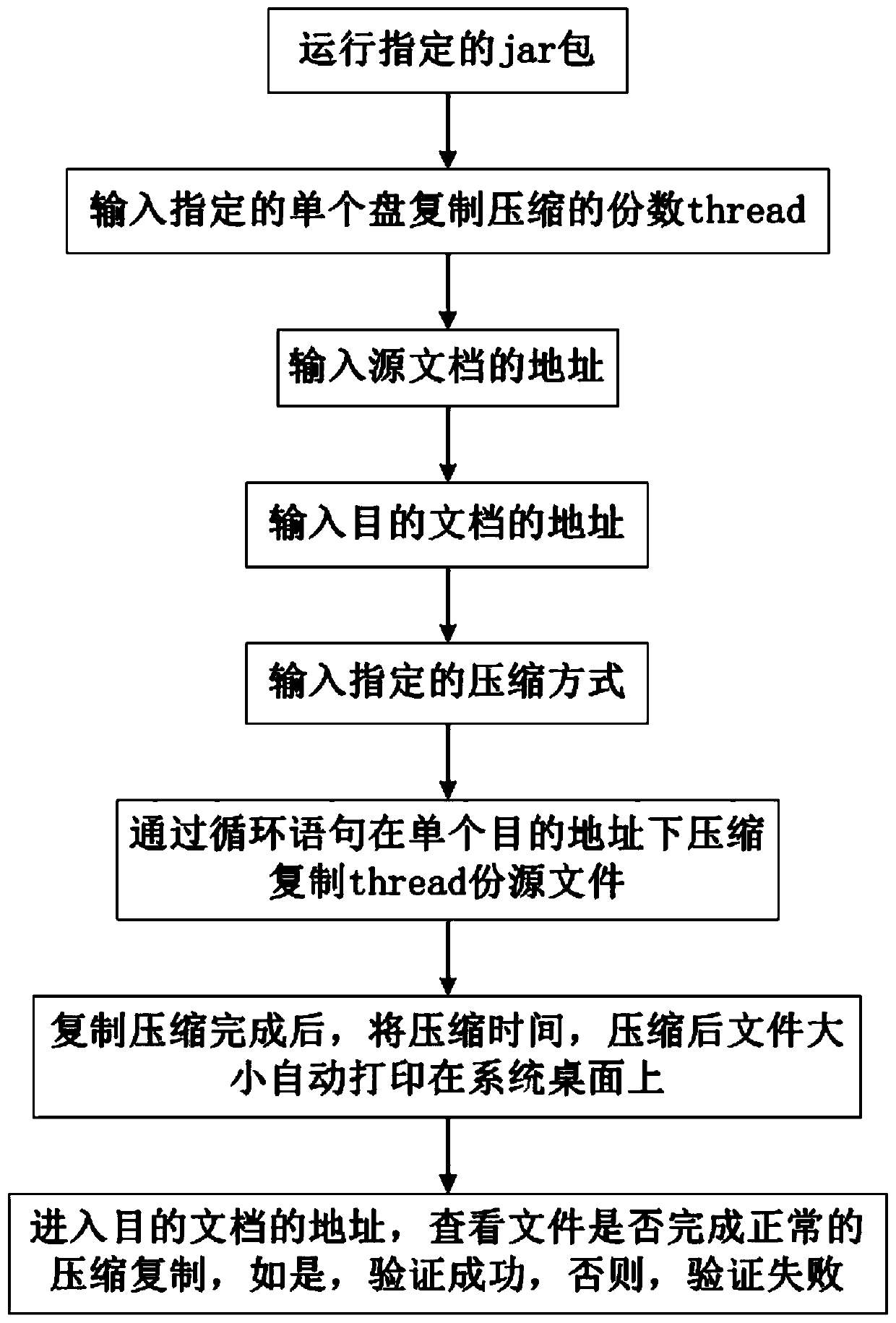

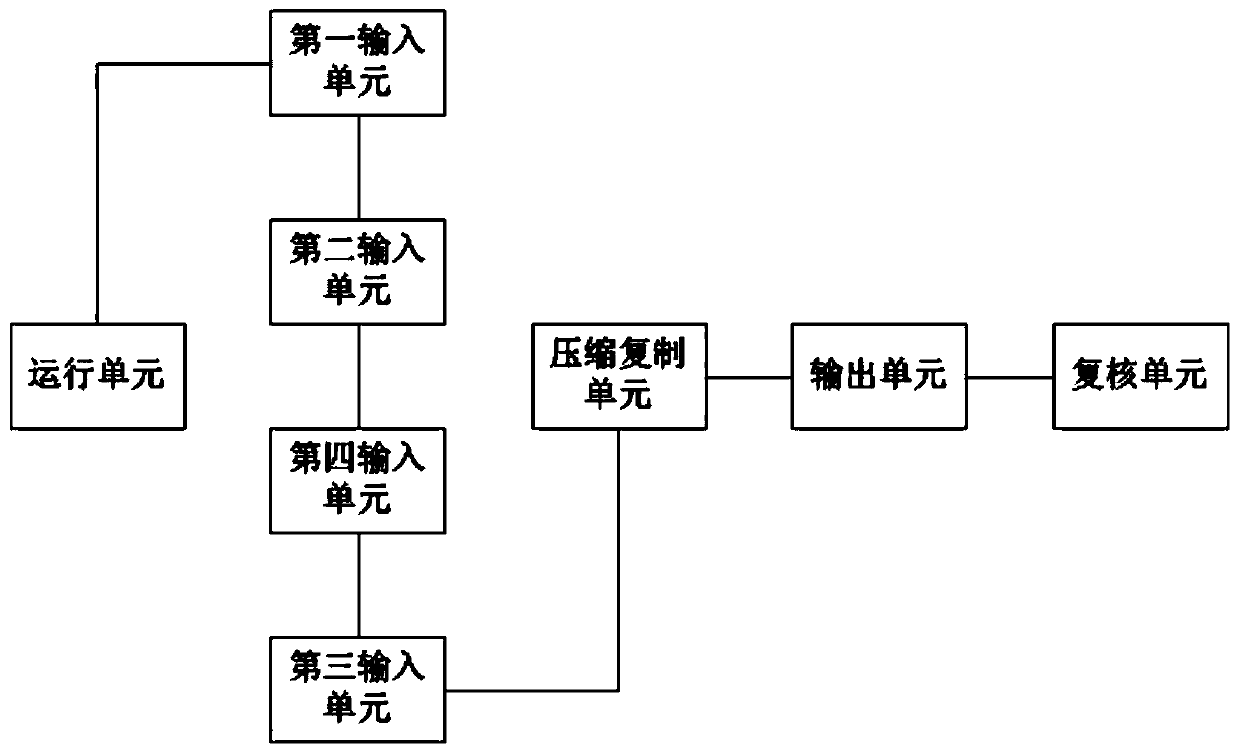

[0042] like figure 1 As shown, the present invention provides a kind of benchmark performance verification method based on HDP+FPGA compression and decompression, comprising the following steps:

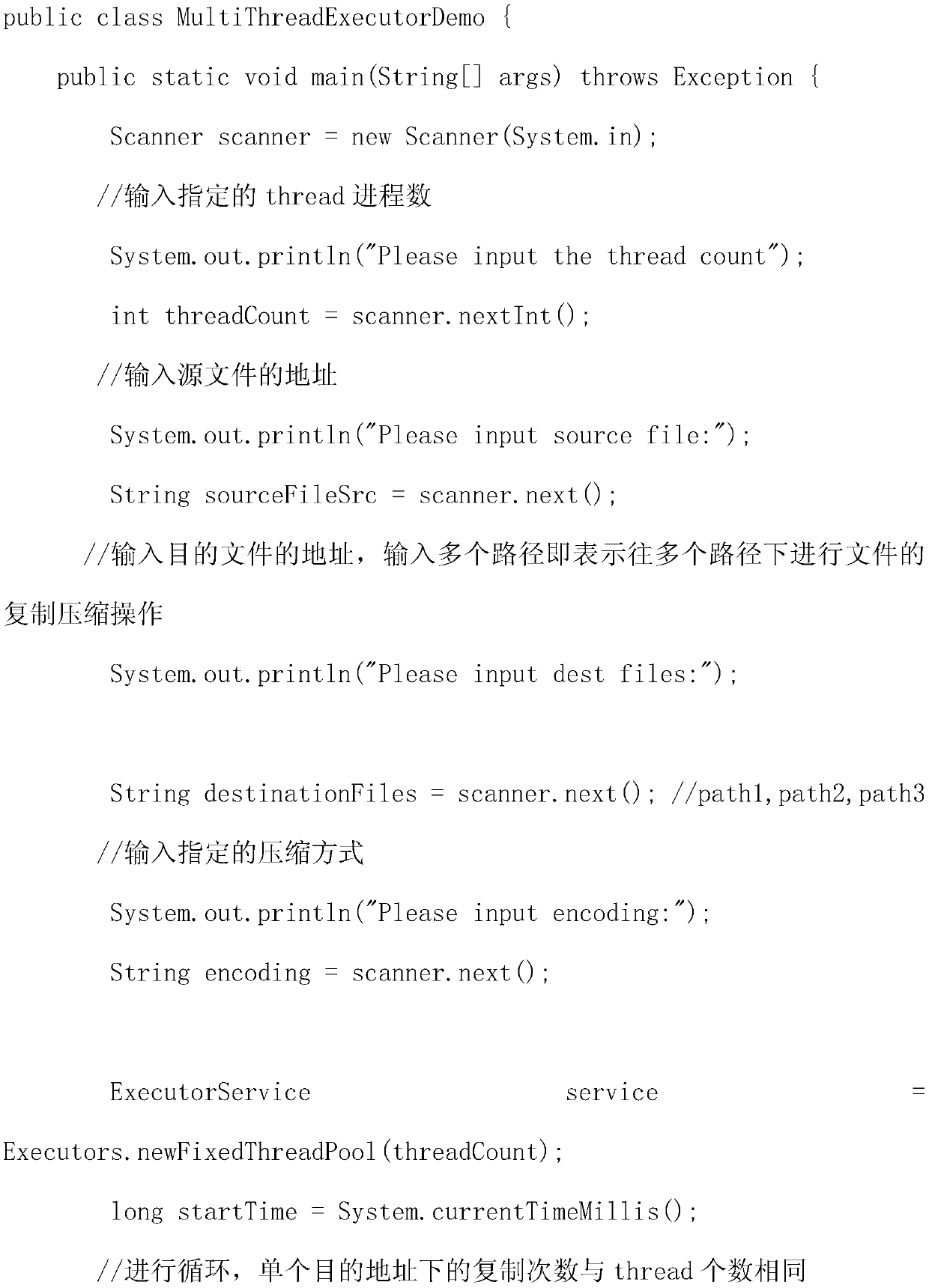

[0043] S1: Run the specified jar package. Specifically: use the Hadoop running tool, input the hadoop jar+jar package, and run the jar package.

[0044] S2: Enter the number of copies of the specified single disk copy compression thread.

[0045] S3: Enter the address of the source document.

[0046] S4: Input the address of the target document. Specifically, fill in the address of the specific destination file, and separate multiple addresses with commas. Entering multiple paths means copying and compressing files to multiple paths.

[0047] S5: Enter the specified compression method. If the compression method is not specified, only multi-process copyi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com