Cache access system

A cache and access system technology, applied in image communication, selective content distribution, electrical components, etc., can solve the problems of wasting hardware space, limited cache efficiency, and high frequency of cache misses

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

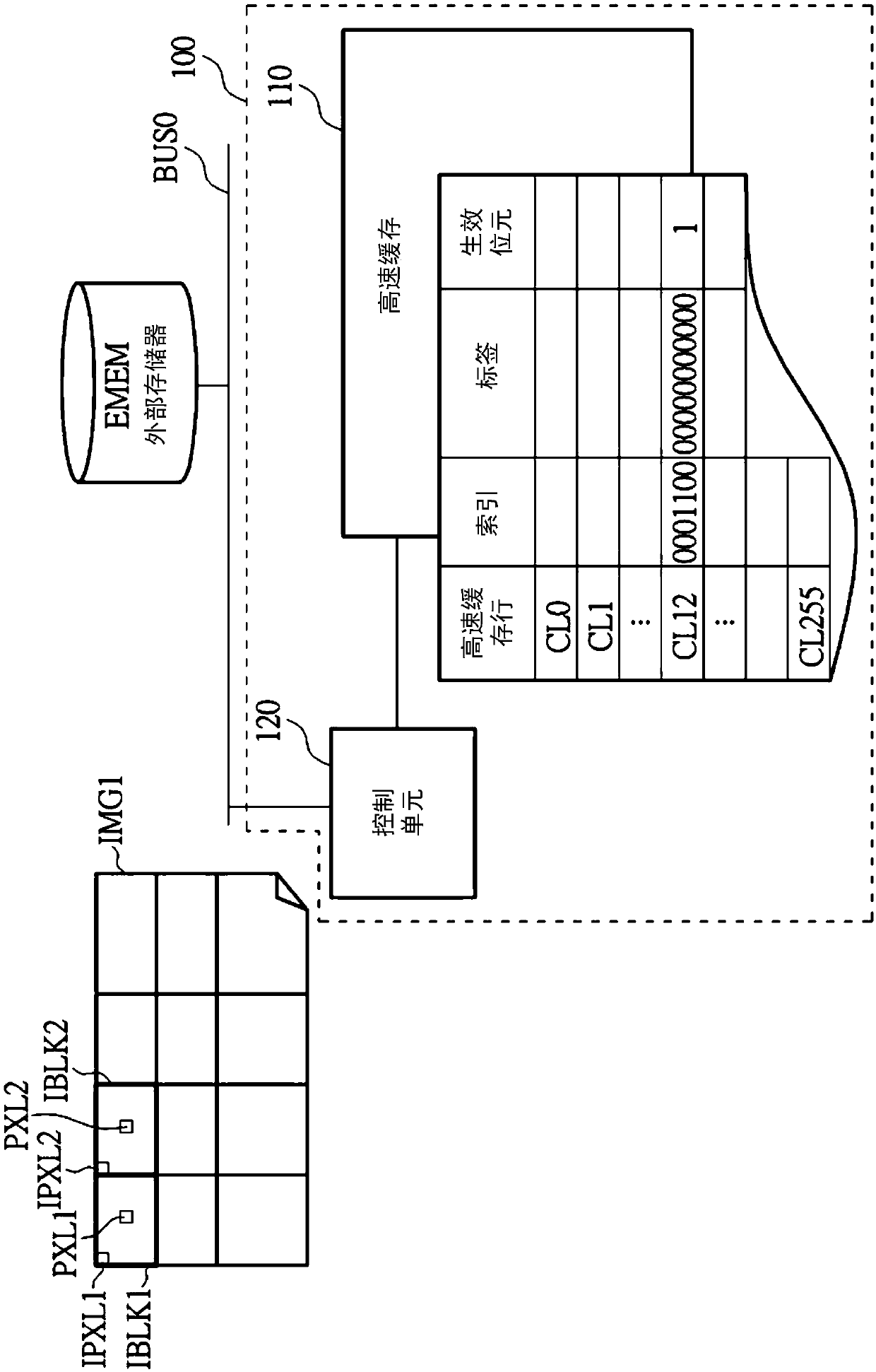

[0038] figure 1 It is a schematic diagram of a cache access system 100 according to an embodiment of the present invention. The cache access system 100 includes a cache 110 and a control unit 120 . In some embodiments of the present invention, the cache access system 100 can be applied to image compression.

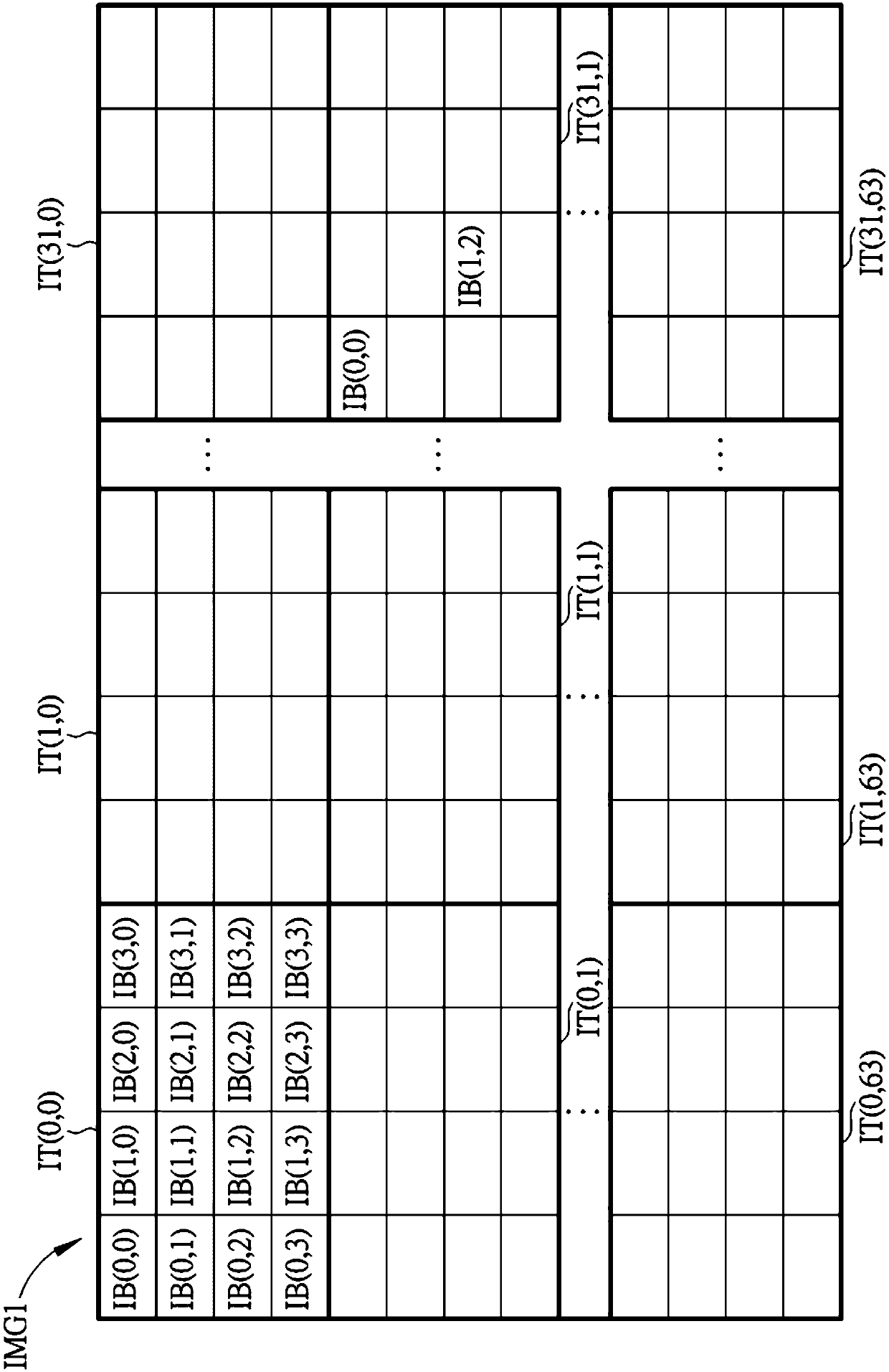

[0039] In practice, in order to improve the utilization efficiency of hardware resources, when compressing the data of a frame, a frame can be divided into multiple image tiles (tiles) and / or multiple image blocks (blocks). Each image block in a frame is compressed sequentially. For example, the original picture can be divided into 2 A x2 B image tiles, and each image tile contains 2 ΔX x2 ΔY blocks, wherein A, B, ΔX and ΔY are natural numbers, that is, zero or positive integers.

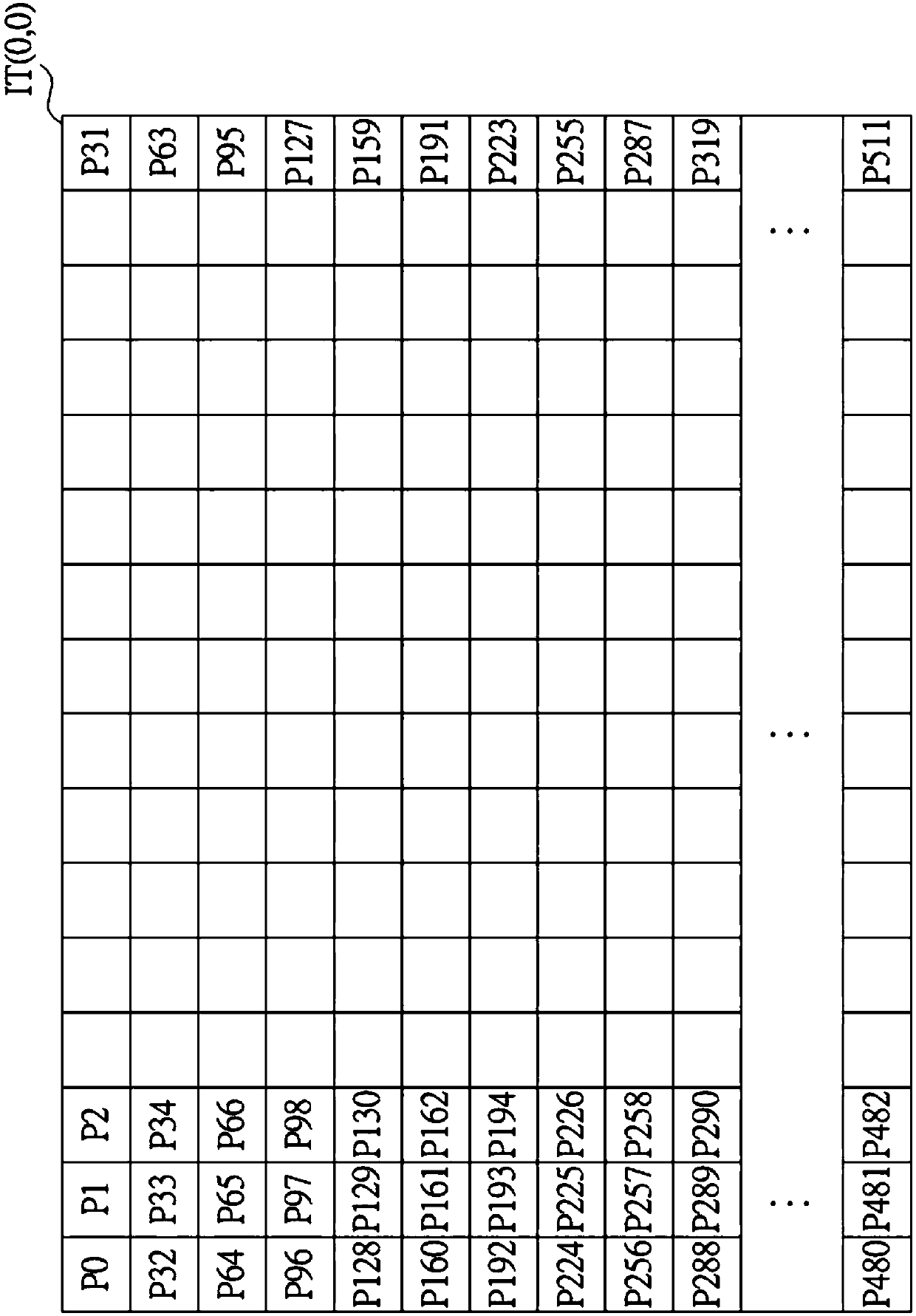

[0040] figure 2 It is a schematic diagram of the image tiles and image blocks of the original picture IMG1 according to an embodiment of the present invention. figure 2 In an exampl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More