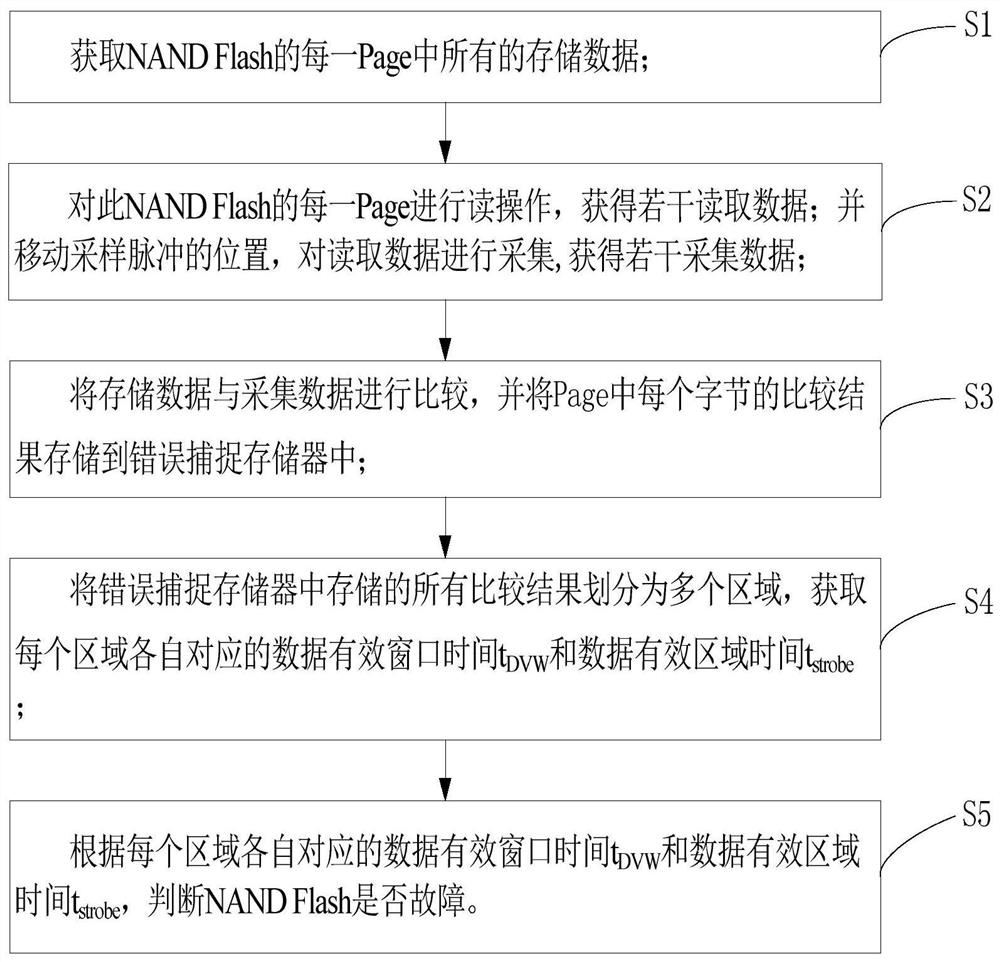

A kind of nand Flash timing test method

A technology of timing testing and timing, which is applied in the direction of faulty hardware testing methods, error detection/correction, and detection of faulty computer hardware, etc., and can solve problems such as inability to test NAND Flash timing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

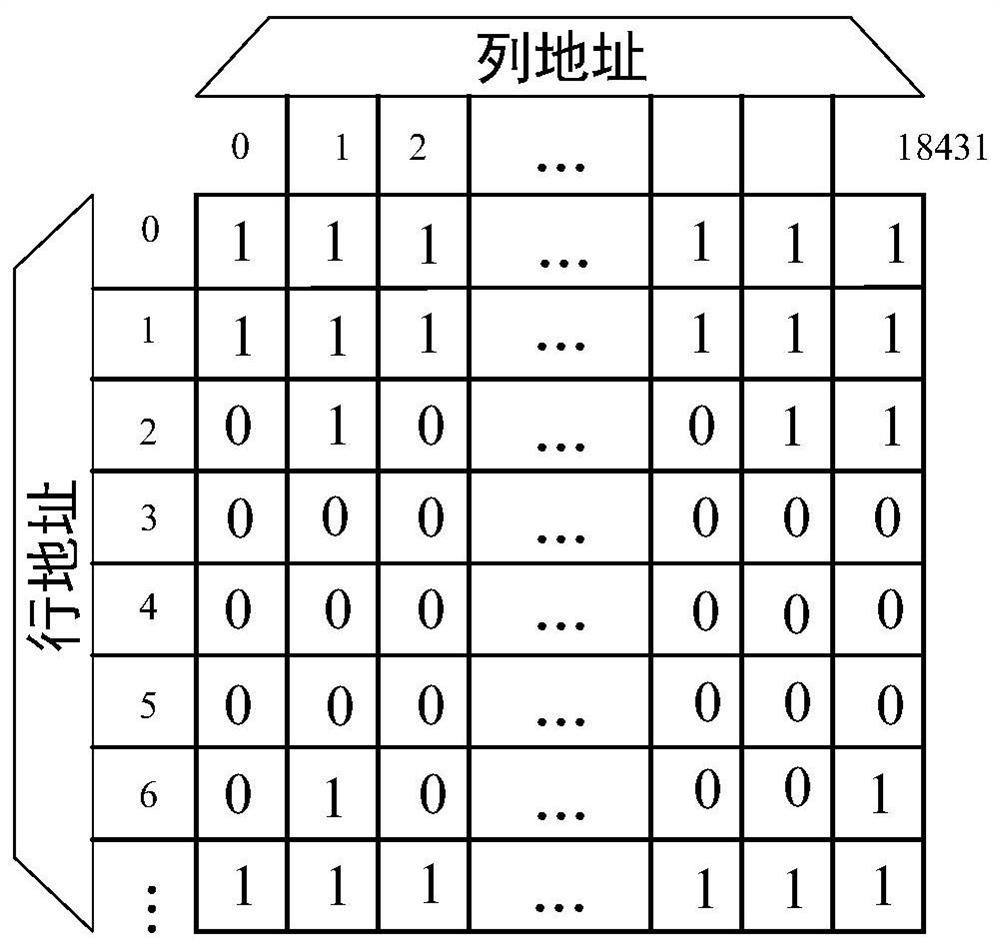

Method used

Image

Examples

Embodiment Construction

[0041] The specific implementation manners according to the present invention will be described below in conjunction with the accompanying drawings.

[0042] In the following description, many specific details are set forth in order to fully understand the present invention, but the present invention can also be implemented in other ways different from those described here, therefore, the present invention is not limited to the specific embodiments disclosed below limit.

[0043] At present, due to the high degree of chip integration, testing of NAND Flash chips is usually performed by automatic test equipment (ATE); during the test process, it is judged whether the chip has a fault by comparing whether the data input and output by the chip are the same.

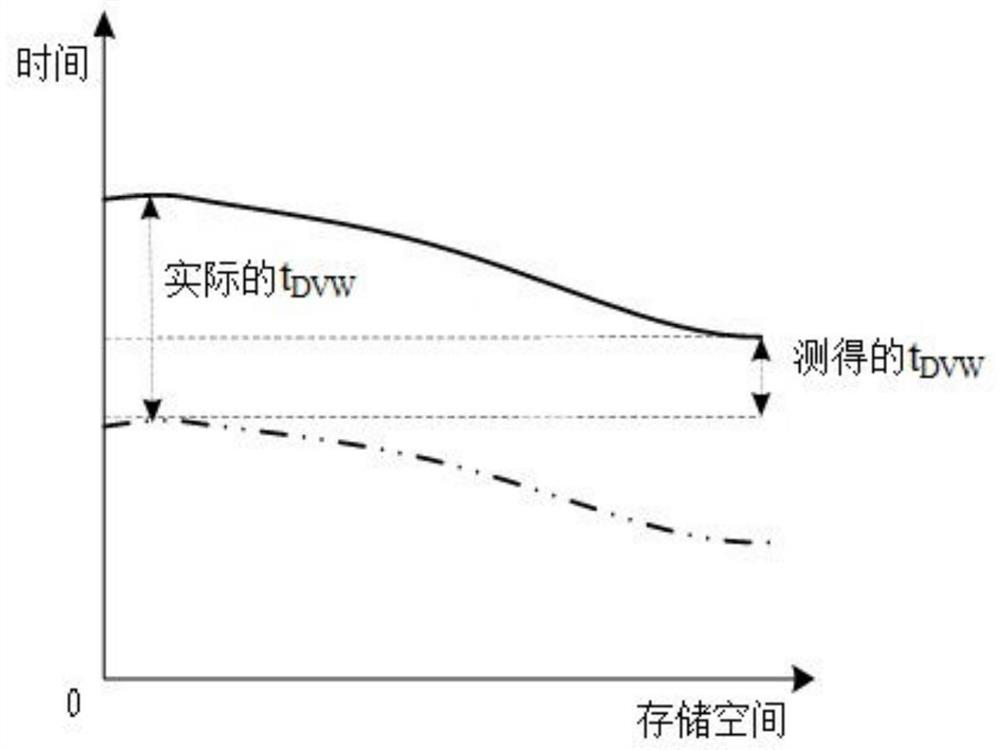

[0044] DDR3 mode has more data selection pulse (DQS) than SDR mode. The DQS signal is generated inside the chip after the read operation is enabled, and is used to accurately distinguish each transmission cycle within one c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More