Embedded gate structure and manufacturing method thereof

A technology of gate structure and manufacturing method, applied in the field of buried gate structure and its manufacturing, can solve the problem that transistors cannot take into account performance and integration at the same time, so as to improve short-channel effect, improve device integration, and increase device integration. The effect of large drive current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

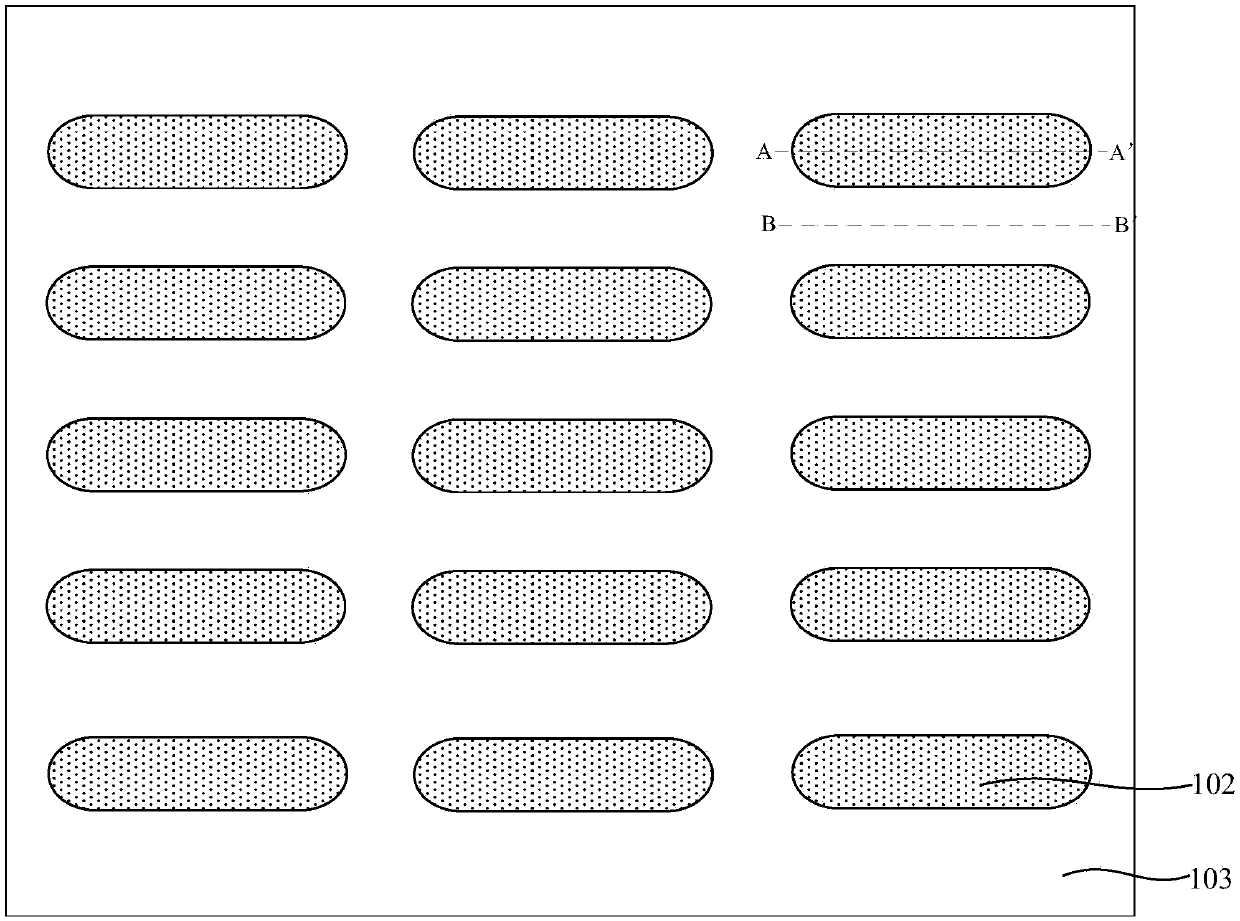

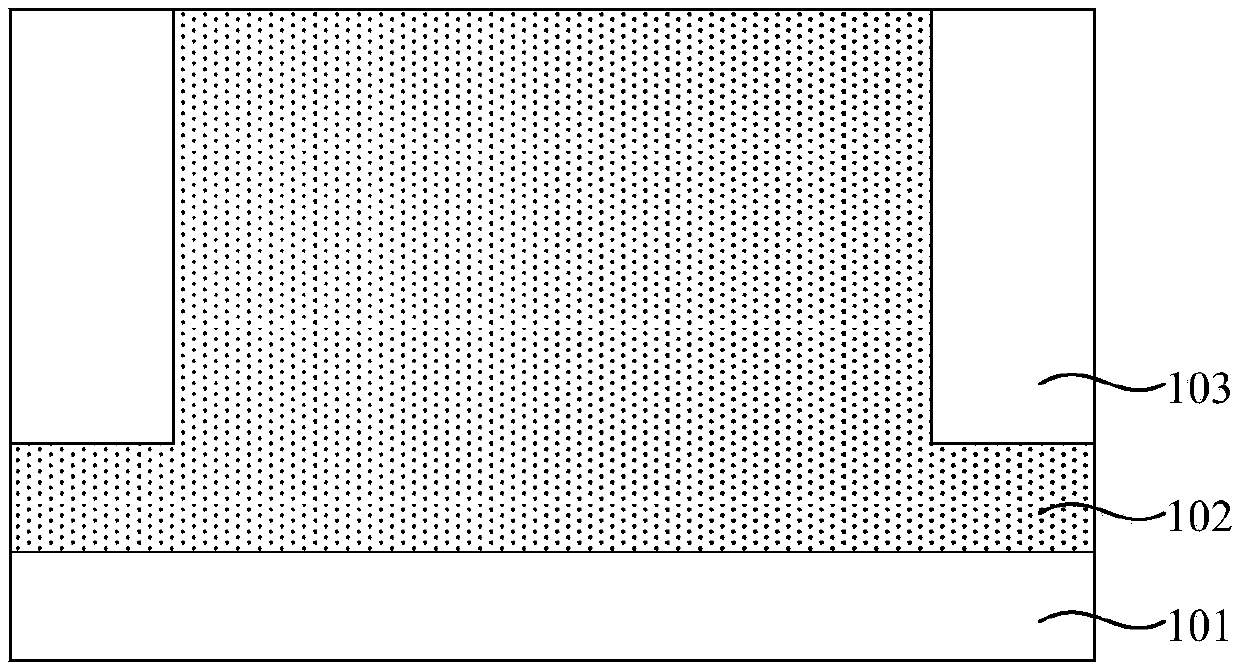

[0055] Such as Figure 1 to Figure 3 As shown, a semiconductor substrate 101 is provided, and an active region 102 and a shallow trench isolation structure 103 isolating the active region 102 are formed in the semiconductor substrate 101 . It should be noted that the method for forming the active region 102 and the shallow trench isolation structure 103 in this step is an existing method, so details will not be repeated here.

[0056] Such as Figure 4 to Figure 17 As shown, an active trench 112 is formed in the active region 102, and an isolation trench 114 is formed in the shallow trench isolation structure 103; the active trench 112 includes The front active trench 105 in 102, and the rear active trench 111 formed at the bottom of the front active trench 105, wherein the width of the rear active trench 111 is greater than that of the front active trench The width of the trench 105; the isolation trench 114 includes the front isolation trench 106 formed in the shallow tren...

Embodiment 2

[0088] The difference between this embodiment and Embodiment 1 is that in this embodiment, after the front-stage active trench 105 and the rear-stage active trench 111 are formed in the active region 102, the shallow trench A front isolation trench 06 and a rear isolation trench 113 are formed in the isolation structure 103 . The specific method is as follows: etching the active region 102 to form a front active trench 105 in the active region 102; and then etching the bottom of the front active trench 105 to form forming a rear active trench 111 at the bottom of the front active trench 105; and etching the shallow trench isolation structure 103 to form a front isolation trench 106 in the shallow trench isolation structure 103 and then etch the bottom of the front isolation trench 106 to form a rear isolation trench 113 at the bottom of the front isolation trench 106 ; It should be noted that the present embodiment differs from the first embodiment only in the formation seque...

Embodiment 3

[0090] Such as Figure 18 and Figure 19 As shown, this embodiment provides a buried gate structure manufactured by the method described in Embodiment 1 or Embodiment 2, and the buried gate structure includes:

[0091] A semiconductor substrate 101, an active region 102 and a shallow trench isolation structure 103 isolating the active region 102 are formed in the semiconductor substrate 101;

[0092] The active trench 112 includes the front active trench 105 formed in the active region 102, and the rear active trench 111 formed at the bottom of the front active trench 105, wherein the rear The width of the active trench 111 is greater than the width of the front active trench 105;

[0093] The isolation trench 114 includes the front isolation trench 106 formed in the shallow trench isolation structure 103, and the rear isolation trench 113 formed at the bottom of the front isolation trench 106, wherein the rear isolation trench The width of the groove 113 is greater than th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More