A method and system for on-orbit reconfiguration of on-board fpga

A spaceborne and configuration data technology, applied in response to error generation, program loading/starting, error detection/correction, etc., can solve low reliability, failure to find errors, and inability to realize on-orbit reconstruction of on-orbit reliability of on-board FPGA and other issues to achieve the effect of ensuring correctness, improving data reliability, and highly reliable on-orbit reconstruction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

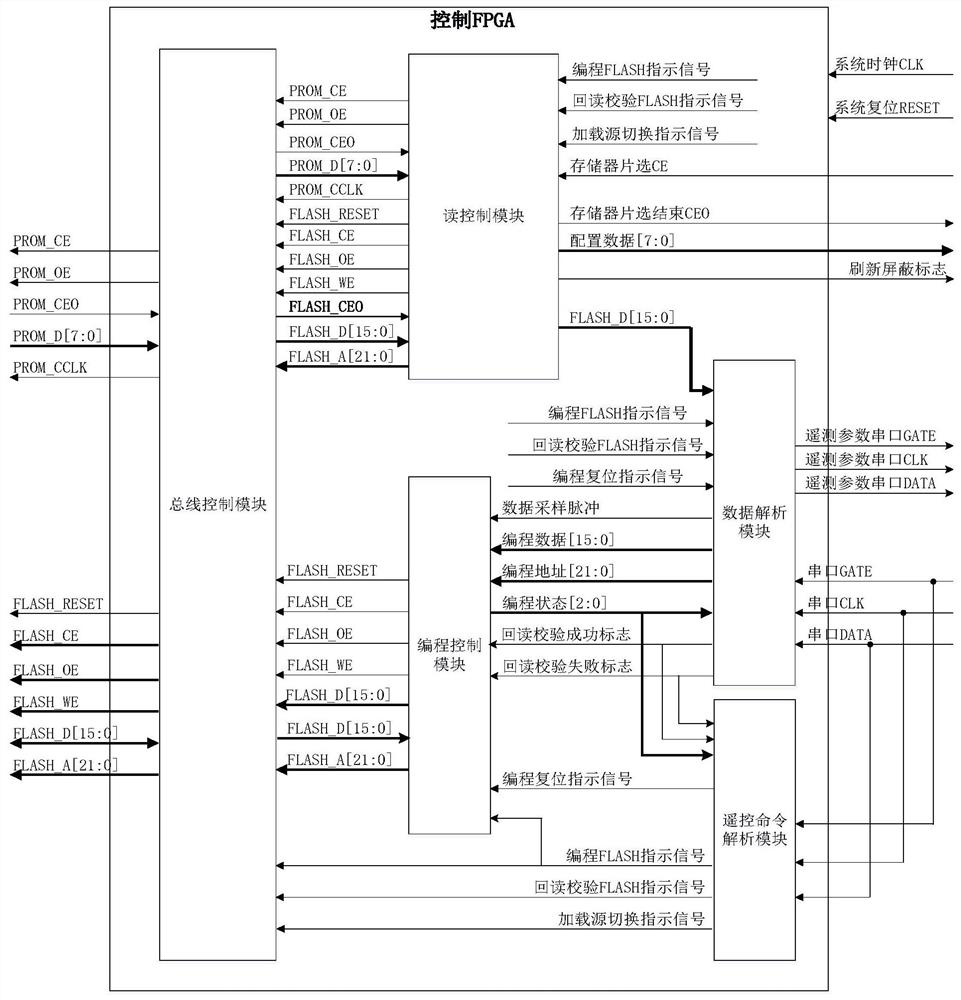

[0100] The embodiment of the present invention also provides an on-orbit reconstruction system, such as figure 1 shown. The control FPGA is composed of a data analysis module, a read control module, a programming control module, a remote control instruction analysis module and a bus control module. The control FPGA performs on-orbit reconstruction for the configuration memory FLASH of the processing FPGA.

[0101] The read control module is connected to the bus control module through the PROM interface and the FLASH interface.

[0102] The PROM interface includes a PROM data interface and a PROM control interface; the FLASH interface includes a FLASH data interface and a FLASH control interface.

[0103] The read control module is connected to the data analysis module through the FLASH data interface.

[0104] The read control module is connected to the load control logic through the memory chip select signal interface.

[0105] The programming control module is connected t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More