Boundary clock window determination method, circuit and terminal equipment and storage medium

A boundary clock and determination method technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of low efficiency, poor adaptability, etc., and achieve the effect of low efficiency, poor adaptability, and simple design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to have a clearer understanding of the technical features, purposes and effects of the present invention, the specific implementation manners of the present invention will now be described with reference to the accompanying drawings.

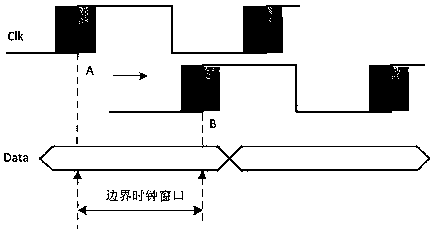

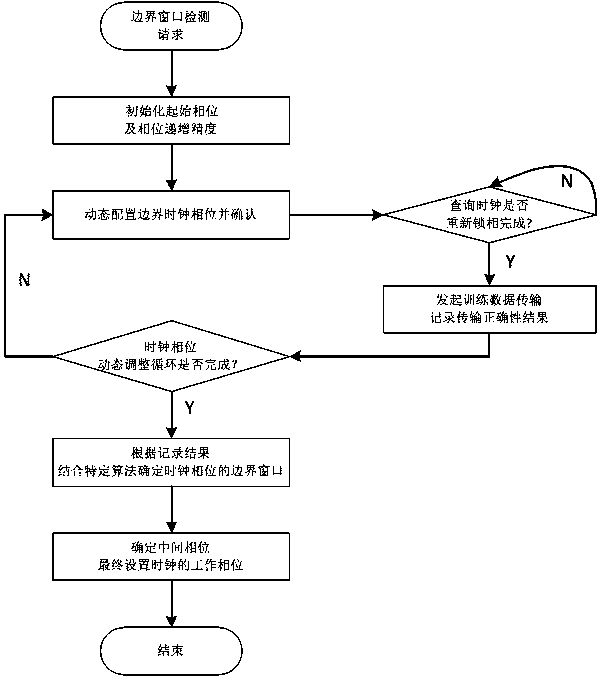

[0041] In this example, if figure 2 As shown, a method for determining the boundary clock window includes dynamic clock configuration: FPGA initializes dynamic clock configuration according to the dynamic configuration command; training data transmission: CPU queries the clock lock status information of FPGA and transmits training data to FPGA; phase cycle interval test : Traversing the entire phase cycle interval for dynamic clock configuration and transmission training; clock window determination: Obtain the transmission correctness test results returned by the FPGA, and re-initiate clock locking according to the test results to complete the clock window determination.

[0042] Specifically, a method for determining a boundary...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More