EDA verification platform based on Python language and use method thereof

A verification platform and language technology, applied in the field of FPGA verification, can solve the problems of high requirements for hardware verification engineers, unfavorable users' rapid use and promotion, and achieve the effect of simplifying verification work, lowering the use threshold, and improving quality and efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described below in conjunction with specific embodiments.

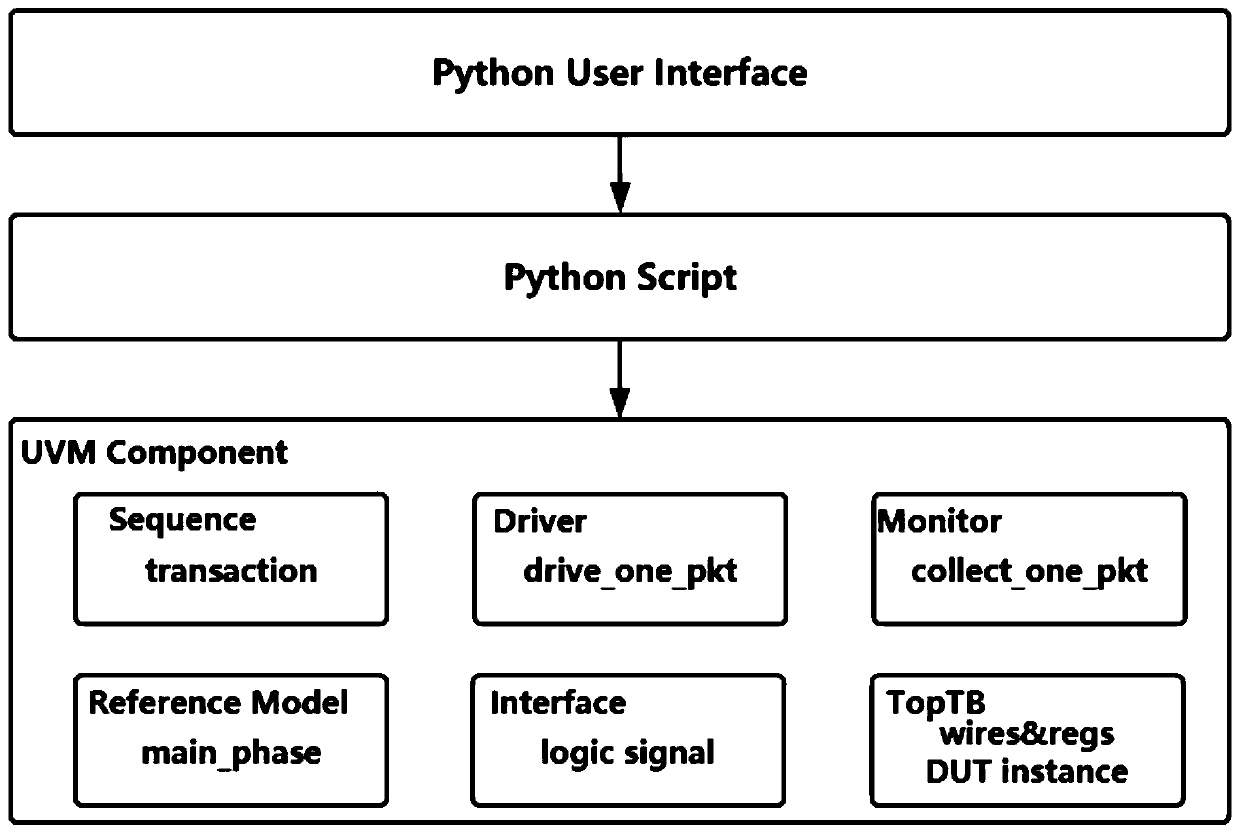

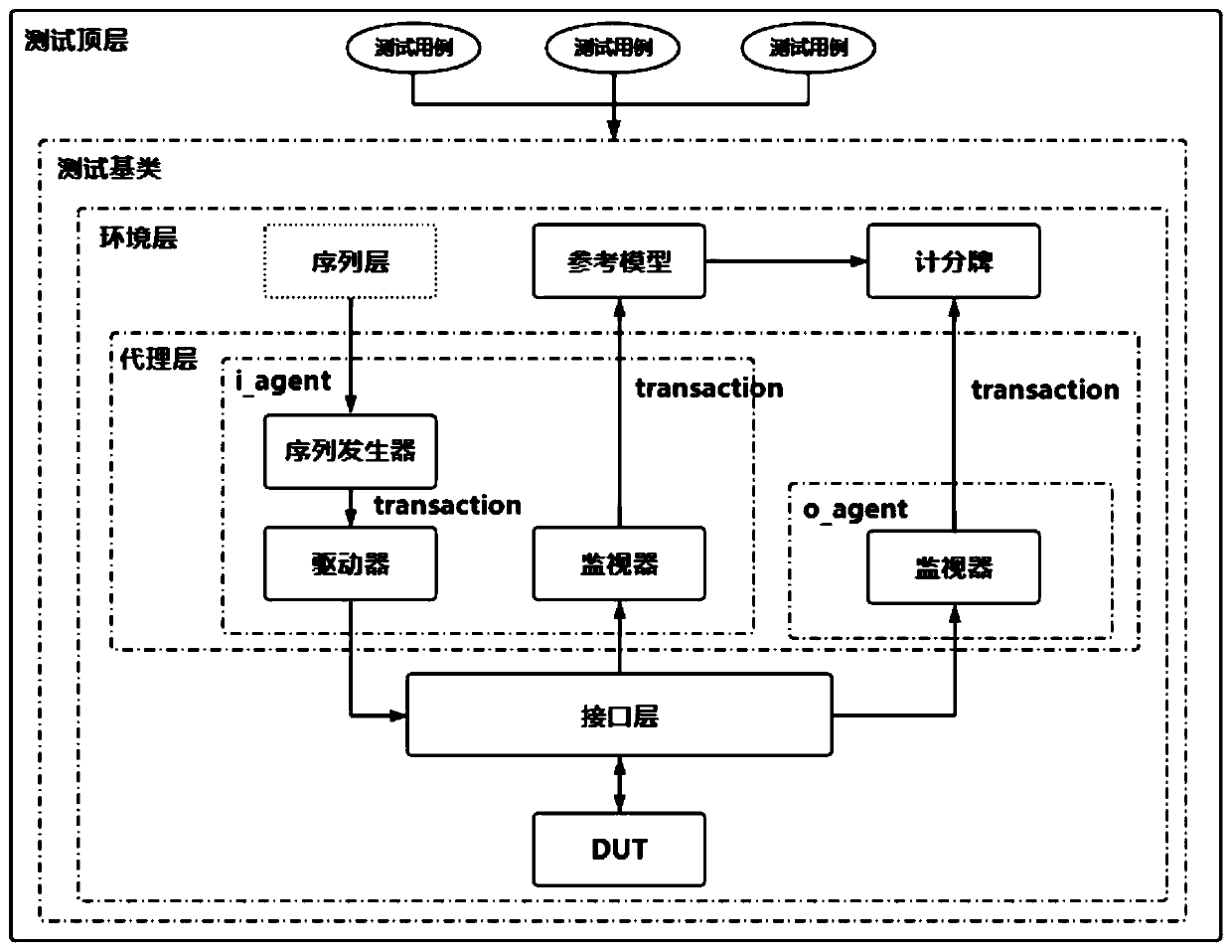

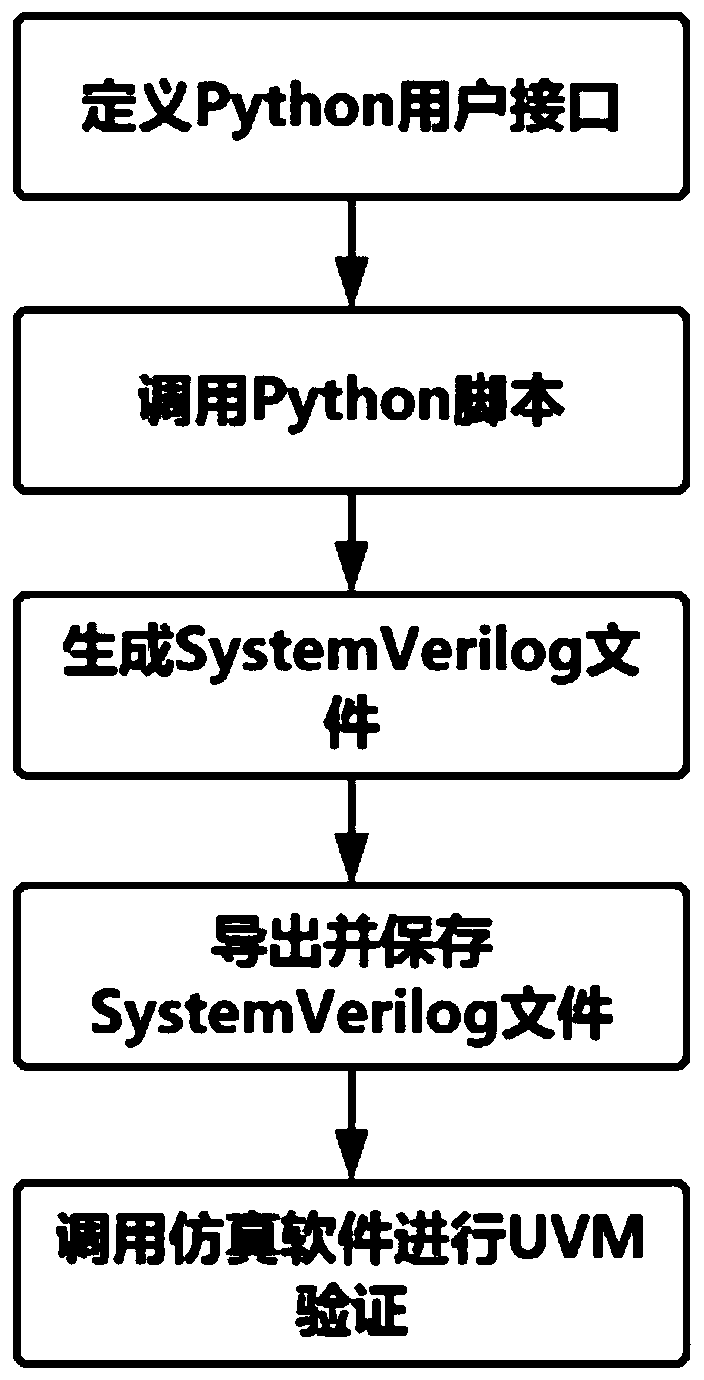

[0042] like figure 1 As shown, the EDA verification platform based on the Python language provided in this embodiment is an EDA verification platform that makes full use of the features of the Python high-level language, lowers the threshold for using the UVM verification environment, and simplifies the verification work of hardware engineers, including Python scripts and UVM verification. components.

[0043] The Python script is used to provide a user interface upward and convert the UVM verification component downward. The user interface includes data packet definition and constraints, data packet driving mode, data packet monitoring mode, and reference model function. The Python script performs string analysis and processing according to the user interface information, and replaces the specific parameters in the UVM verification component. in:

[0044] Described pac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More