Low-delay thin film transistor, array substrate and display panel

A thin-film transistor and array substrate technology, applied in the display field, can solve the problems of large resistance and capacitance delay of the display panel, large overlapping area of the drain and the gate, and affecting the display performance of the display panel, so as to improve the display performance and reduce the Positively facing the overlapping area and reducing the effect of coupling capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

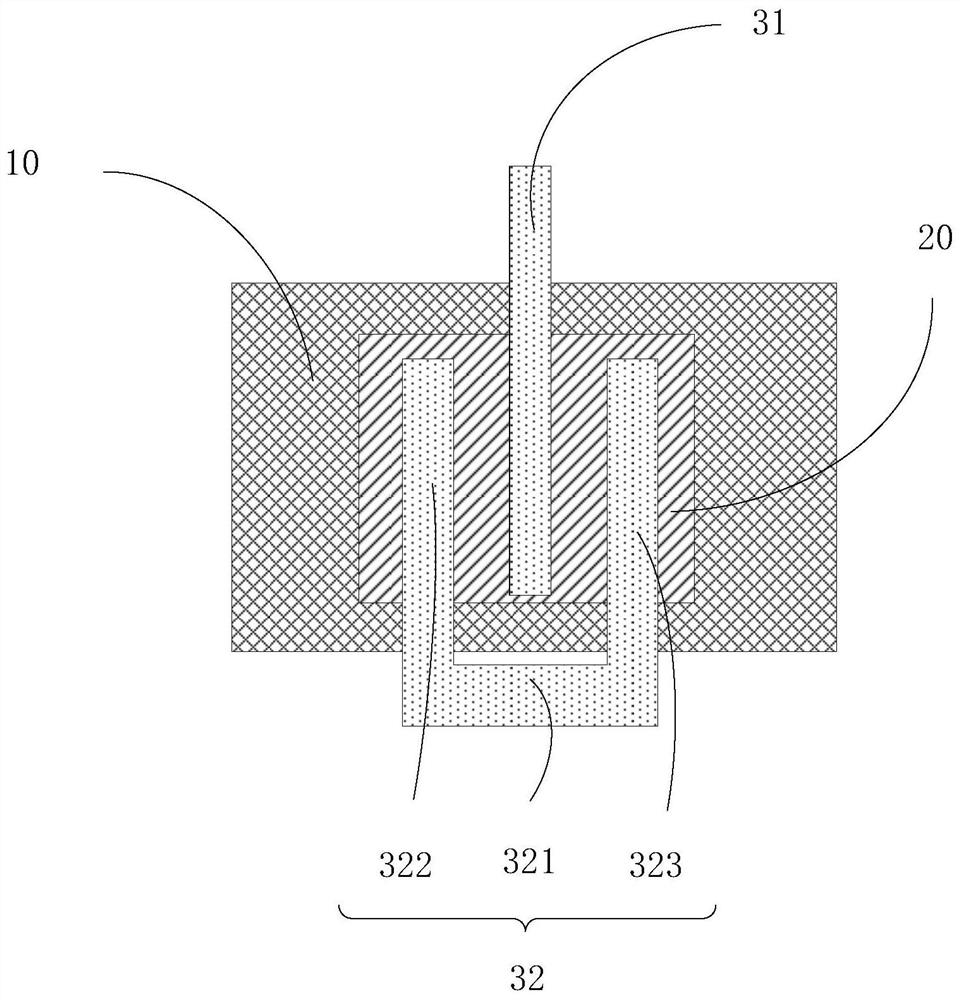

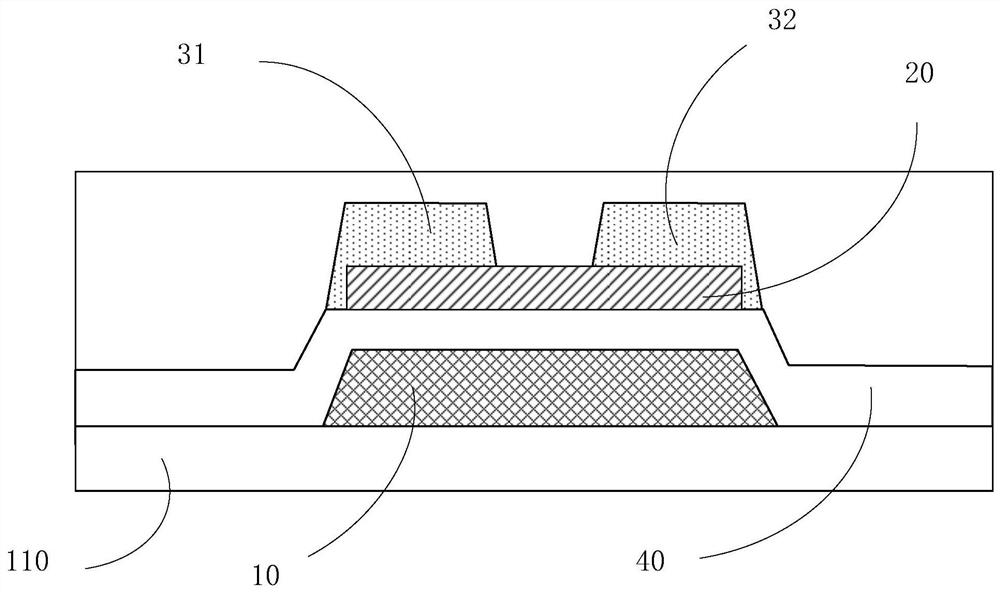

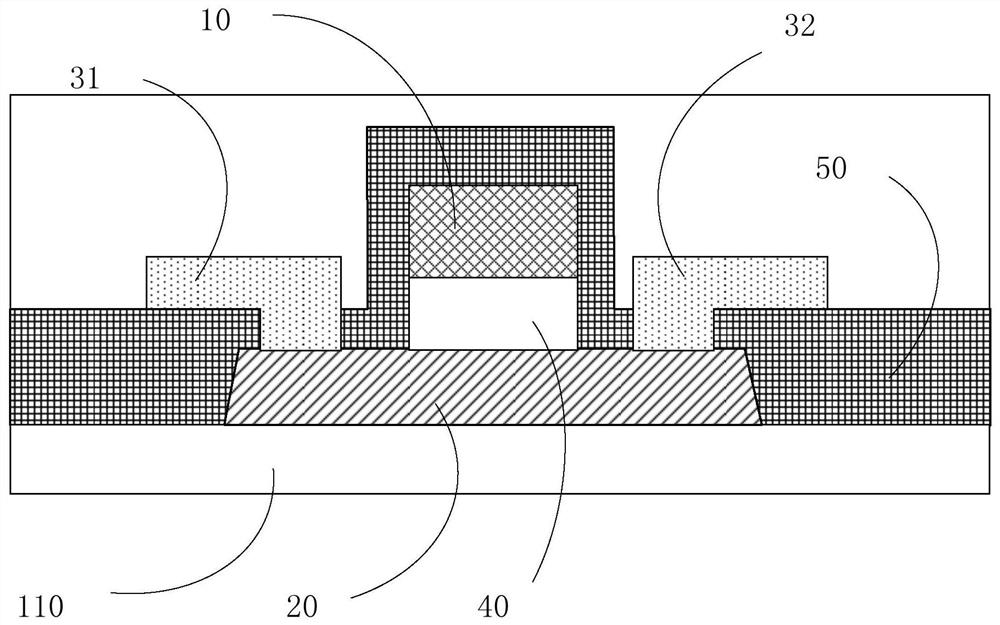

[0029] The technical solutions in the embodiments of the present application will be clearly and completely described below in conjunction with the drawings in the embodiments of the present application. Apparently, the described embodiments are only some of the embodiments of this application, not all of them. Based on the embodiments in this application, all other embodiments obtained by those skilled in the art without making creative efforts belong to the scope of protection of this application.

[0030] In the description of the present application, it should be understood that the terms "center", "longitudinal", "transverse", "length", "width", "thickness", "upper", "lower", "front", " Orientation indicated by rear, left, right, vertical, horizontal, top, bottom, inside, outside, clockwise, counterclockwise, etc. The positional relationship is based on the orientation or positional relationship shown in the drawings, which is only for the convenience of describing the a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More