Method for realizing reclosing test function of direct-current relay protection tester based on FPGA

A technology of relay protection tester and test function, which is applied in the direction of circuit breaker test, instrument, and electrical measurement. It can solve problems such as reclosing malfunction, electrical equipment hazards in the power system, and wrong action signals issued, so as to solve the problem of reclosing Brake malfunction, simple and clear operation, and the effect of reducing operation steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

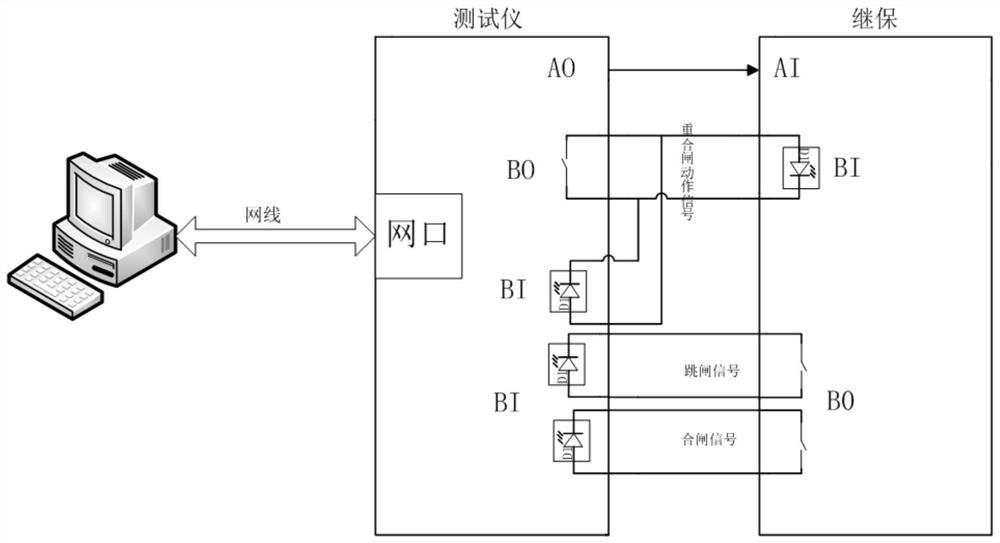

Method used

Image

Examples

Embodiment example

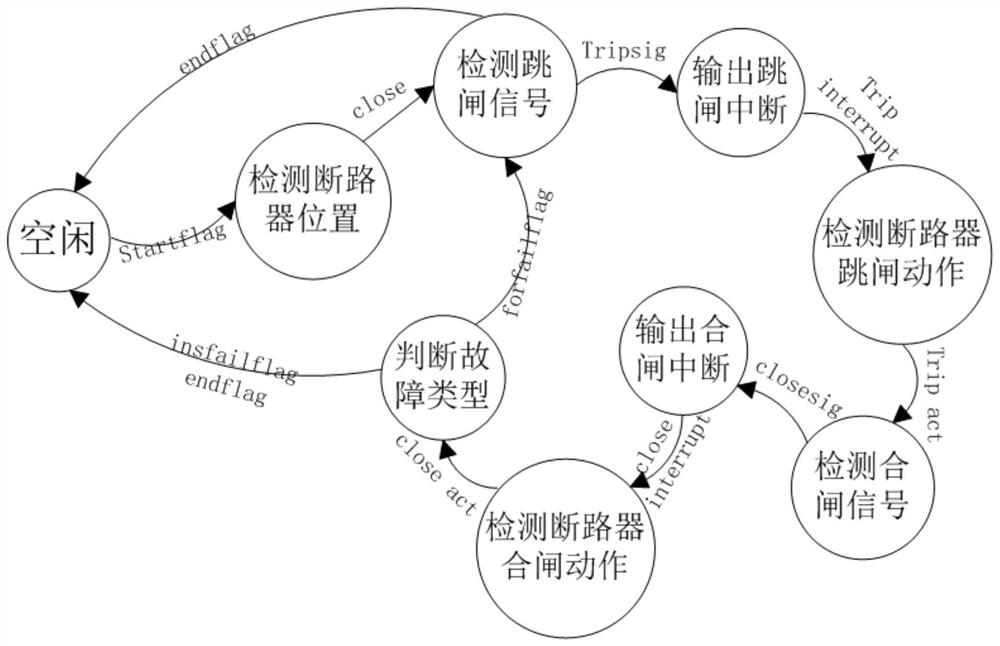

[0036] A preferred implementation example, in step S5, the judgment action for judging the fault type status includes:

[0037] a. If it is an instantaneous current fault (that is, insfailflag=1) or the experimental time limit flag is triggered (endflag=1), the state of the tester jumps to idle and waits for the next start;

[0038] b. If it is a permanent current fault (that is, forfailflag=1), the state of the tester jumps to the detection trip signal and waits for the next operation. If the test time limit flag (endflag) is detected in this state, the state of the tester jumps to idle and waits Next experiment.

[0039]In a preferred implementation case, every time the relay of the tester completes an opening or closing action, the system logic will return an action time to the CPU, and the CPU will upload it to the PC for display, thereby judging the reclosing function characteristics of the DC relay protection device Whether the action time meets the requirements.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More