Delay overcurrent protection circuit and design method thereof

A design method and overcurrent technology, applied in emergency protection circuit devices, circuit devices, emergency protection devices with automatic disconnection, etc., can solve problems such as inconvenient use, achieve wide application prospects, simple structure, and reliable design principles Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

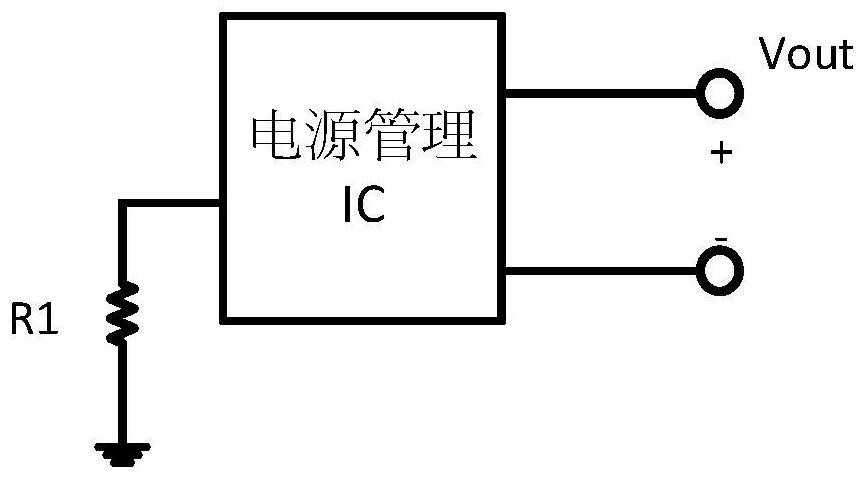

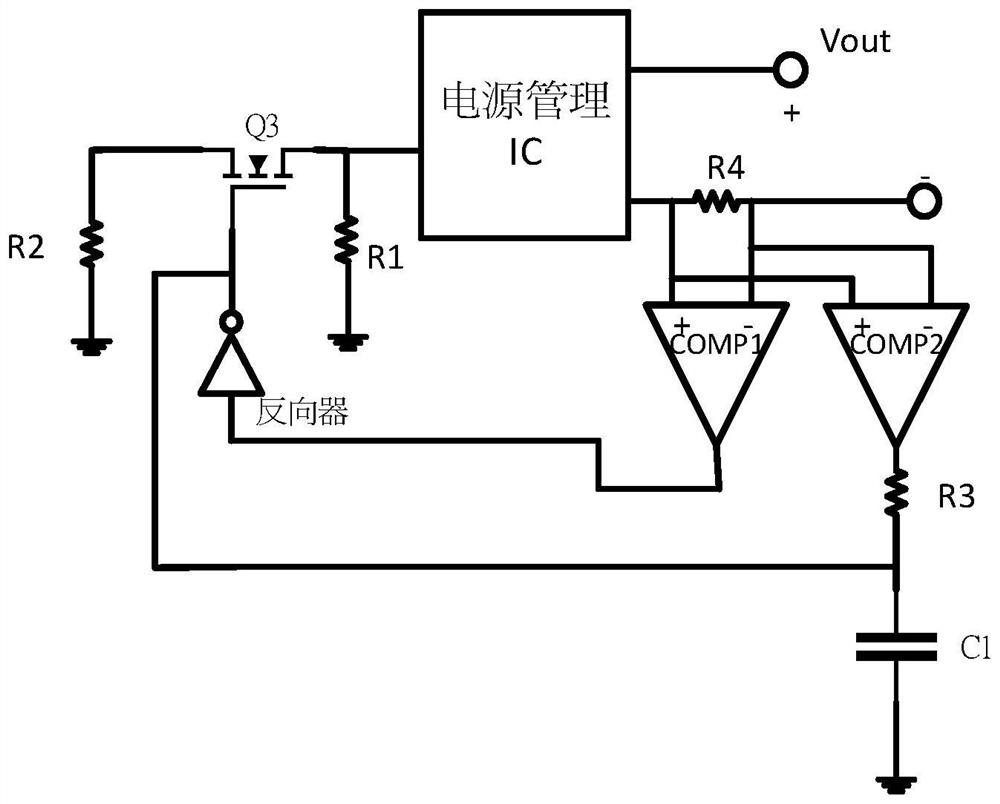

[0035] Such as image 3 As shown, this embodiment provides a delayed overcurrent protection circuit, including a power management IC and a loop connected outside the power management IC; the loop includes: a first protection resistor R1, a second protection resistor R2, n Channel MOS transistor Q3, low-impedance resistor R, second comparator COMP2, third protection resistor R3, capacitor C1, inverter, and first comparator COMP1; the first protection resistor R1 and the n-channel MOS transistor Q3 The D poles of the power management IC are respectively connected to the power management IC, and the second protection resistor R2 is connected to the S pole of the n-channel MOS transistor Q3; the negative pole of the output terminal of the power management IC is connected in series with a low-impedance resistor R4; the input of the first comparator COMP1 terminal and the input terminal of the second comparator COMP2 are respectively connected in parallel at both ends of the low-imp...

Embodiment 2

[0043] This embodiment provides a design method for delayed overcurrent protection, and the main body of the design method may be a circuit for delayed overcurrent protection.

[0044] Specifically, the design method of a delayed overcurrent protection includes:

[0045] S1, add n-channel MOS transistor Q3 and the second protection resistor R2 connected in parallel with the first protection resistor R1, and set the n-channel MOS transistor Q3 to be in the on state during initialization, which is used to reduce the overcurrent protection point in the normal working state. When increasing the overcurrent protection point in the subsequent steps, in order not to affect the overcurrent protection mechanism and keep the subsequent overcurrent protection point as it is, it is necessary to reduce the overcurrent protection point first;

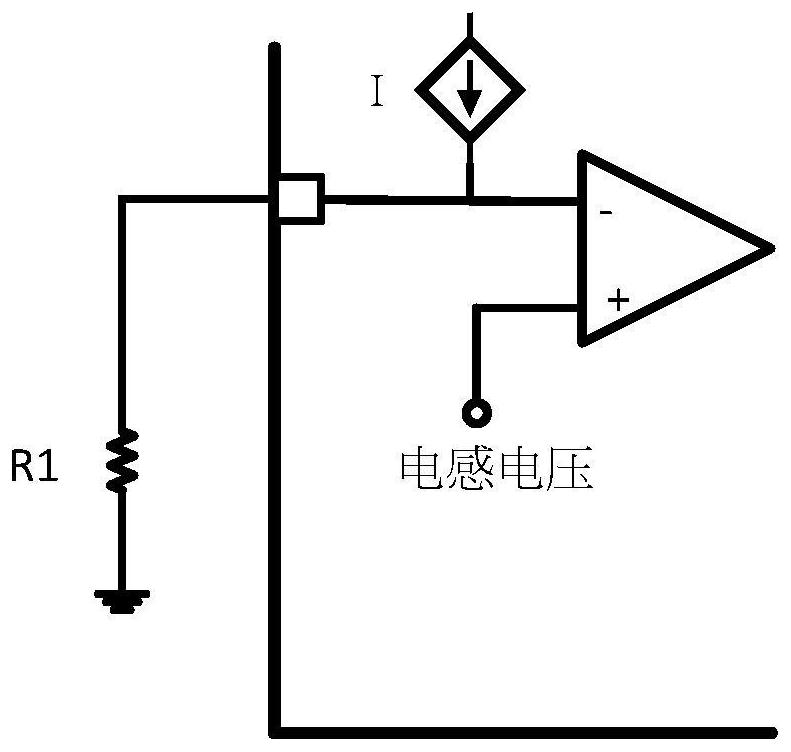

[0046] S2, increase the low-impedance resistor R4, the first comparator COMP1 and the inverter, set the first comparator COMP1 to monitor the voltag...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More