Planarization method of IGBT device

A planarization method and device technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as uniformity and adverse effects on performance of IGBT devices, large differences in wafer surface topography, etc., to avoid excessive Throwing and under-grinding, flush top surface, precise control effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

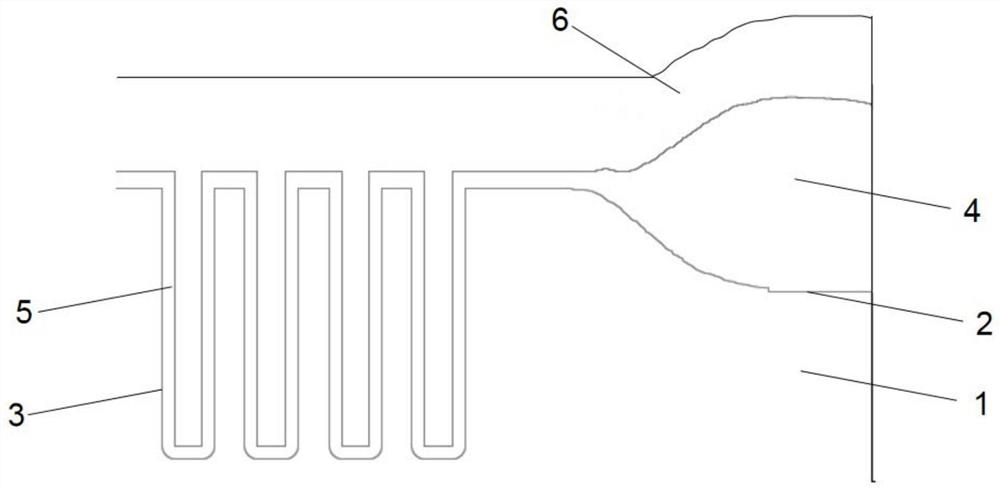

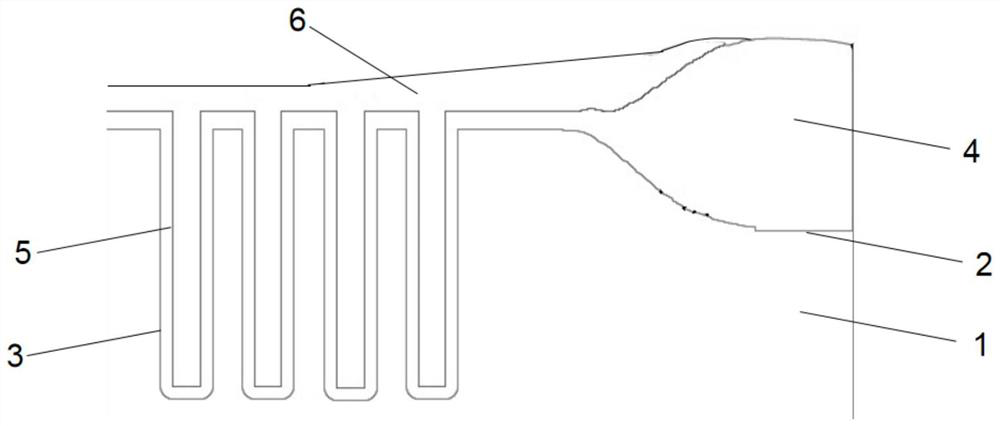

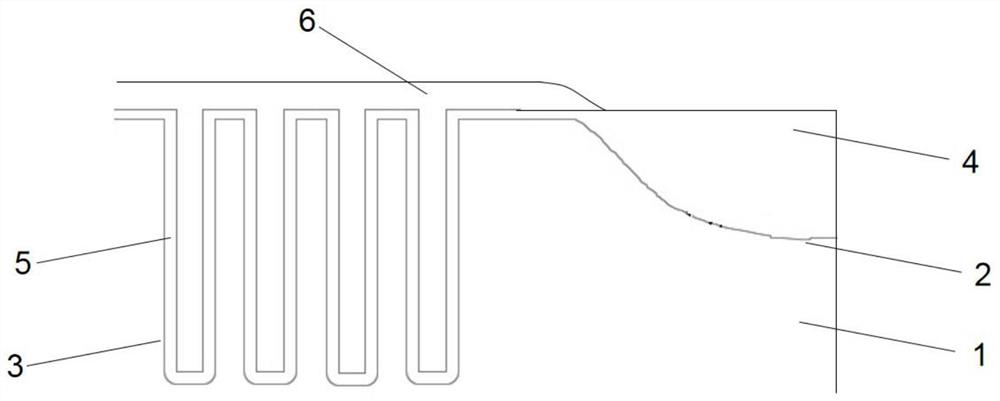

[0035] This embodiment provides a method for planarizing an IGBT device. Before the gate of the IGBT device is planarized, the structure of the gate of the IGBT device is as follows: figure 1 As shown: the substrate 1 includes a first trench 2 and several second trenches 3, and the depth of the second trench 3 is greater than that of the first trench 2, and a first insulating layer 4 is formed in the first trench 2 and the second trench The thickness of an insulating layer 4 is higher than the depth of the first trench 2, the bottom and side walls of the first trench 2 are formed with a second insulating layer 5, and the first insulating layer 4 communicates with the second insulating layer 5; the first A polysilicon layer 6 is formed on the insulating layer 4 and the second insulating layer 5, and the polysilicon layer 6 on the second insulating layer 5 extends to the outlet of the second groove 3. The material of the first insulating layer 4 and the second insulating layer 5 ...

Embodiment 2

[0042] This embodiment provides a method for planarizing an IGBT device. Before the gate of the IGBT device is planarized, the structure of the gate of the IGBT device is as follows: figure 1 As shown: the substrate 1 includes a first trench 2 and several second trenches 3, and the depth of the second trench 3 is greater than that of the first trench 2, and a first insulating layer 4 is formed in the first trench 2 and the second trench The thickness of an insulating layer 4 is higher than the depth of the first trench 2, the bottom and side walls of the first trench 2 are formed with a second insulating layer 5, and the first insulating layer 4 communicates with the second insulating layer 5; the first A polysilicon layer 6 is formed on the insulating layer 4 and the second insulating layer 5, and the polysilicon layer 6 on the second insulating layer 5 extends to the outlet of the second groove 3. The material of the first insulating layer 4 and the second insulating layer 5 ...

Embodiment 3

[0049] This embodiment provides a method for planarizing an IGBT device. Before the gate of the IGBT device is planarized, the structure of the gate of the IGBT device is as follows: figure 1 As shown: the substrate 1 includes a first trench 2 and several second trenches 3, and the depth of the second trench 3 is greater than that of the first trench 2, and a first insulating layer 4 is formed in the first trench 2 and the second trench The thickness of an insulating layer 4 is higher than the depth of the first trench 2, the bottom and side walls of the first trench 2 are formed with a second insulating layer 5, and the first insulating layer 4 communicates with the second insulating layer 5; the first A polysilicon layer 6 is formed on the insulating layer 4 and the second insulating layer 5, and the polysilicon layer 6 on the second insulating layer 5 extends to the outlet of the second groove 3. The material of the first insulating layer 4 and the second insulating layer 5 ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More