Chip pin expansion device

A technology for expanding devices and pins, which is applied in the directions of additional/integrated components of printed circuit boards, printed circuits connected with non-printed electrical components, electrical components, etc. , increase in space, etc., to achieve the effect of reducing PCB design time, saving space occupied by PCB, and meeting functional requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

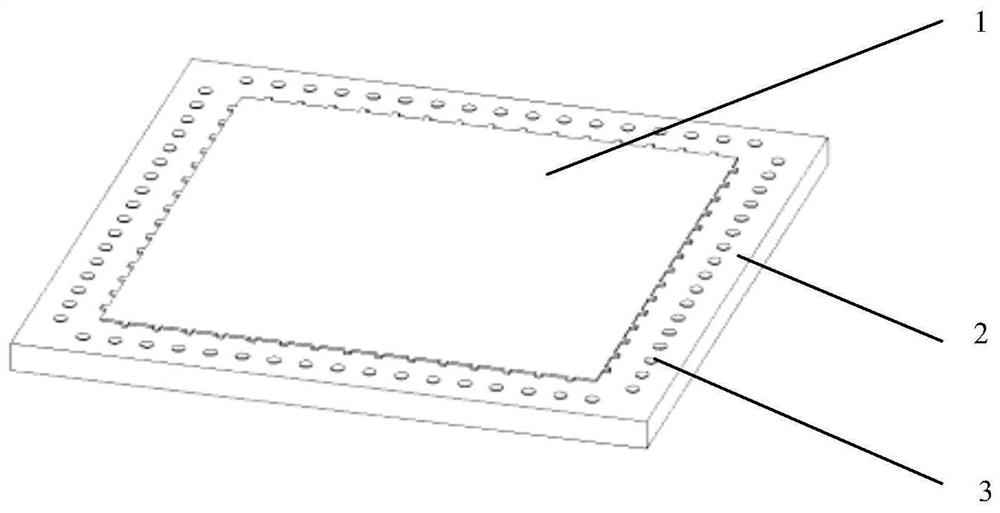

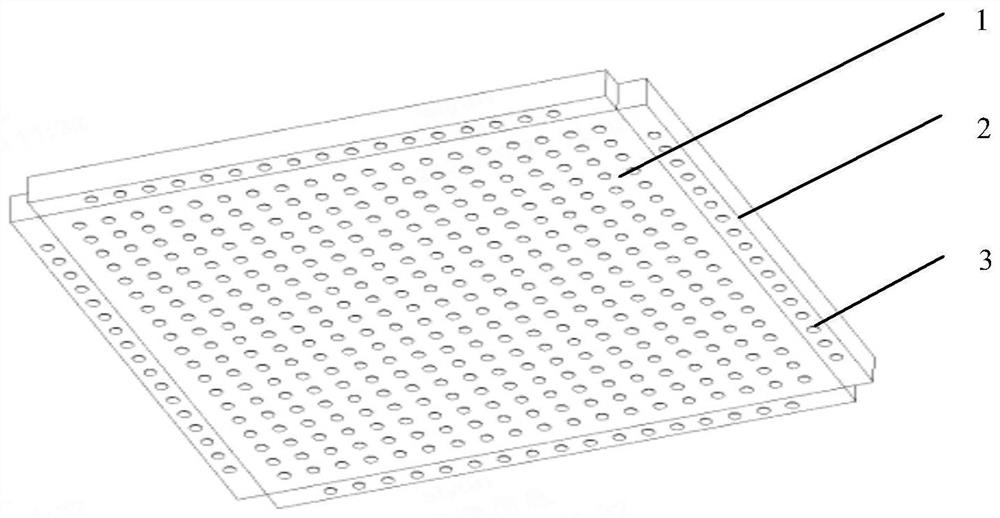

[0024] Please refer to figure 1 and figure 2 , this embodiment provides a chip pin expansion device, including:

[0025] Expansion boards 2 of various sizes and specifications are provided with a plurality of regularly arranged pins 3 on the expansion board 2 , and the arrangement distance of the pins 3 on the expansion board 2 is the same as that of the pins 3 on the main chip 1 . Therefore, the number of pins 3 on the expansion board 2 is determined by the size of the expansion board 2 .

[0026] The expansion board 2 is welded to the edge of the main chip 1 to expand the number of pins 3 of the main chip 1 . All four sides of the main chip 1 can be welded with the expansion board 2 .

[0027] If the expansion chip pin 3 is not used, there is an insulating protective mold around the pin 3 on the upper end of the chip to prevent the newly added pin 3 from being exposed.

[0028] BGA is to connect the chip pins to the PCB by soldering the solder balls on the bottom of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More