Low-delay parallel digital down-conversion method and system

A digital down-conversion and low-latency technology, applied in digital transmission systems, transmission systems, modulated carrier systems, etc., can solve problems such as resource consumption, increased delay, and performance impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

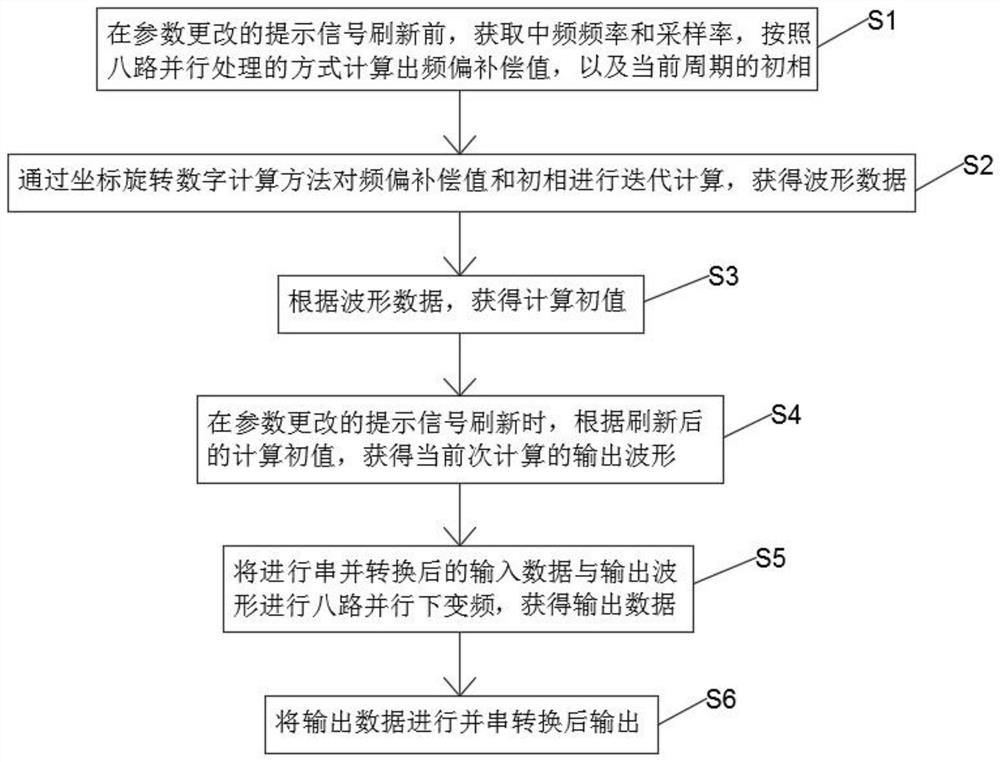

[0106] An embodiment of the present invention, such as figure 1 As shown, the present invention provides a low-latency parallel digital down-conversion method, comprising steps:

[0107] S1. Before the prompt signal (Refresh) of parameter change is refreshed, the intermediate frequency frequency and sampling rate are obtained, and the frequency offset compensation value and the initial phase of the current cycle are calculated in an eight-way parallel processing manner.

[0108] Specifically, before the prompt signal of parameter change is refreshed, the intermediate frequency frequency f0 and sampling rate fs are obtained, and the frequency offset compensation value fac and the initial phase phi of the current cycle are calculated according to the eight-way parallel processing method, fac=f0 / fs*2 ^32, phi=0.

[0109] For example, for a certain wireless communication receiver, fs=2.4G, the signal needs to be down-converted f0=300M, then fac=300 / 2400*2^32, phi=0.

[0110] S2....

Embodiment 2

[0141] An embodiment of the present invention, on the basis of Embodiment 1, after obtaining the frequency offset compensation value and the initial sine and cosine values of the initial phase, further includes: storing the initial sine and cosine values.

[0142] After obtaining the calculation initial value, it also includes: storing the calculation initial value.

[0143] Specifically, cos(fac), sin(fac), cos(phi), sin(phi), cos(8*fac), and sin(8*fac) are stored in registers 1-6 respectively, and the initial calculation value is stored in Register 7. Certainly, various registers may also be combined. For example, in this embodiment, registers 1-4 are combined into one register, registers 5-6 are combined into one register, and register 7 is a single register.

[0144] Preferably, after obtaining the output waveform of the current calculation according to the refreshed initial calculation value, the method further includes: re-refreshing the stored initial calculation val...

Embodiment 3

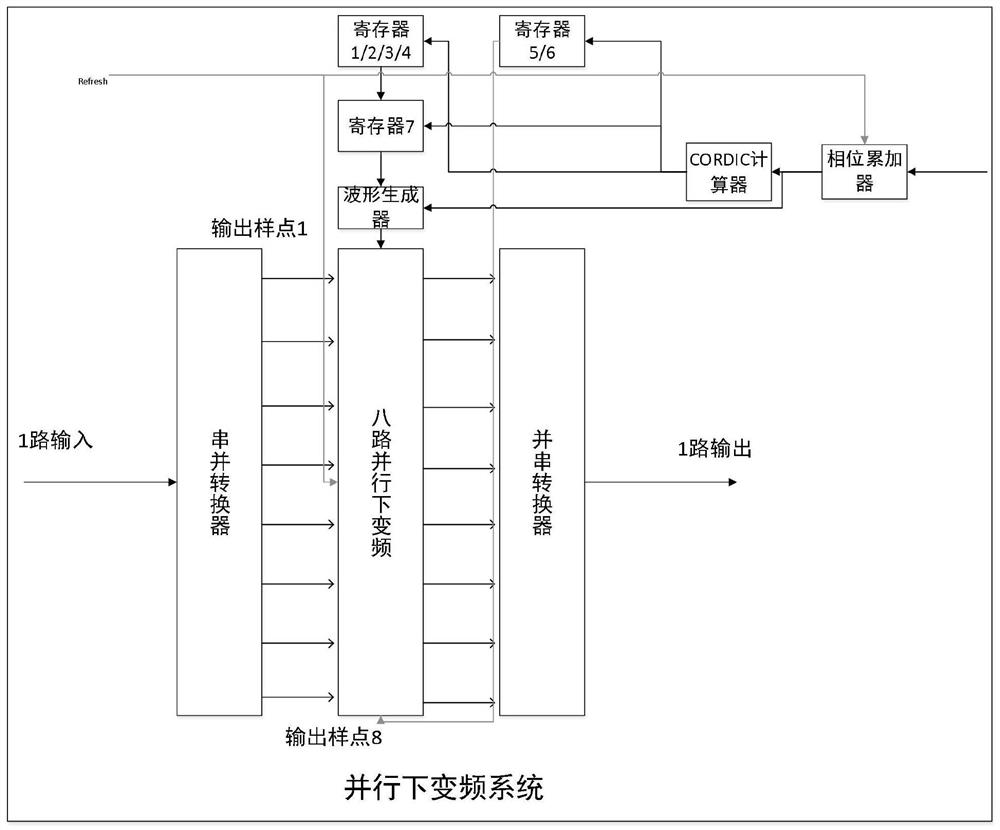

[0150] An embodiment of the present invention, such as image 3 As shown, the present invention also provides a low-latency parallel digital down-conversion system, including a phase accumulator, a CORIDC calculator, a waveform generator, a serial-to-parallel converter, an eight-way parallel down-converter and a parallel-to-serial converter.

[0151] The phase accumulator 10 is used to obtain the intermediate frequency and sampling rate before the prompt signal of parameter change is refreshed, calculate the frequency offset compensation value according to eight-way parallel processing, and configure the initial phase of the current cycle.

[0152] Specifically, before the prompt signal (Refresh) of parameter change is refreshed, the intermediate frequency frequency f0 and the sampling rate fs are obtained, and the frequency offset compensation value fac and the initial phase phi of the current cycle are calculated according to the eight-way parallel processing method, fac=f0 / ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More