Multi-chip mounting structure and preparation method thereof

A multi-chip and placement technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as difficulty in effectively realizing on-demand filling, difficulty in filling packaging structures, and large influence between steps. Improve process efficiency and product yield, reduce filling difficulty, and solve the effect of filling bubbles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

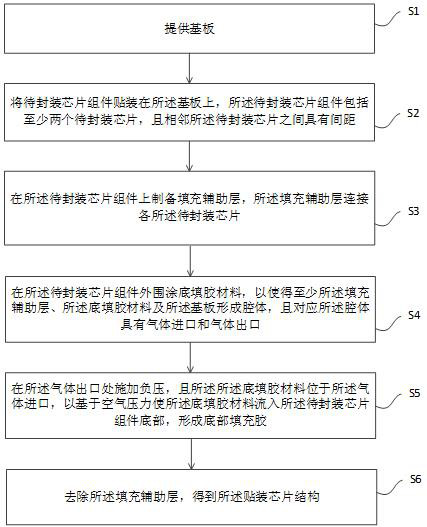

[0038] Such as figure 1 As shown, the present invention provides a kind of preparation method of multi-chip mounting structure, and described preparation method comprises the following steps:

[0039] S1, providing the substrate;

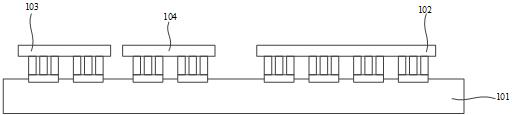

[0040] S2, attaching a chip assembly to be packaged on the substrate, the chip assembly to be packaged includes at least two chips to be packaged, and there is a distance between adjacent chips to be packaged;

[0041] S3, preparing an auxiliary filling layer on the chip assembly to be packaged, the auxiliary filling layer connecting each of the chips to be packaged;

[0042] S4, coating an underfill material on the periphery of the chip component to be packaged, so that at least the filling auxiliary layer, the underfill material, and the substrate form a cavity, and corresponding to the cavity, there is a gas inlet and a gas exit;

[0043] S5, applying negative pressure at the gas outlet, and correspondingly coating the underfill material at th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com