Device and method for calibrating offset of comparator in high-speed ADC

A technology for calibrating devices and comparators, applied in analog/digital conversion calibration/testing, analog-to-digital converters, etc., can solve problems such as large input offset of comparators, achieve small input parasitics, reduce offsets, and improve effect of speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

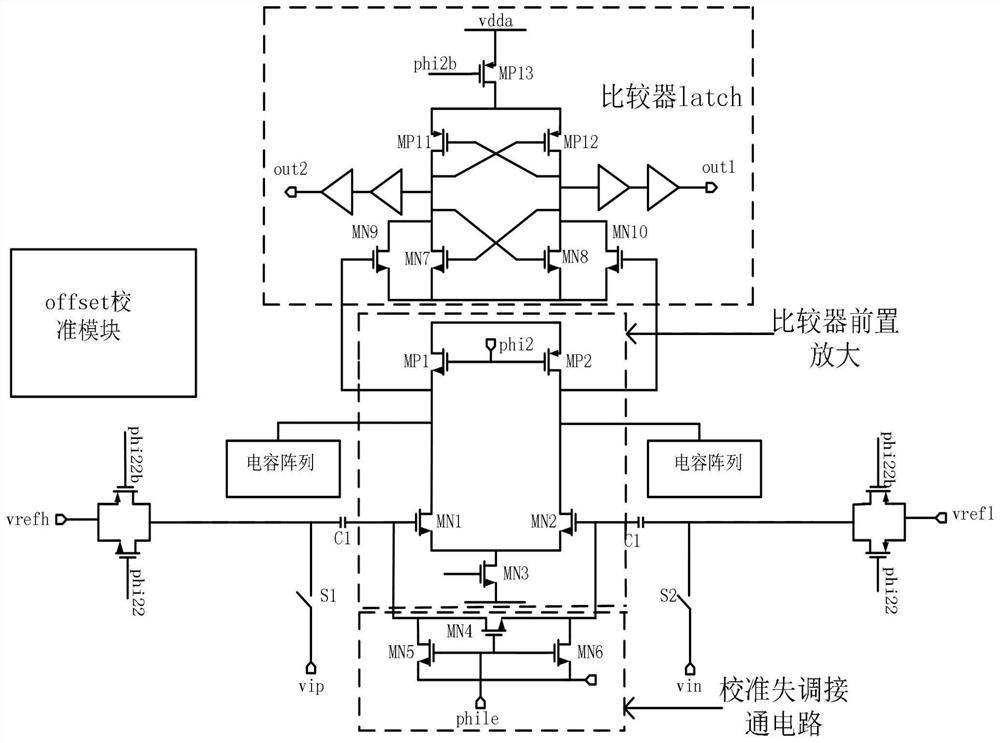

Embodiment 1

[0033] This embodiment provides a calibration device for comparator offset in a high-speed ADC. The high-speed ADC described in this embodiment is a high-speed pipelineADC, and the comparator is a dynamic comparator. The speed of this dynamic comparator is relative to that of a static comparator. Much faster. In high-speed ADCs, the transistor size of the entire comparator is very small due to the high speed requirements. The input terminals of the comparator (the tube MN1 and the tube MN2 ) are the minimum size of the corresponding process, so there will be a very large offset voltage at the input terminal. The dynamic comparator used in this high-speed ADC cannot store the offset voltage like the method of storing the offset voltage in the general ADC (just insert the corresponding offset storage capacitor in series in the preamplifier circuit), the size of the capacitor, the capacitance of the capacitor How it is used becomes very critical and can easily affect the speed o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com