Overlay test structure, preparation method thereof and overlay test method

A test structure and test method technology, applied in the field of semiconductors, can solve the problem that the boundary signal cannot measure the overlay accuracy normally, and achieve the effects of cost saving, wide application prospect, and simple process optimization.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

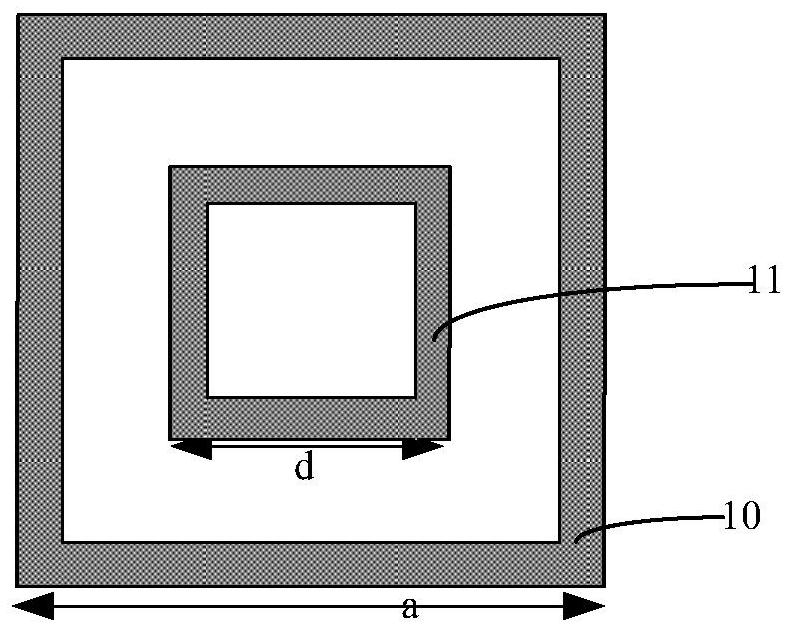

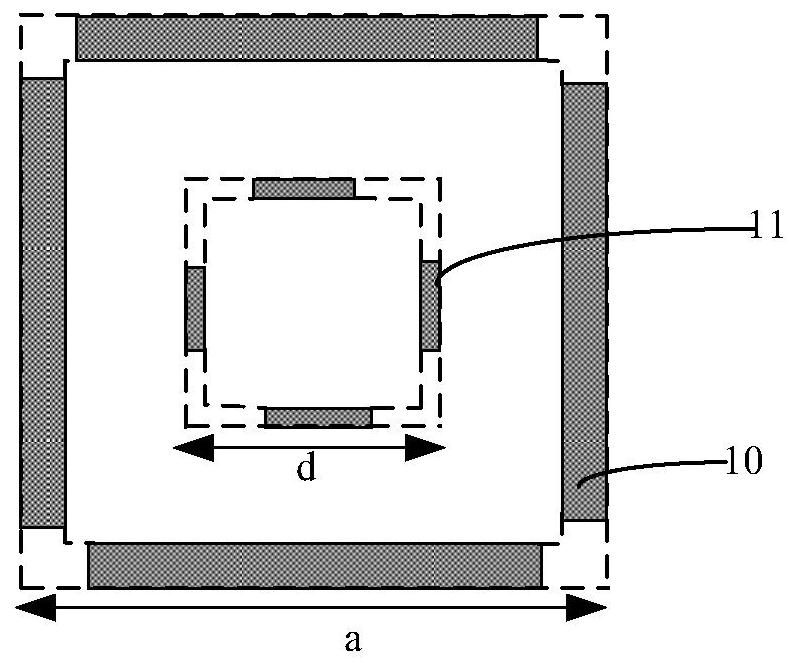

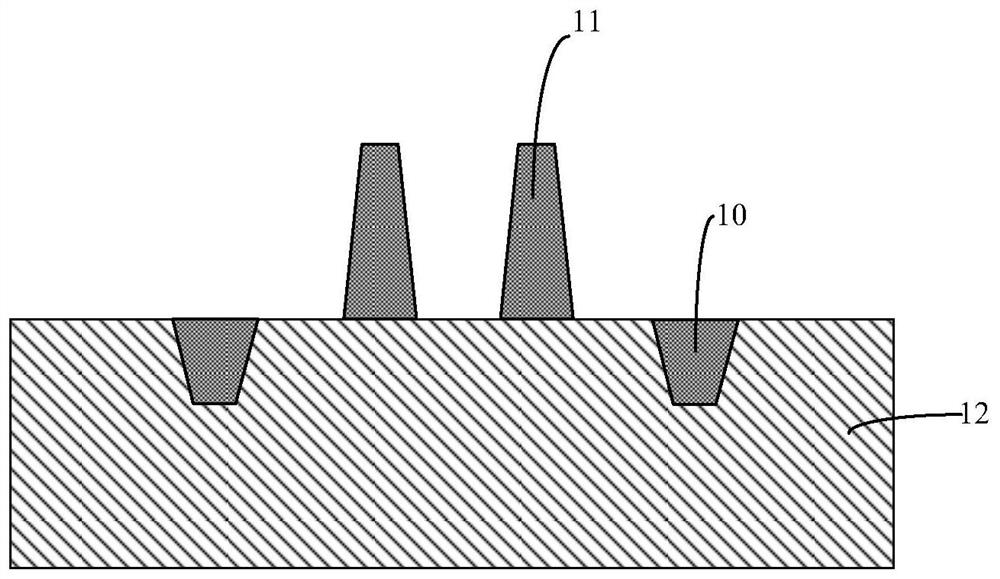

[0077] Attached below Figures 1A-1B ,as well as figure 2 with Figure 4 An overlay alignment standard of the present invention is described in detail. in Figures 1A-1B It shows a schematic top view of an overlay test structure in an embodiment of the present invention; figure 2 It shows a schematic cross-sectional view of an overlay test structure in an embodiment of the present invention; Figure 4 A flowchart showing the steps of a method for preparing an overlay test structure according to an embodiment of the present invention.

[0078] Such as figure 2 As shown, in this embodiment, the overlay test structure includes:

[0079] base layer 12;

[0080] a first layer of overlay marks 10 formed in the base layer 12;

[0081] The second layer of overlay marks 11 is formed on the first film layer on the base layer, the first layer of overlay marks 10 and the second layer of overlay marks 11 are hollow ring frames and the first layer The size of any border in the rin...

Embodiment 2

[0124] Attached below Figures 3A-3C ,as well as Figure 5 An overlay test structure of the present invention is described in detail. Figures 3A-3C It shows a schematic cross-sectional view of each device during the preparation process of an overlay test structure in an embodiment of the present invention; Figure 5 A flowchart showing the steps of a method for fabricating a test structure according to another embodiment of the present invention.

[0125] Such as Figure 3C As shown, in this embodiment, the overlay test structure includes:

[0126] base layer 12;

[0127] The first layer of overlay marks 10, formed in the first film layer on the base layer;

[0128] The second overlay mark 11 is formed on the first film layer on the base layer;

[0129] Wherein, the first-layer overlay mark 10 and the second-layer overlay mark 11 are hollow ring frames, and the second-layer overlay mark 11 is arranged on the first-layer overlay mark on the projection of the horizontal p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com