GPDSP assembly transplantation optimization method and system based on countdown buffering

An optimization method and assembly technology, applied in the direction of computing, code compilation, software engineering design, etc., can solve the problems of assembly code development and optimization difficulty, waste of human and financial resources, code is not portable, etc., to achieve good code performance and hardware. The effect of resource utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

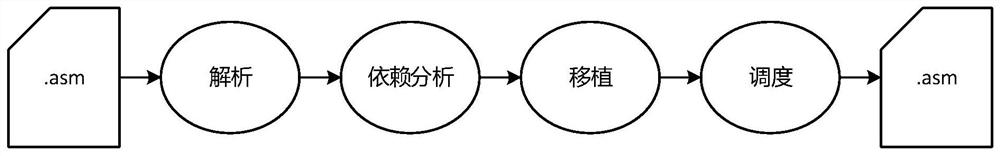

[0031] Such as figure 1 As shown, the GPDSP assembly transplantation optimization method based on the countdown buffer in this embodiment includes:

[0032] 1) For the GPDSP assembly code to be transplanted ( figure 1 Indicated by the suffix ".asm"), and analyze the dependencies based on the countdown buffer pool, analyze the sequence of instruction streams and the dependencies between instructions, and build a directed acyclic graph of instruction dependencies;

[0033] 2) Analyze the difference in instruction set information before and after transplantation, correct the instructions in the assembly code according to the difference in instruction set information before and after transplantation, and map it to the instruction information under the new architecture;

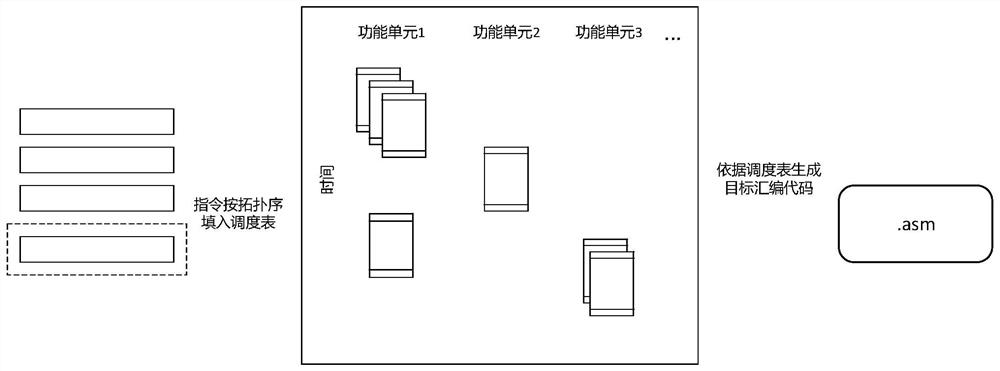

[0034] 3) Based on the directed acyclic graph of instruction dependence, the instruction information mapped to the new architecture is transplanted. Based on the long instruction priority list scheduling algorith...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More