Network layer communication method between a central processing unit (CPU) and field programmable gate array (FPGA)

A communication method and network layer technology, applied in the direction of electrical components, transmission systems, etc., can solve problems such as the end of transmission that cannot be solved

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

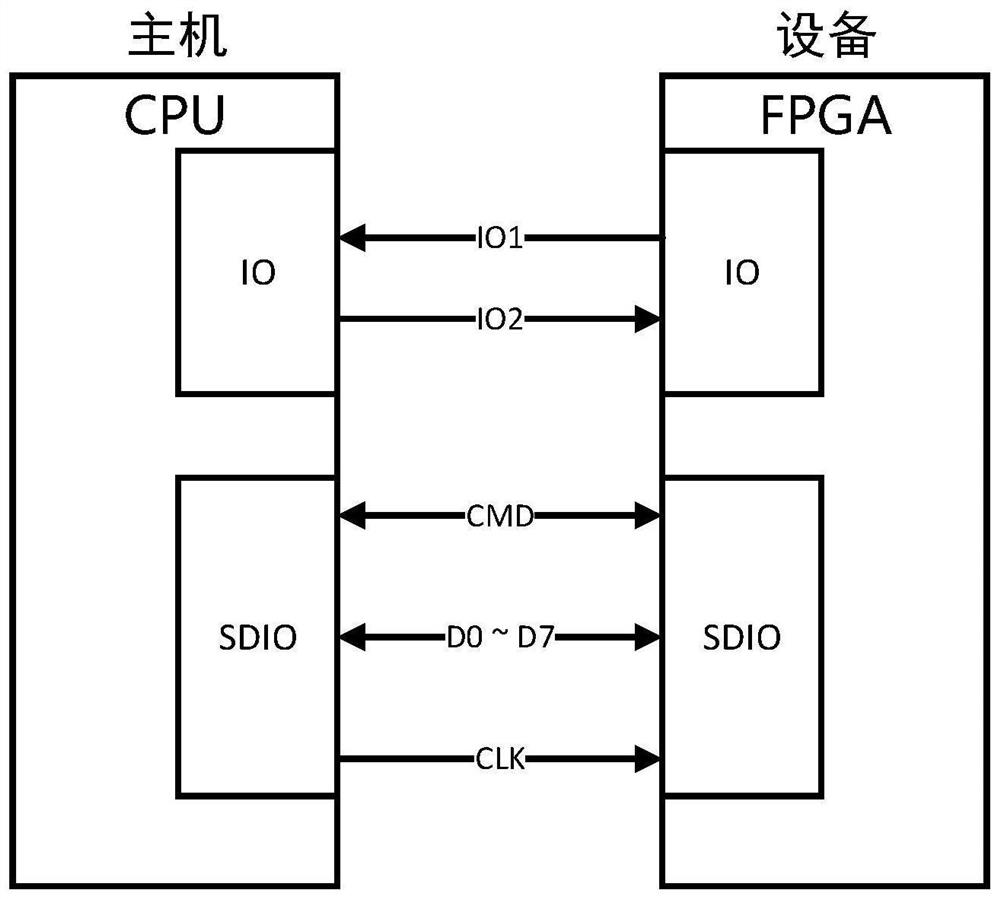

[0057] A kind of network layer communication method between CPU and FPGA of the present invention, see figure 1 As shown, it is applied to the communication between CPU and FPGA. In the present invention, CPU acts as a host, and FPGA acts as a device for data communication. Either the host CPU or the device FPGA can initiate communication for data transmission.

[0058] Such as figure 1 As shown, the communication interface between the host CPU and the device FPGA is defined as follows:

[0059] 1) IO1: used for the device FPGA to wake up the host CPU line;

[0060] 2) IO2: used for the host CPU to wake up the device FPGA line;

[0061] 3) CMD: command control line, the host CPU sends commands to the device FPGA through this line;

[0062] 4) D0~D7: data lines, used to transmit data;

[0063] 5) CLK: Clock signal line, used to send the clock signal from the host CPU to the device FPGA.

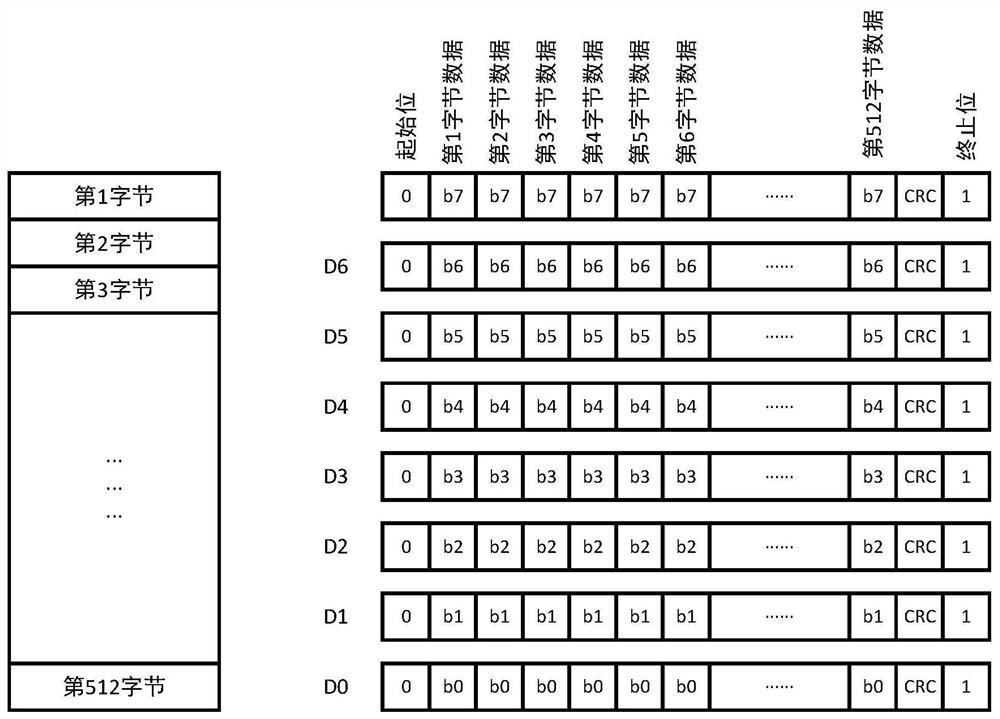

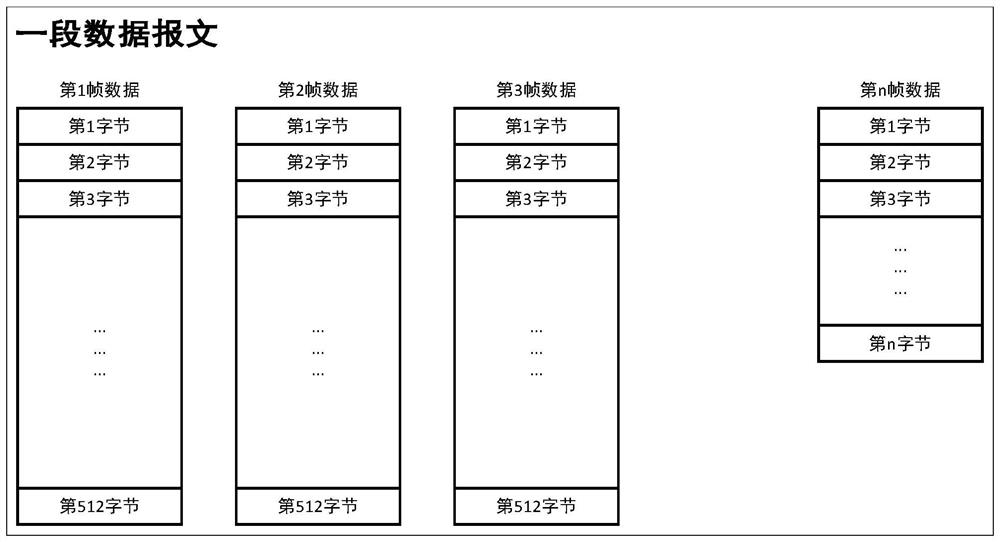

[0064] Such as figure 2 As shown, the interactive data defining the host CPU and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com