Hierarchical SoC test scheme based on IEEE1149 and IEEE1500 standards

A technology of IEEE1149.1 and IEEE1149, which is applied in the field of hierarchical SoC test solutions, can solve problems such as the difficulty of obtaining IP core detailed information, and achieve the effects of promoting test reuse, high-efficiency design solutions, and reducing test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

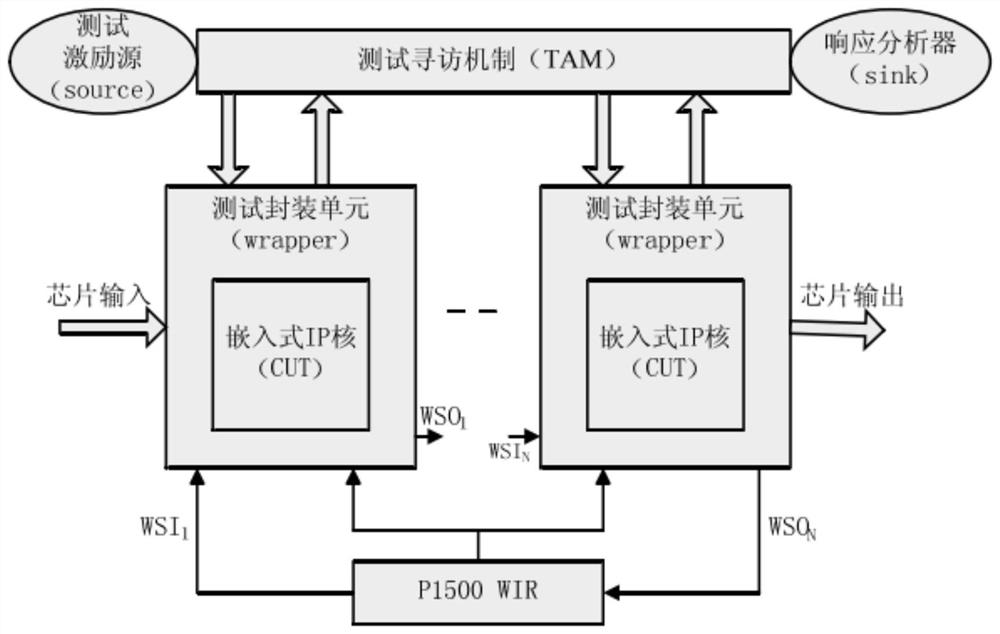

[0023] Such as figure 1 As shown; the IEEE1500 standard protocol divides the SoC test architecture into three parts: the test package unit (Wrapper), the chip-level test access controller and the test access mechanism (Test Access Mechanism, referred to as TAM);

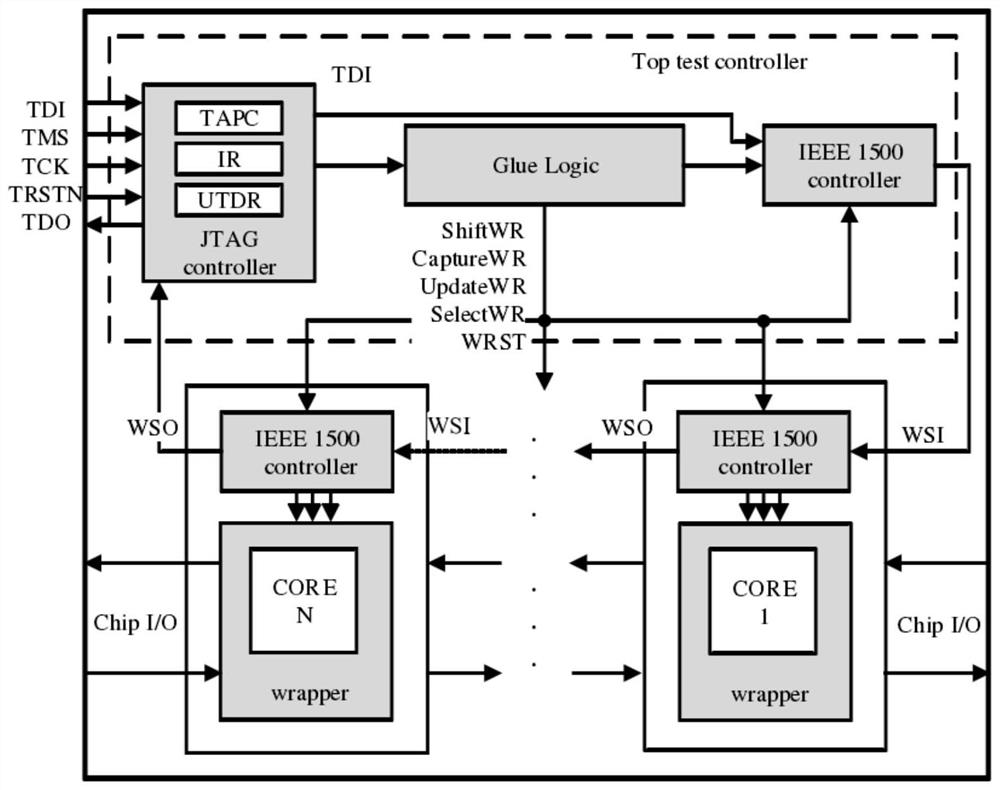

[0024] Such as figure 2 As shown; the IEEE1500 standard protocol is one of the most popular standards in the industry that can implement embedded core testing, and it can effectively complete the testin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More