Scalable integrated circuit with synaptic electronics and CMOS integrated memristors

A circuit and synapse technology, applied in the field of neural networks, which can solve the problem that the connection is not programmable.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In the following description, numerous specific details are set forth in order to clearly describe various specific embodiments disclosed herein. However, it will be understood by those skilled in the art that the present invention may be practiced without all of the specific details discussed below. In other instances, well-known features have not been described in order not to obscure the invention.

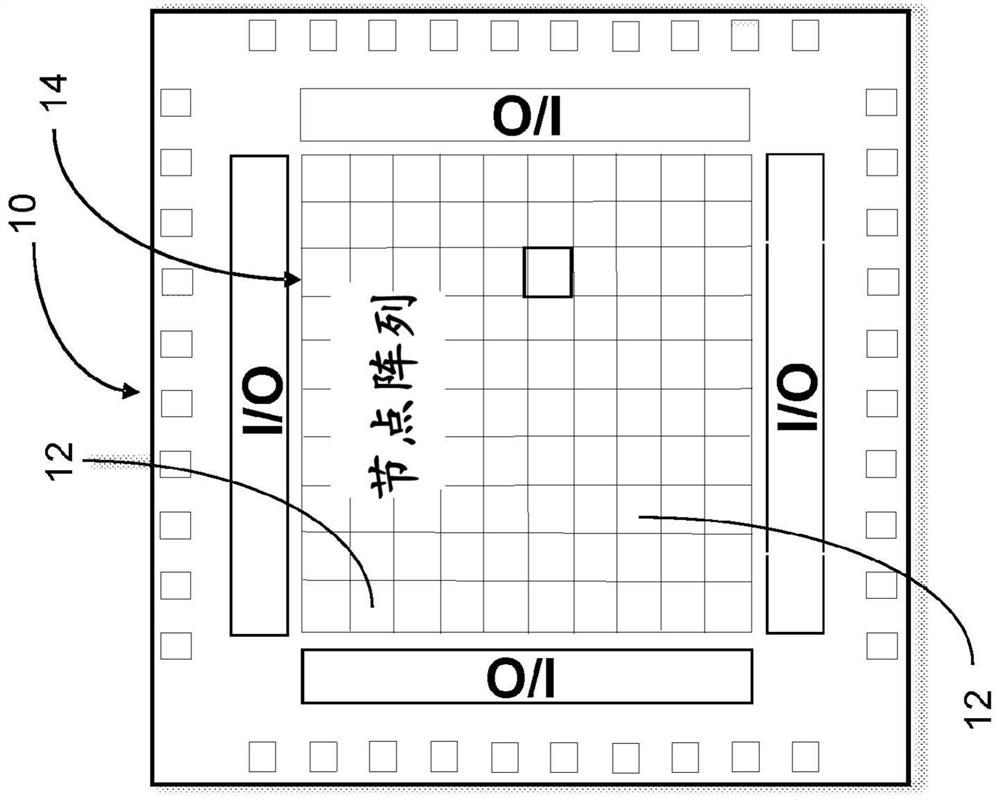

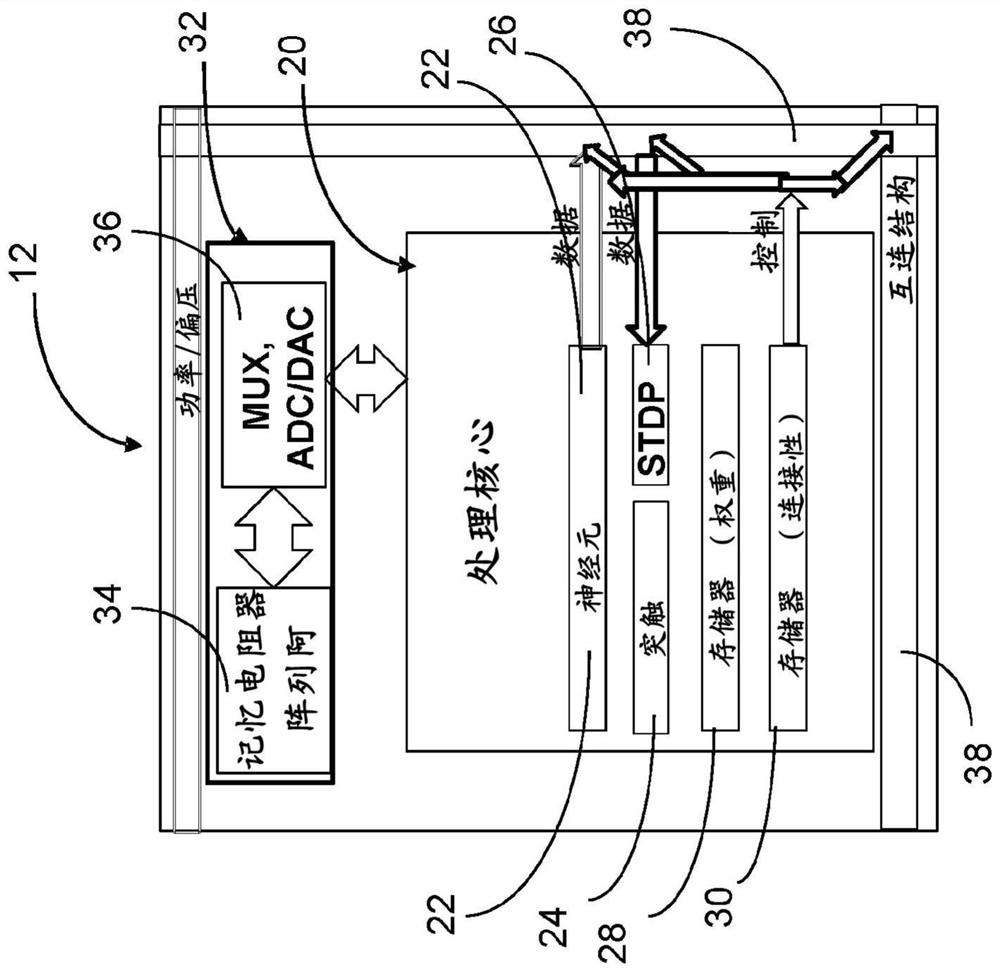

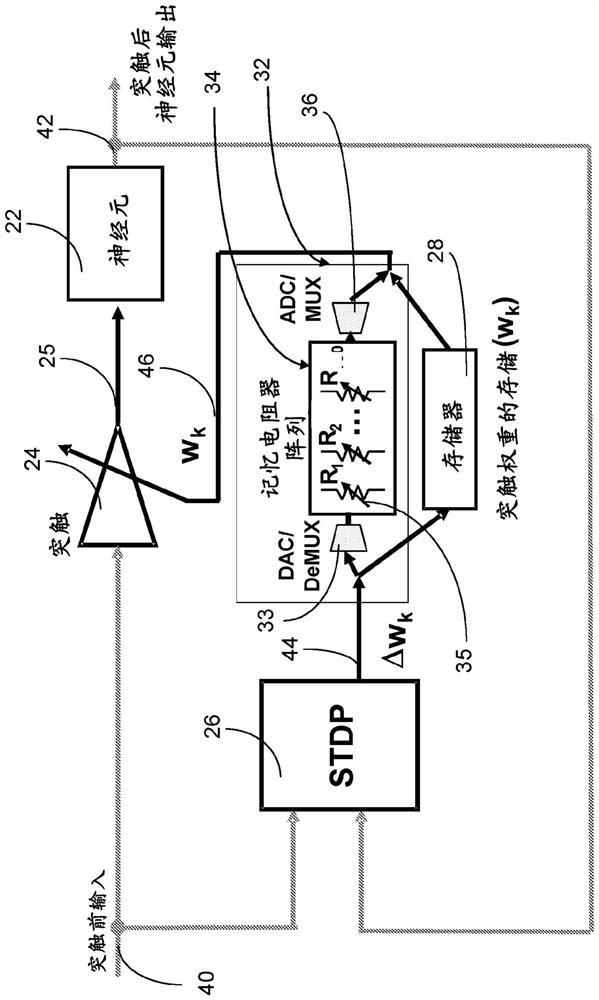

[0033] In this disclosure, scalable neuromorphic integrated circuits with spiking neurons, synapses, and spike timing-dependent plasticity (STDP) are described, where connections between neurons and synapses are not fixed but can be programmed of. Synapses, STDP circuits, and interconnection paths between neurons and synapses are time multiplexed. The integrated circuit includes memory that stores synaptic weights and interconnect routing information. Circuitry includes CMOS circuitry to implement high-density memristor memory and write and read memristors.

[0034] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More