Method for inhibiting writing fluctuation of ferroelectric transistor FeFET

A ferroelectric transistor and write operation technology, which is applied to digital memory information, instruments, biological neural network models, etc., can solve problems such as the disappearance of storage windows, the decrease of neural network accuracy, and the sacrifice of dynamic range of units, so as to improve accuracy and reduce conductance Fluctuation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further elaborated below through specific embodiments in conjunction with the accompanying drawings.

[0020] This embodiment uses Hf 0.5 Zr 0.5 o 2 The ferroelectric transistor FeFET of ferroelectric material, at this time, the spontaneous polarization of ferroelectric material will induce additional charges on the gate oxide layer of MOSFET, resulting in a change in the channel conductance of the device. The charge induced by the ferroelectric polarization charge on the gate oxide layer of the MOSFET can also be equivalent to an additional gate voltage, which can be reflected on the entire FeFET as a change in the channel conductance of the device.

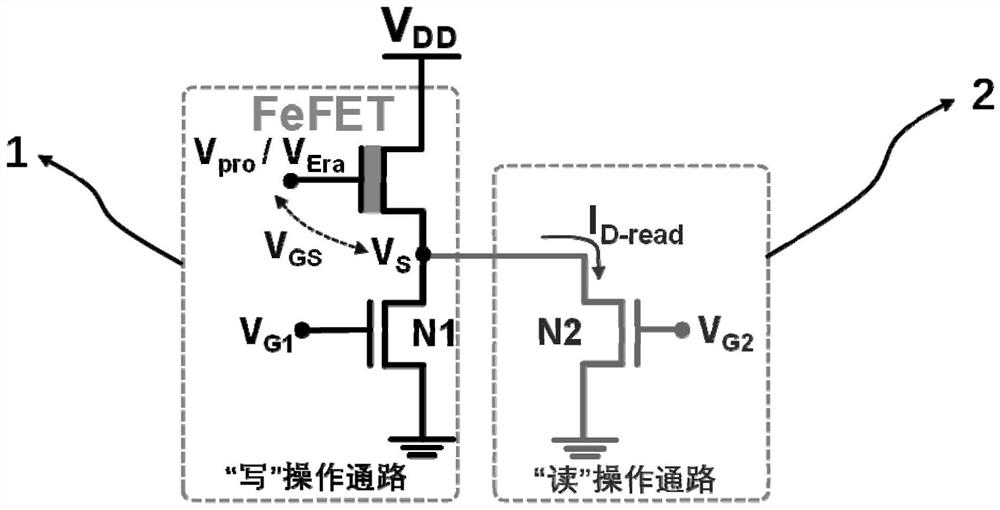

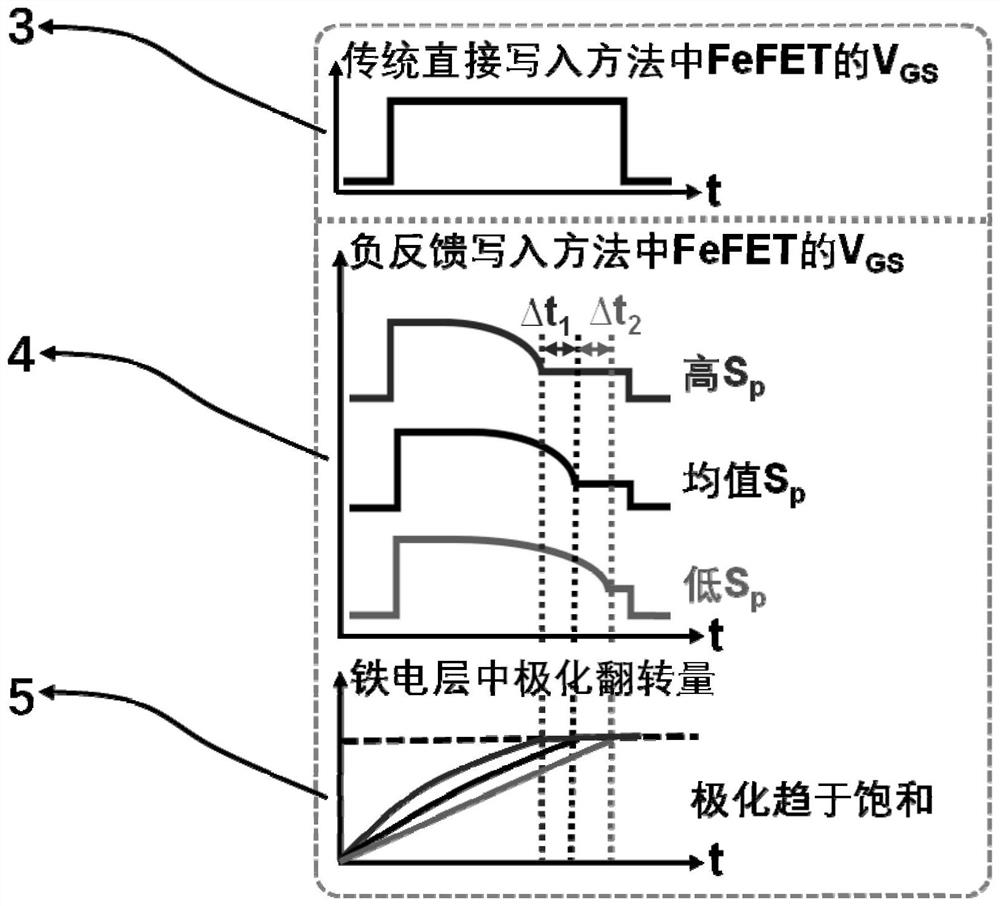

[0021] Such as figure 1 As shown, the present embodiment is a method for suppressing the write fluctuation of the ferroelectric transistor FeFET, including the ferroelectric transistor FeFET, the NMOS (N1) of the write operation path, and the NMOS (N2) of the read operation path; wherein, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More