Method for realizing excitation and inhibition functions of synapses

A synaptic and exciting technology, applied in the synaptic field of neuromorphic computing, can solve problems such as changes in device channel conductance, and achieve the effect of plasticity and maintaining characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The present invention will be further elaborated below through specific embodiments in conjunction with the accompanying drawings.

[0016] This embodiment uses Hf 0.5 Zr 0.5 o 2 The ferroelectric transistor FeFET of ferroelectric material, at this time, the spontaneous polarization of ferroelectric material will induce additional charges on the gate oxide layer of PMOS, resulting in a change in the channel conductance of the device. The charge induced by the ferroelectric polarization charge on the PMOS gate oxide layer can also be equivalent to an additional gate voltage, which can be reflected on the entire FeFET as a change in the channel conductance of the device.

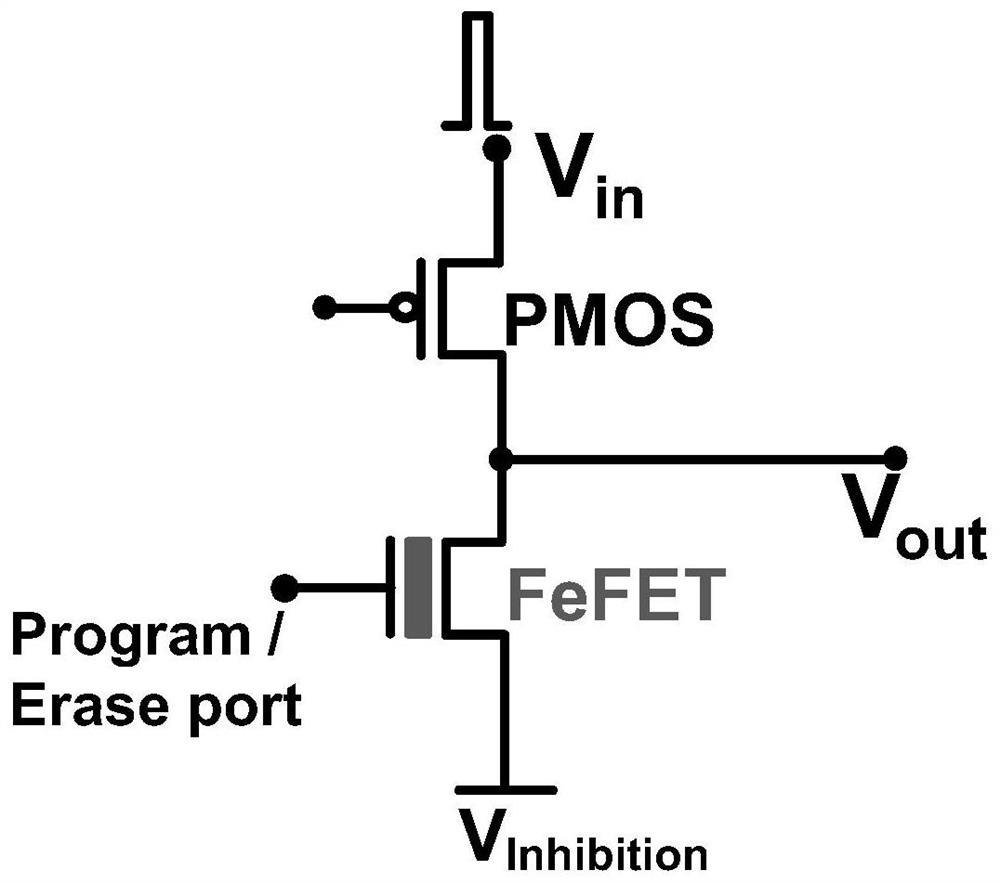

[0017] Such as figure 1 As shown, the present embodiment is based on ferroelectric transistors with excitatory and inhibitory synaptic circuits, including ferroelectric transistors FeFET and PMOS; wherein, FeFET is used to realize the plasticity and retention characteristics of synapses, programming ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More