Packaging method and packaging structure of fan-out stacked chip

A technology of packaging structure and packaging method, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of ultra-thin substrate production difficulty, difficulty, and unsustainable reduction, and achieve ultra-thin multi-layer Effects of high-density stacked packaging, reduced package size, and increased density interconnection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to enable those skilled in the art to better understand the technical solutions of the present invention, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

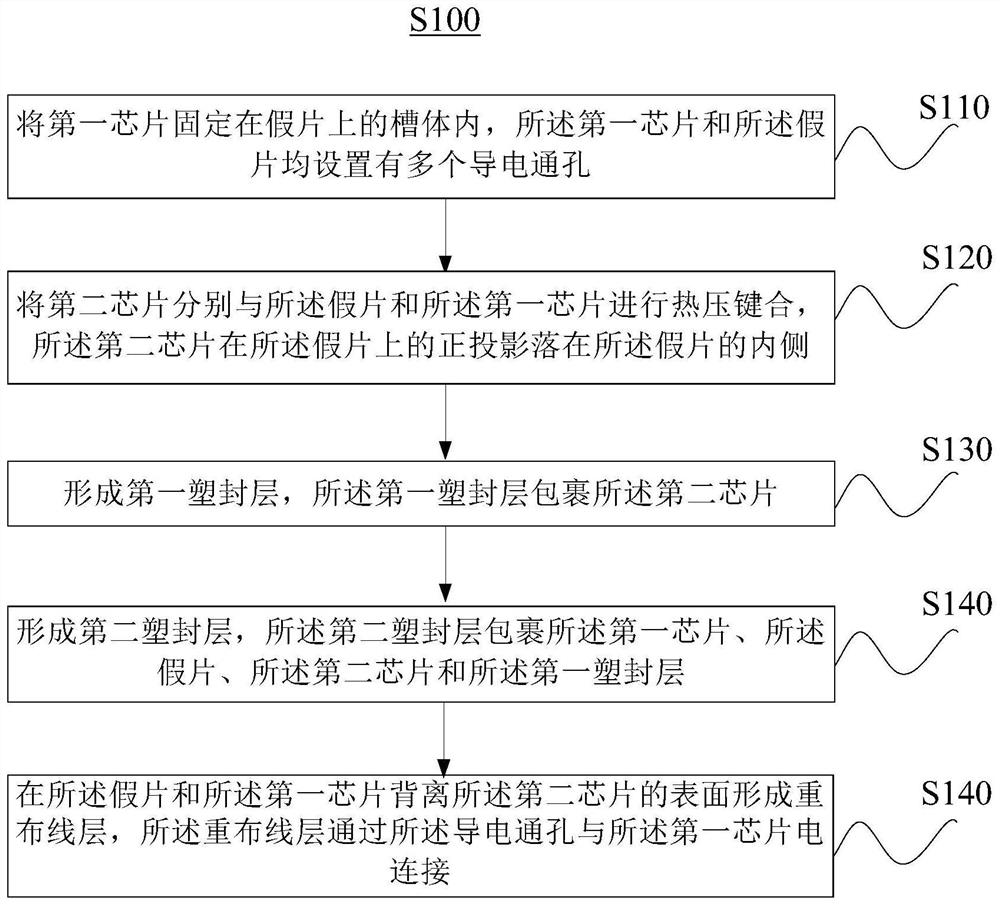

[0042] Such as figure 2 As shown, one aspect of the present invention provides a fan-out stacked chip packaging method S100, the packaging method S100 includes:

[0043] S110. Fix the first chip in the groove on the dummy, where the first chip and the dummy are both provided with a plurality of conductive through holes.

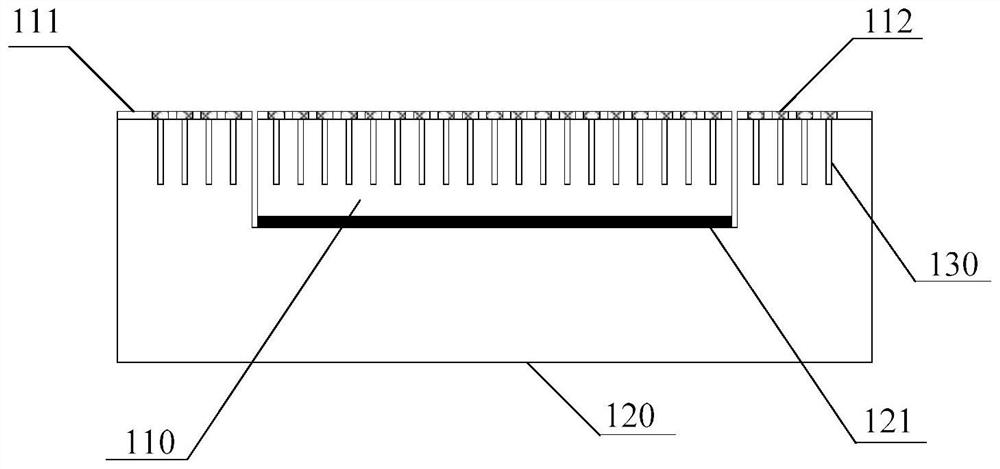

[0044] Specifically, such as image 3 As shown, the back side of the first chip 110 is fixed in the groove on the dummy 120 by the adhesive 121, wherein the surface of the first chip 110, that is, the front of the first chip 110 is flush with the surface of the dummy 120 In other words, the surface of the first chip 110 is flush with the surface of the dummy sheet 120 so as to better perform thermocom...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com