Astronavigation general gate-level logic modeling method for form verification

A form verification and modeling method technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems that cannot meet the requirements of aerospace-grade integrated circuit evaluation and use, to ensure safety and adaptability, guarantee The effect of safety and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

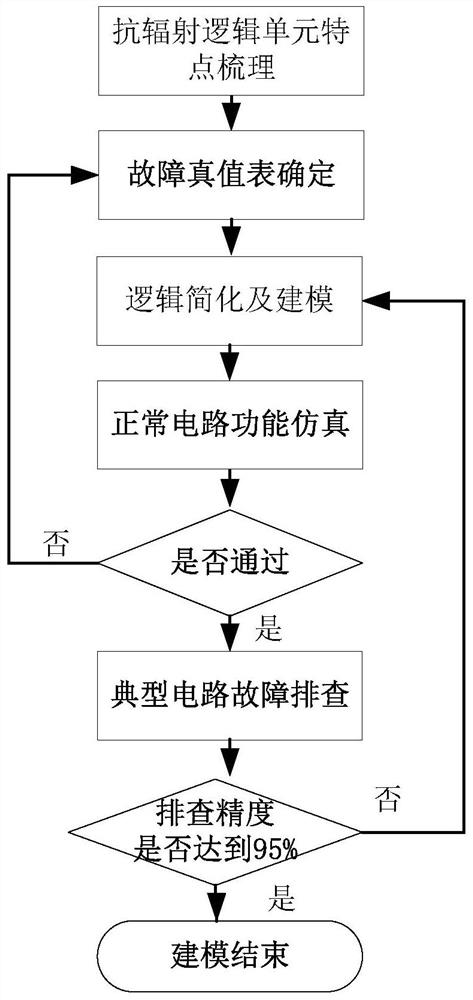

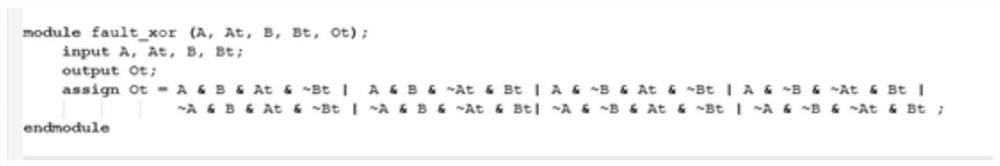

[0026] A general gate-level logic modeling method for aerospace for formal verification, which is used to solve the problem of evaluating the safety attributes of integrated circuits under the space radiation environment and high-reliability application conditions of spacecraft. The specific method steps are as follows:

[0027] (1) Sorting out and analyzing the anti-radiation hardening strategies of aerospace-level large-scale integrated circuits to be verified, and obtaining typical characteristics of aerospace-level large-scale integrated circuit logic gates;

[0028] Among them, the aerospace environment includes extreme temperature, or bit-flip failure modes caused by space radiation conditions;

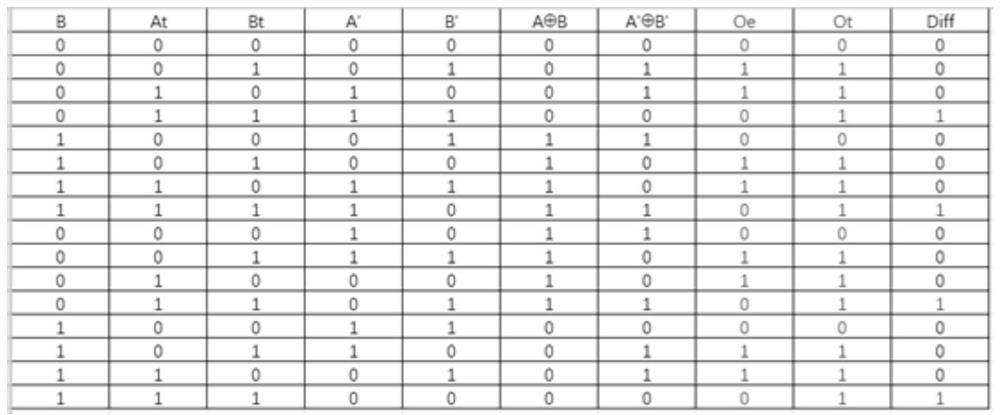

[0029] (2) According to the typical characteristics of the aerospace-grade large-scale integrated circuit logic gate obtained in step (1), and the aerospace environmental pollution label, carry out combing and analysis, and obtain the fault truth table;

[0030] Among them, the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com