Patents

Literature

182 results about "Radiation hardening" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Radiation hardening is process of making electronic components and circuits resistant to damage or malfunction caused by high levels of ionizing radiation (particle radiation and high-energy electromagnetic radiation), especially for environments in outer space and high-altitude flight, around nuclear reactors and particle accelerators, or during nuclear accidents or nuclear warfare.

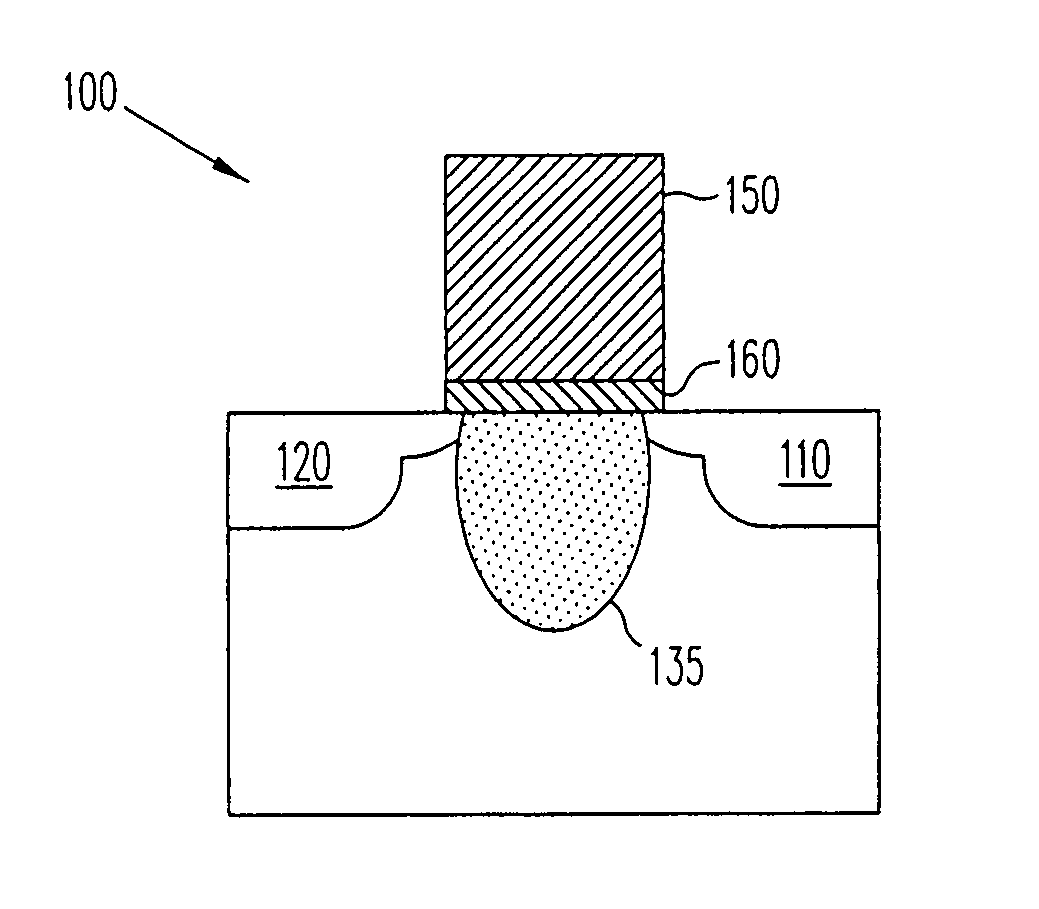

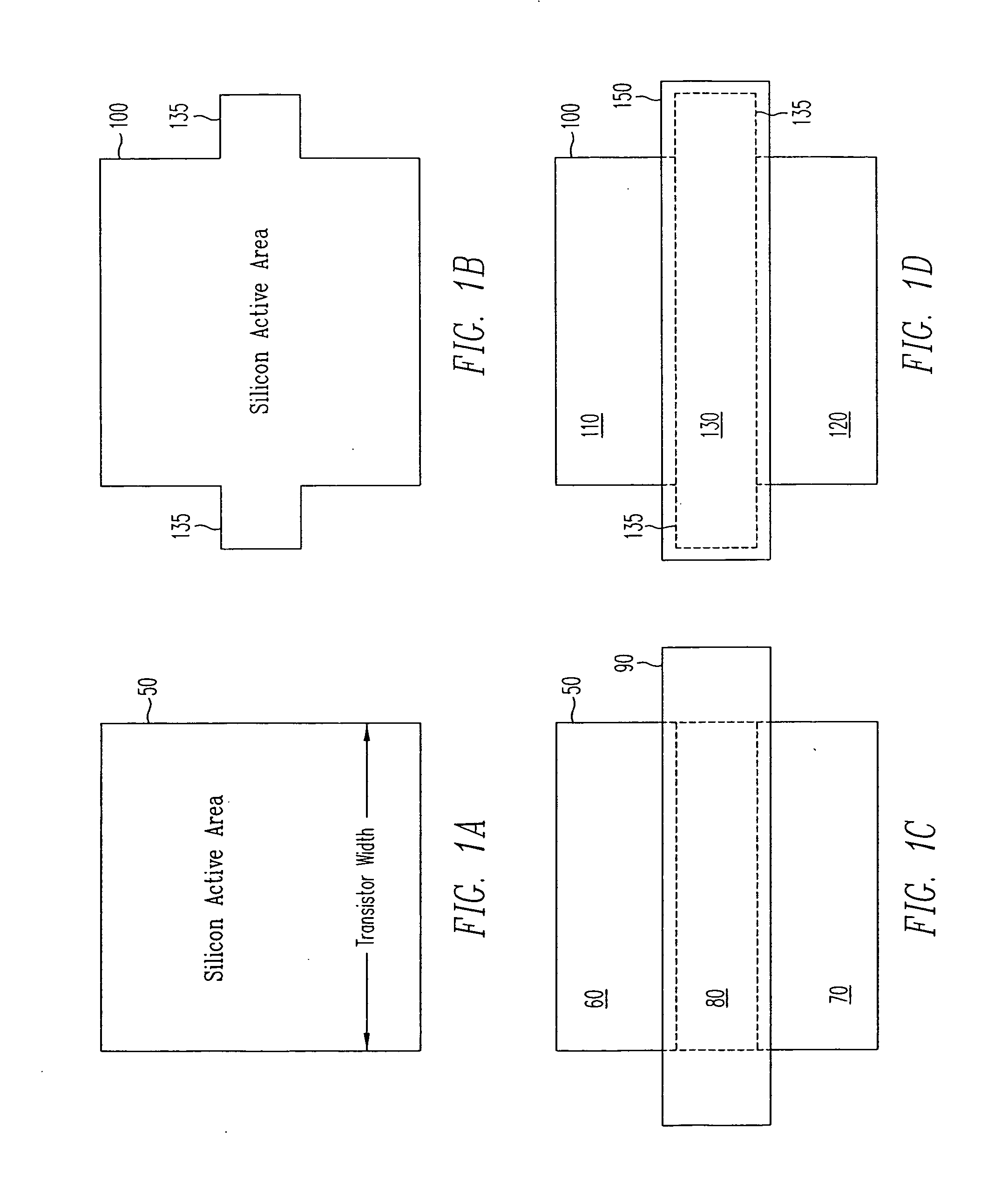

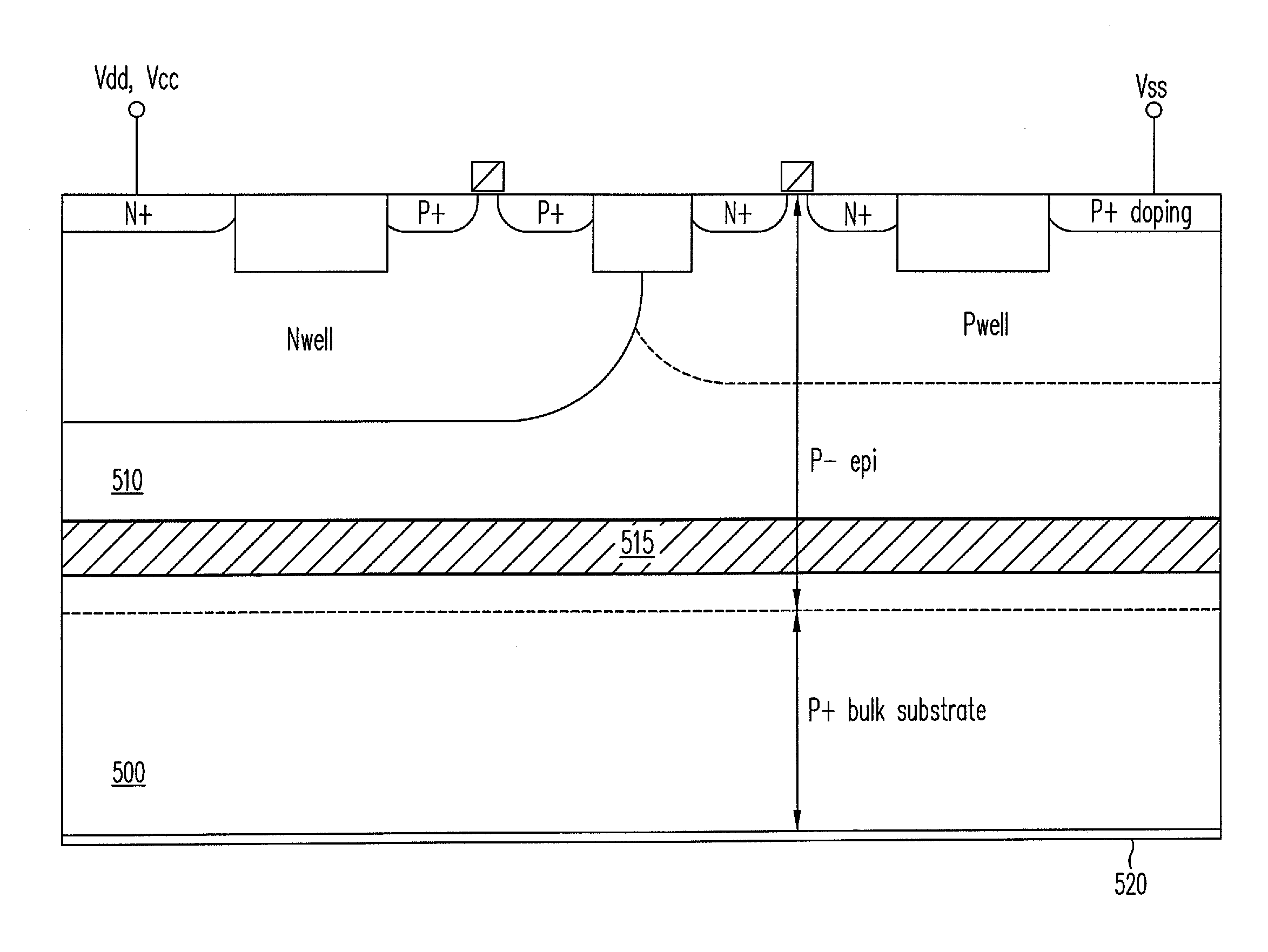

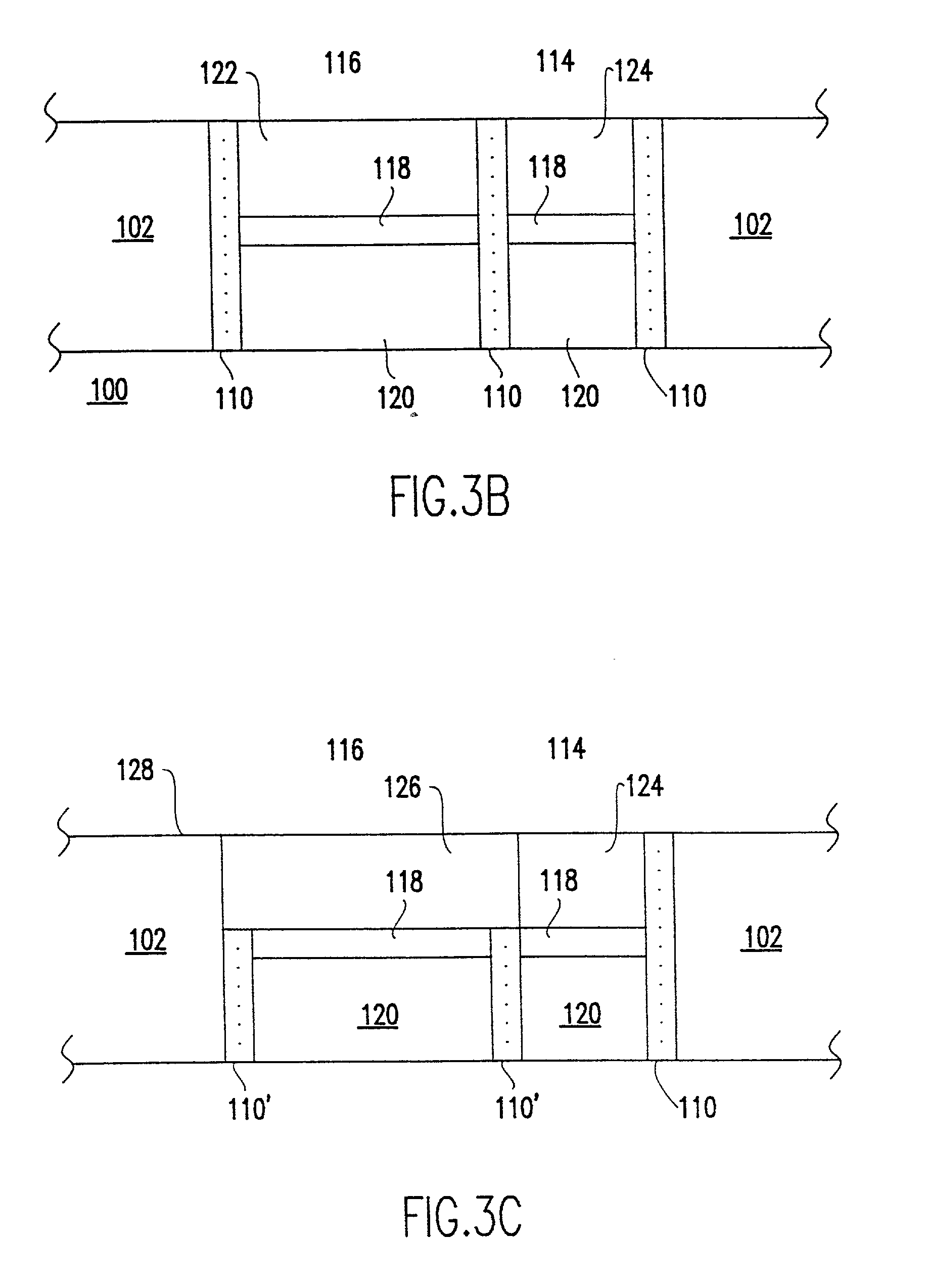

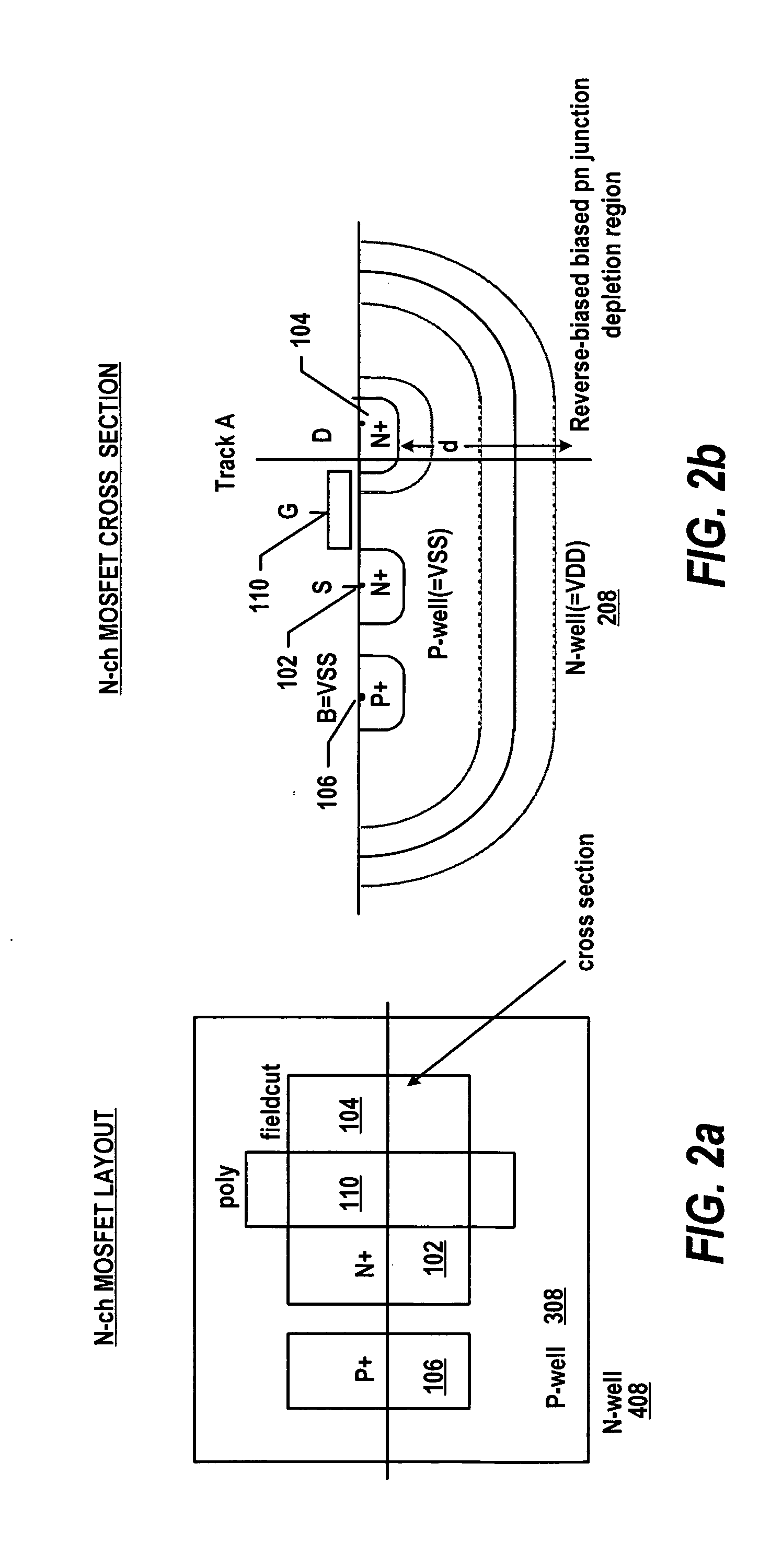

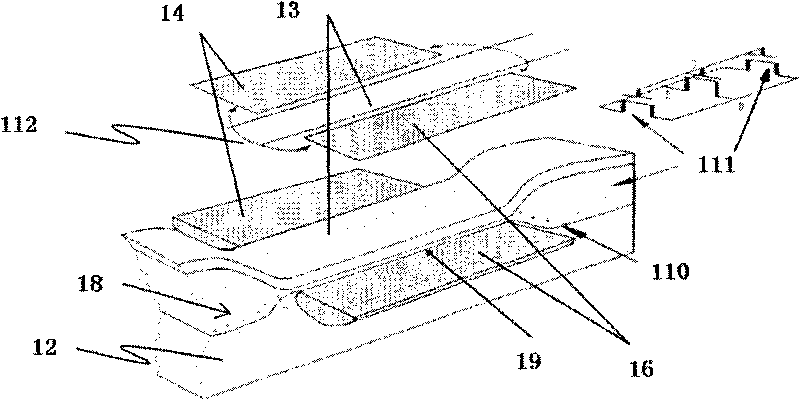

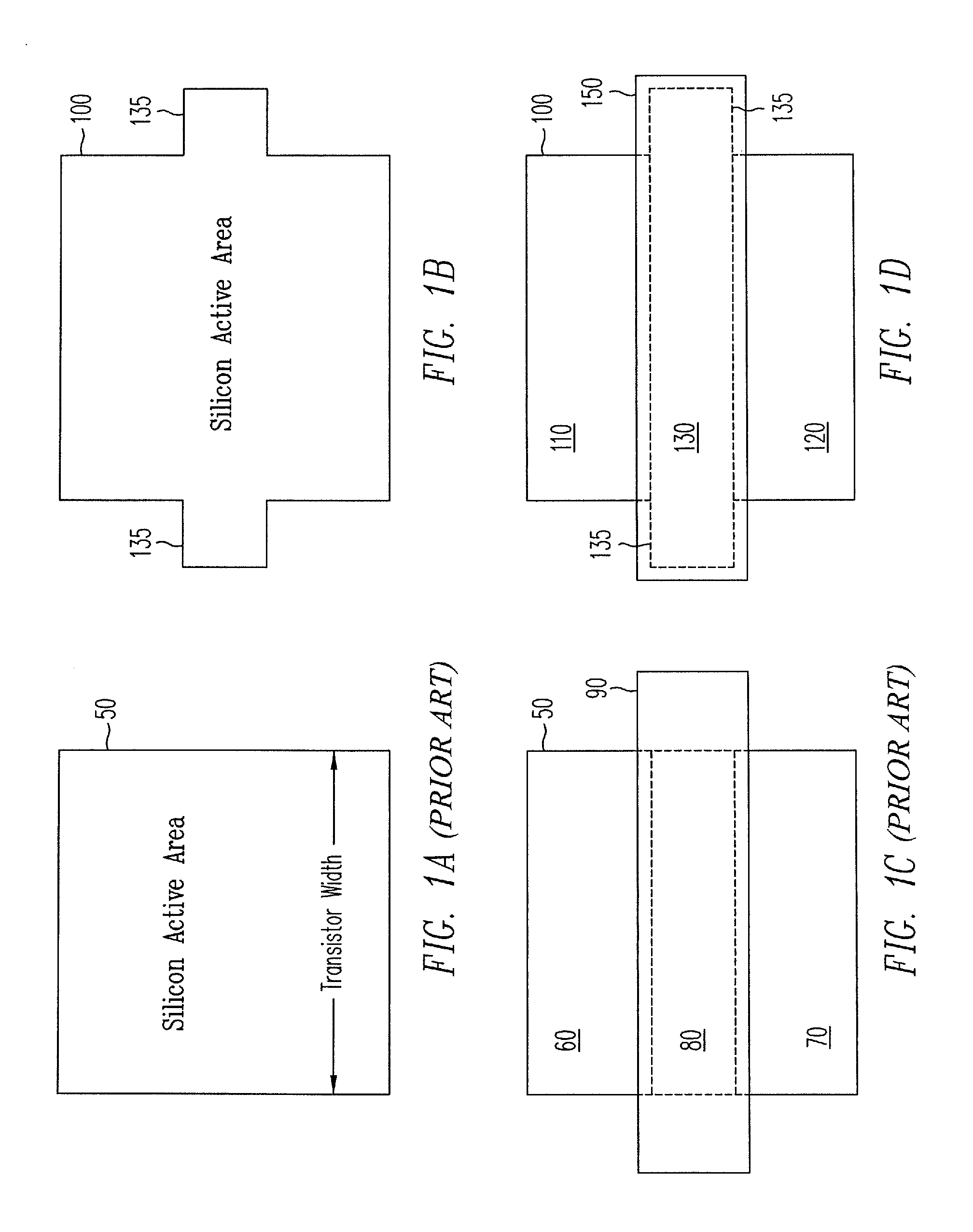

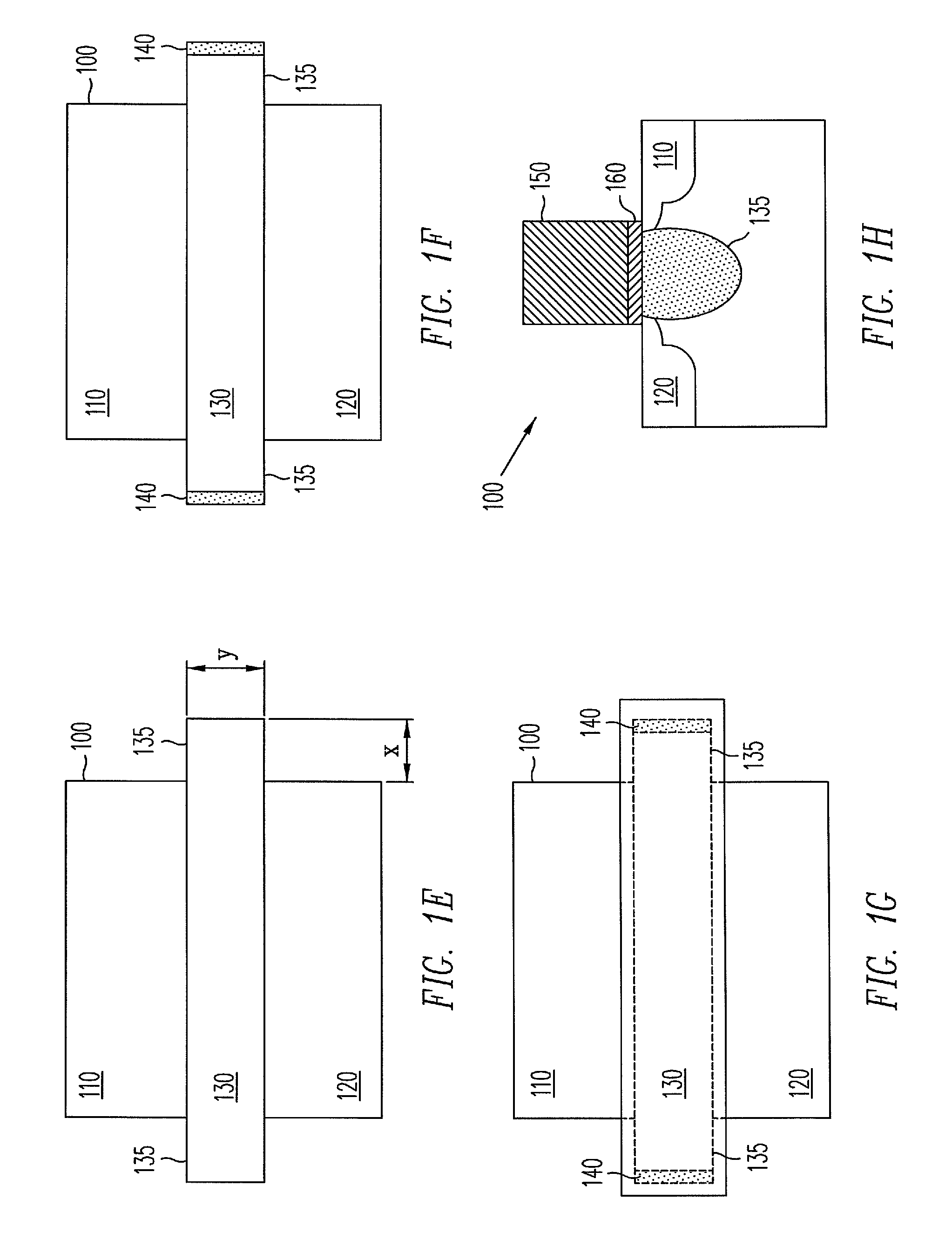

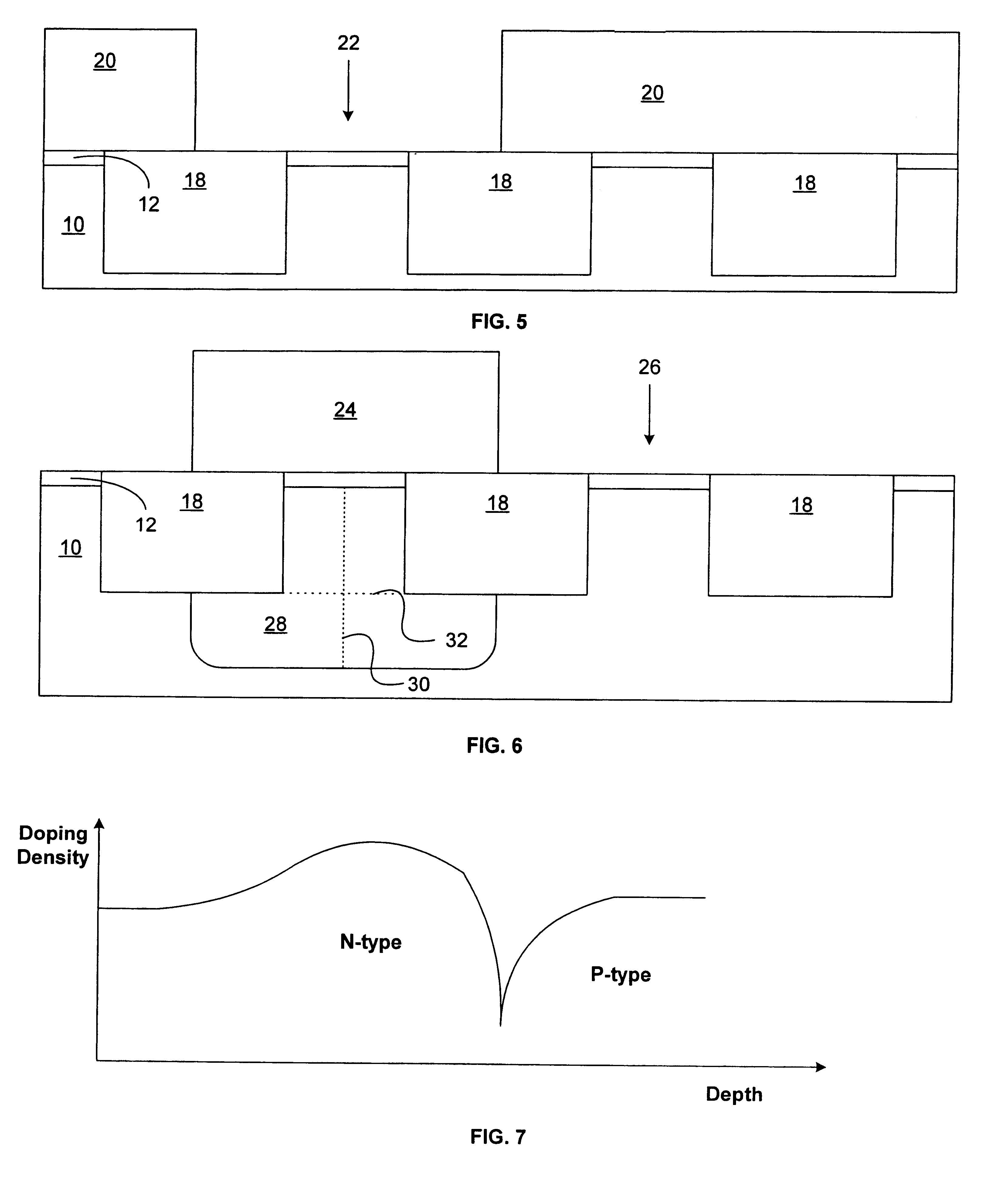

Radiation hardened isolation structures and fabrication methods

ActiveUS20070141794A1Reduce and eliminate effectLow costTransistorSolid-state devicesManufacturing technologyDevice material

Semiconductor devices can be fabricated using conventional designs and process but including specialized structures to reduce or eliminate detrimental effects caused by various forms of radiation. Such semiconductor devices can include one or more parasitic isolation devices and / or buried layer structures disclosed in the present application. The introduction of design and / or process steps to accommodate these novel structures is compatible with conventional CMOS fabrication processes, and can therefore be accomplished at relatively low cost and with relative simplicity.

Owner:SILICON SPACE TECH

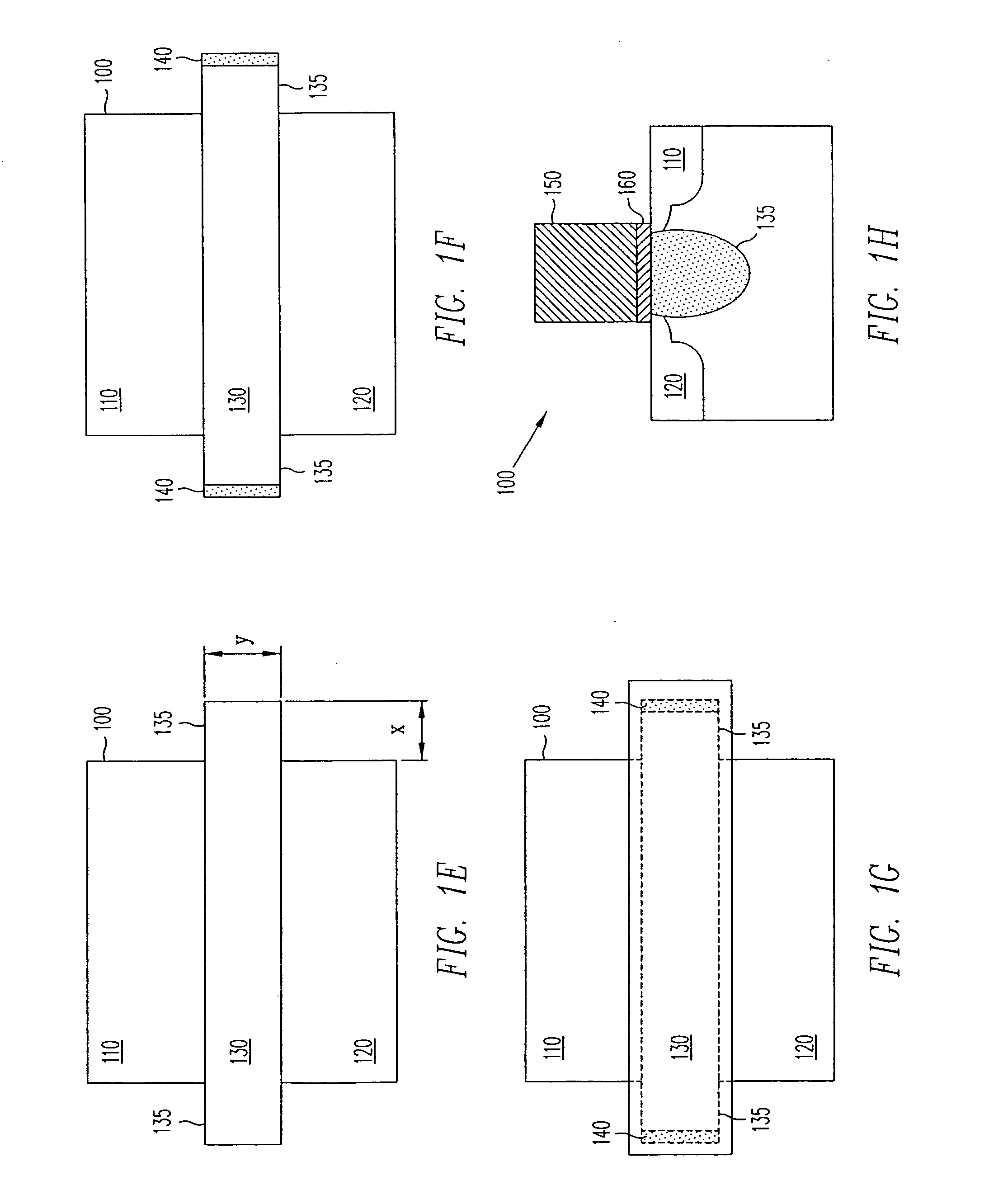

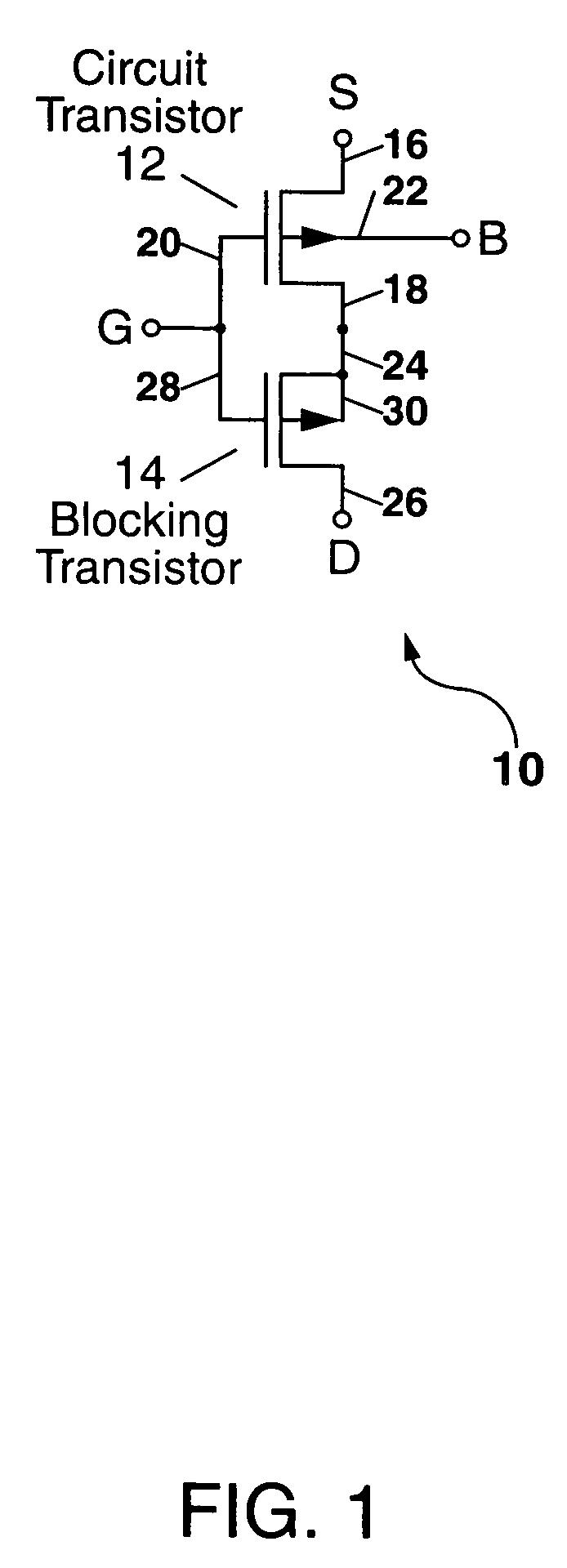

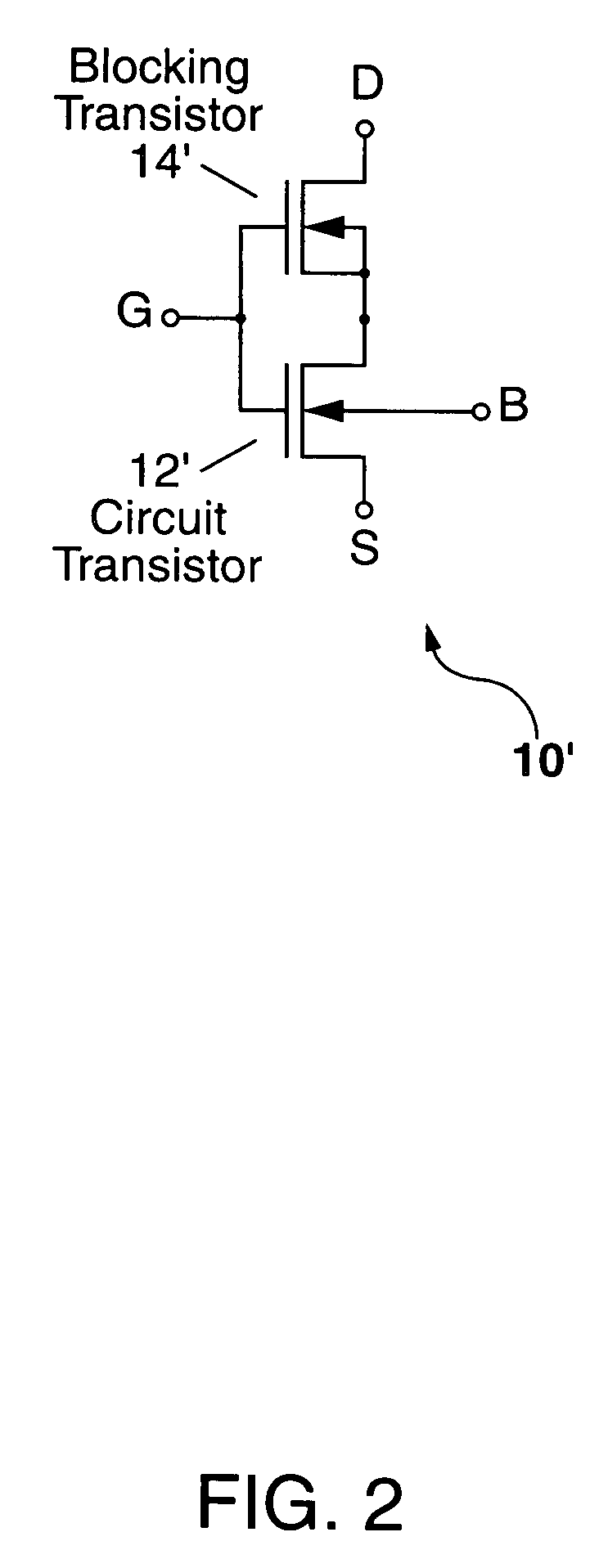

Radiation-hardened transistor and integrated circuit

A composite transistor is disclosed for use in radiation hardening a CMOS IC formed on an SOI or bulk semiconductor substrate. The composite transistor has a circuit transistor and a blocking transistor connected in series with a common gate connection. A body terminal of the blocking transistor is connected only to a source terminal thereof, and to no other connection point. The blocking transistor acts to prevent a single-event transient (SET) occurring in the circuit transistor from being coupled outside the composite transistor. Similarly, when a SET occurs in the blocking transistor, the circuit transistor prevents the SET from being coupled outside the composite transistor. N-type and P-type composite transistors can be used for each and every transistor in the CMOS IC to radiation harden the IC, and can be used to form inverters and transmission gates which are the building blocks of CMOS ICs.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

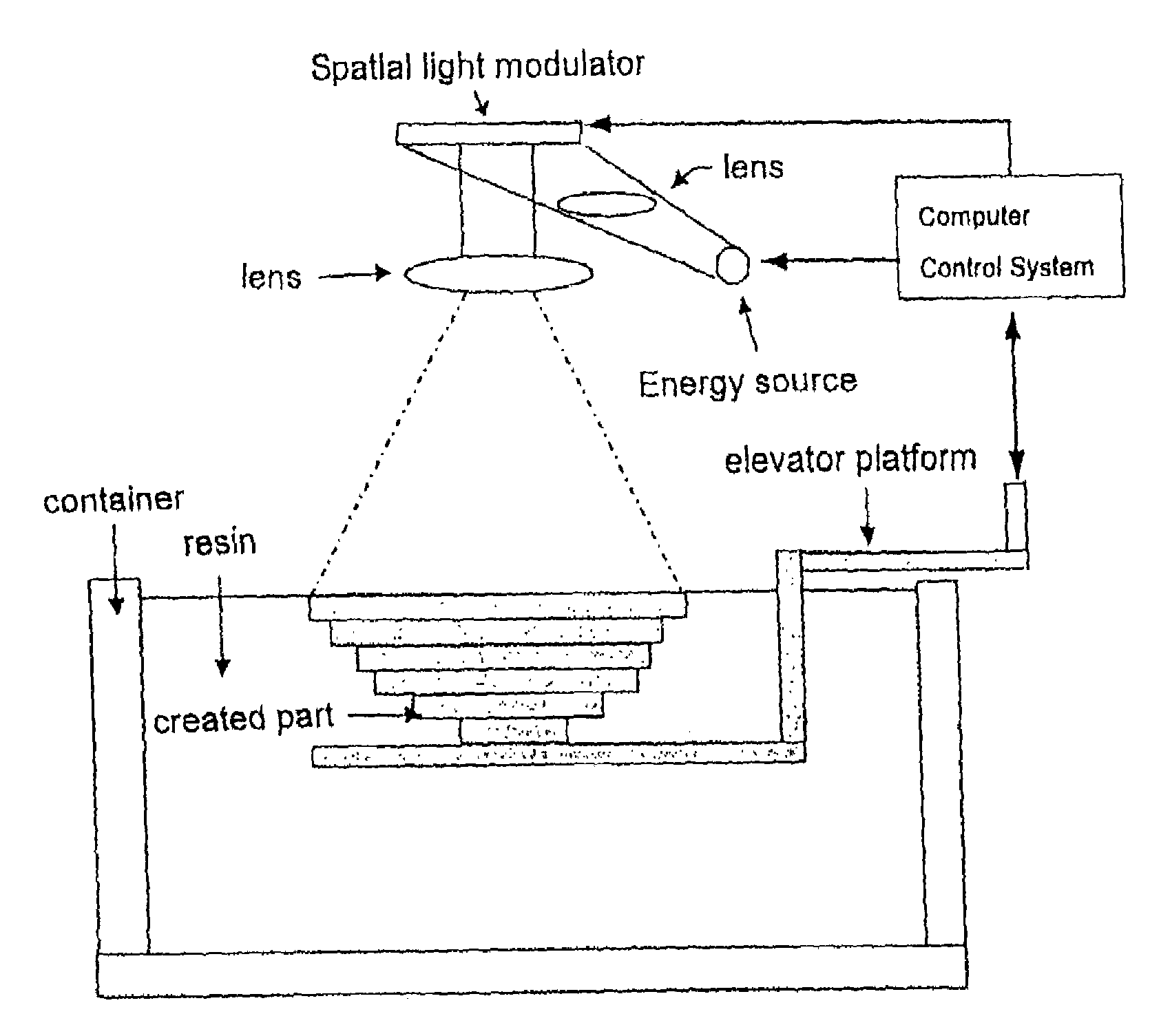

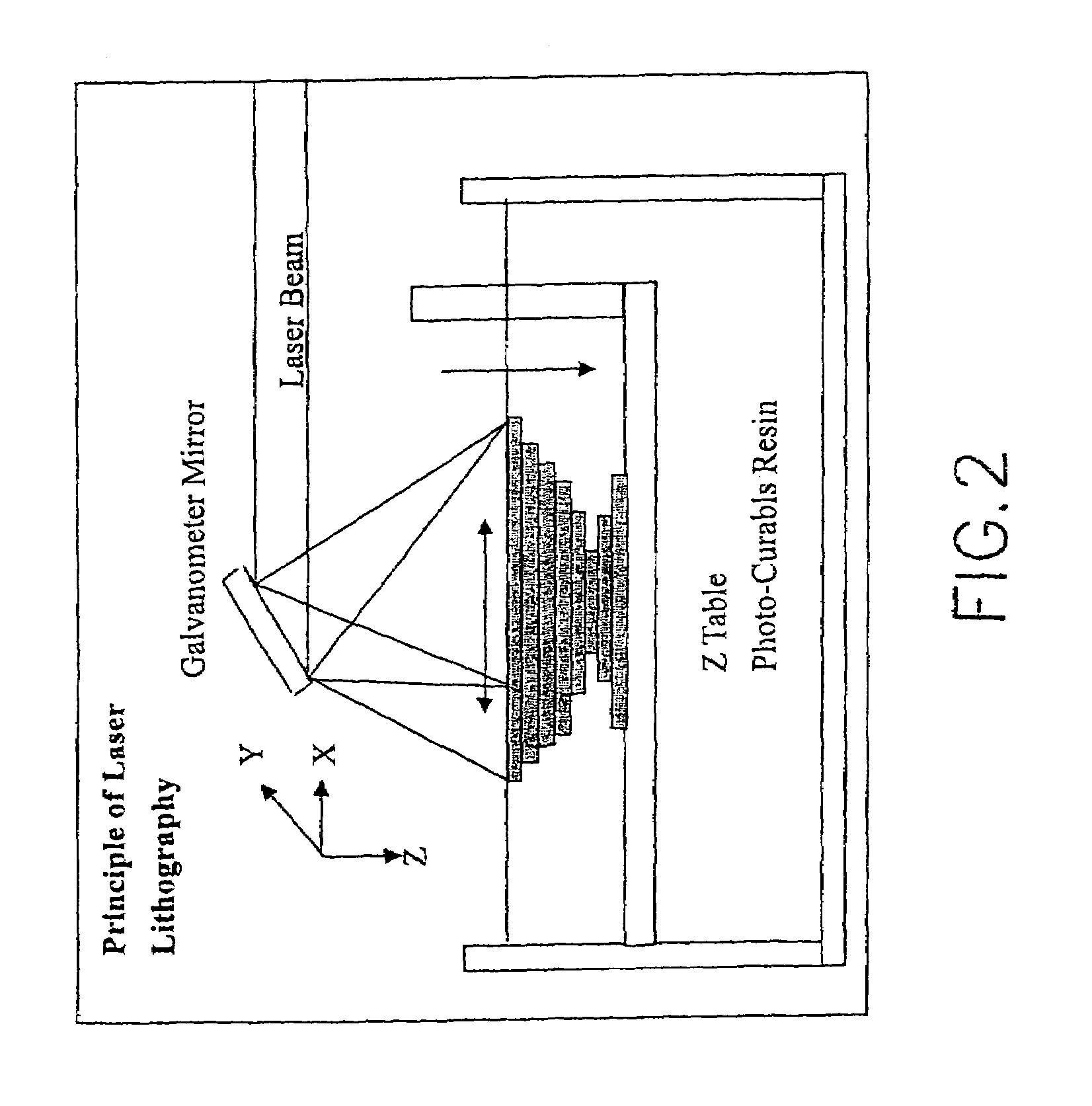

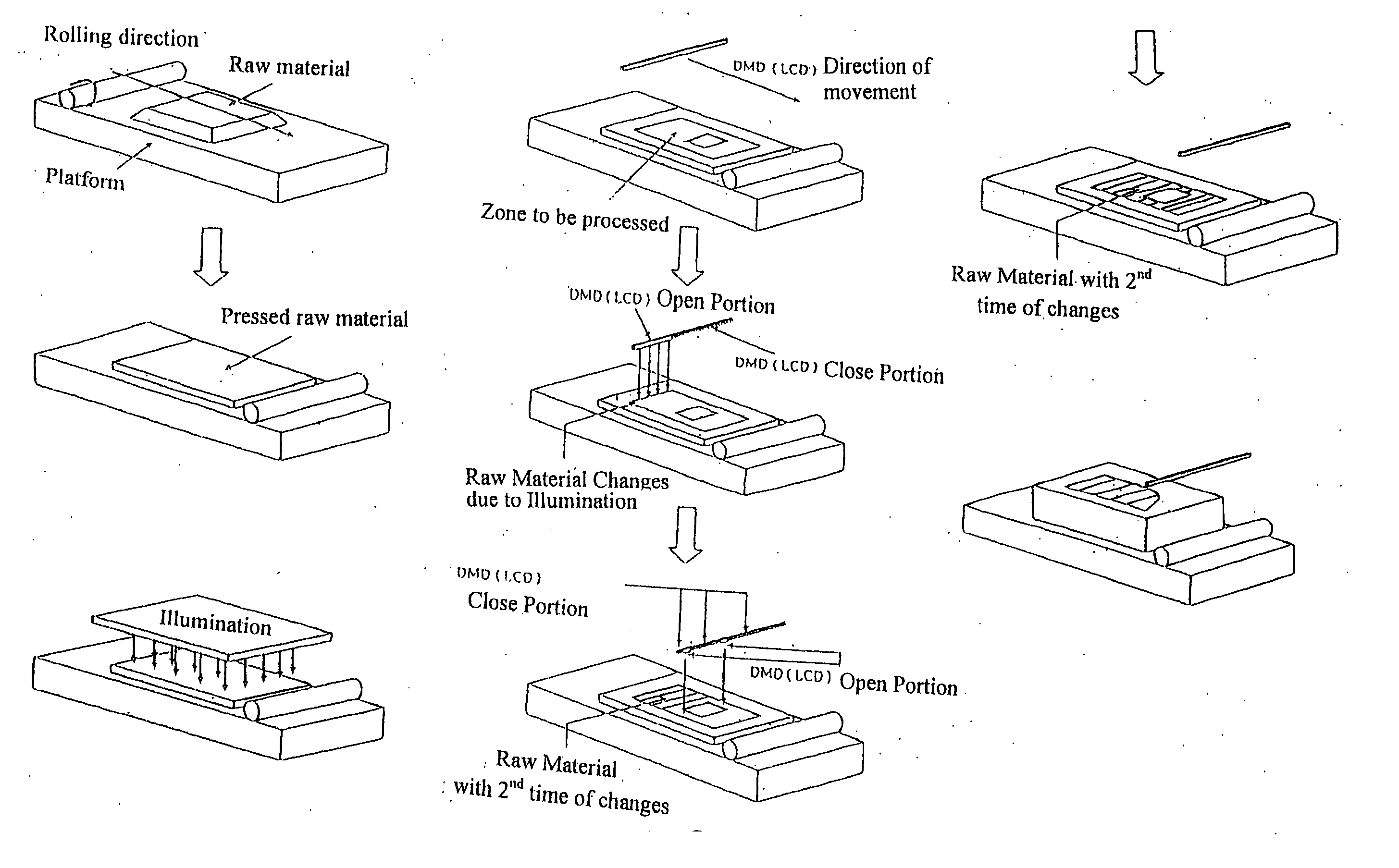

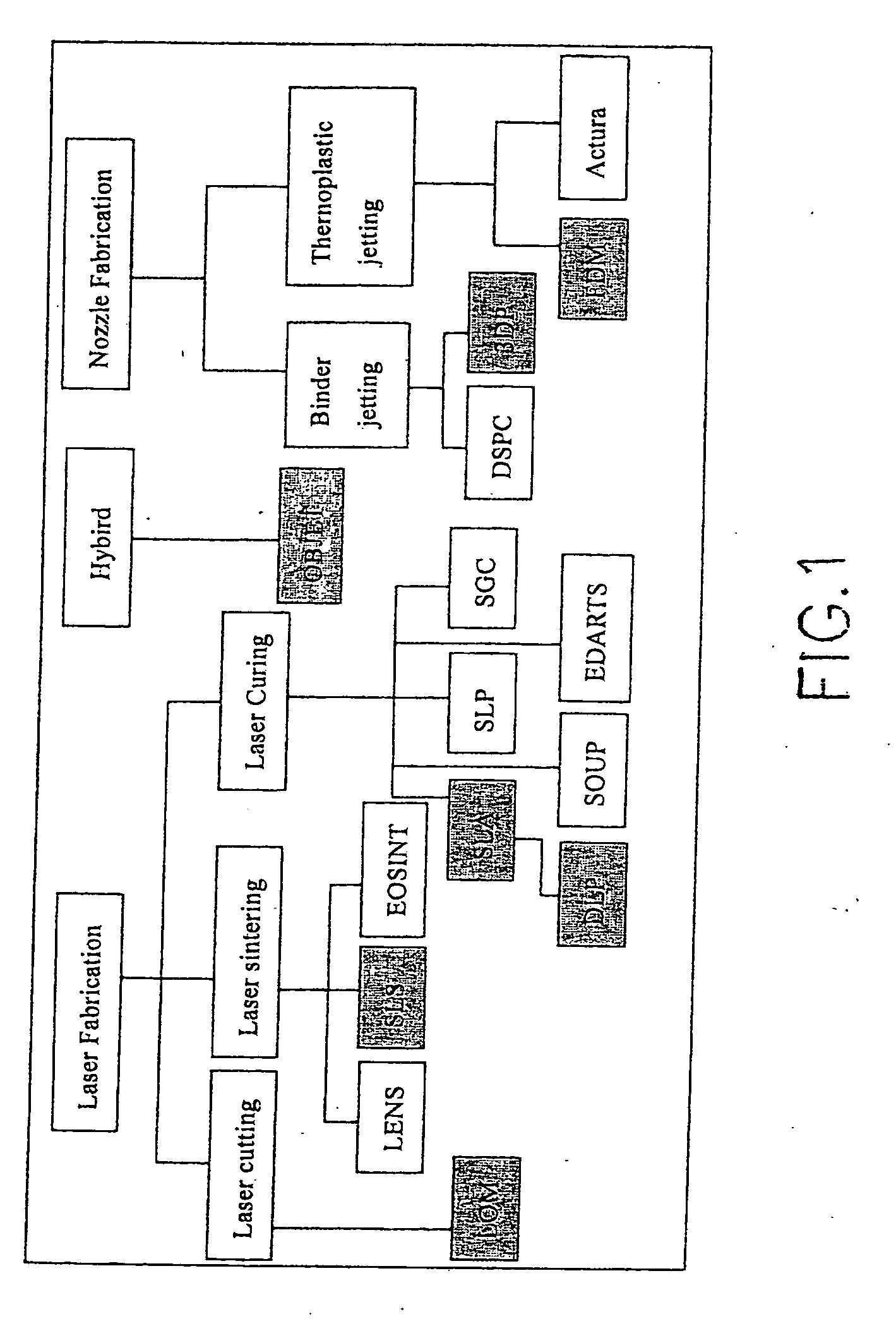

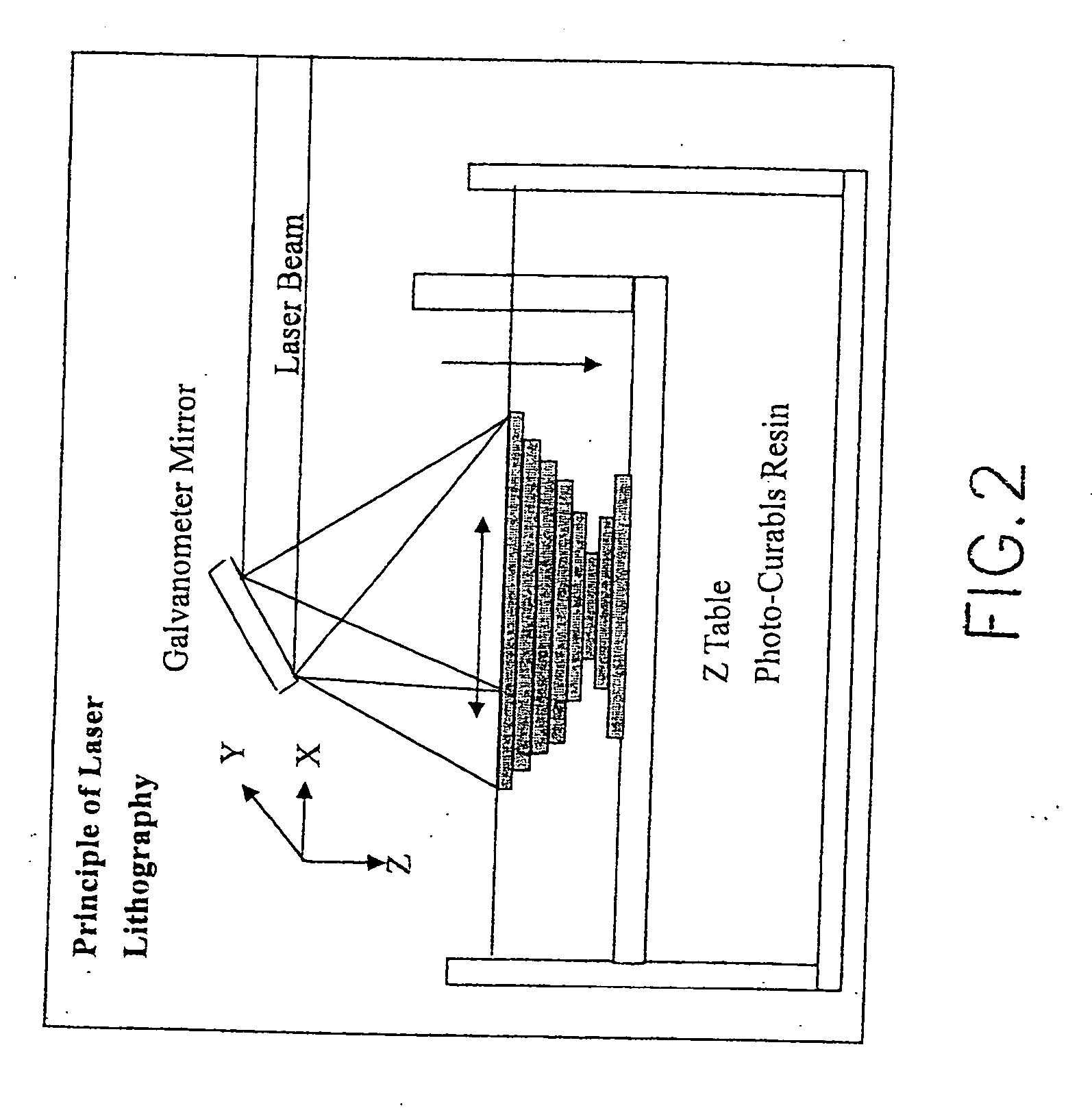

Method for rapid prototyping by using linear light as sources

InactiveUS7158849B2Additive manufacturing apparatus3D object support structuresLiquid-crystal displayEngineering

A method for rapid prototyping by using linear light as sources employs DLP (Radiation Hardening Formation) or LCD, together with the portable devices and linear light source to treat the raw material in two stages. The first stage is to spread the raw material to a selected zone by nozzles or rollers and illuminating the material to let the material being processed and have physical o mechanical changes. The second stage is to use more powerful linear light source with the cooperation of the portable DMD (Digital Micromirror Device) or LCD (Liquid Crystal Display) to illuminate the material to make it have a second times of physical o mechanical changes. By the piling up the layers of the material, a complete 3-D work piece is obtained.

Owner:NAT CHENG KUNG UNIV

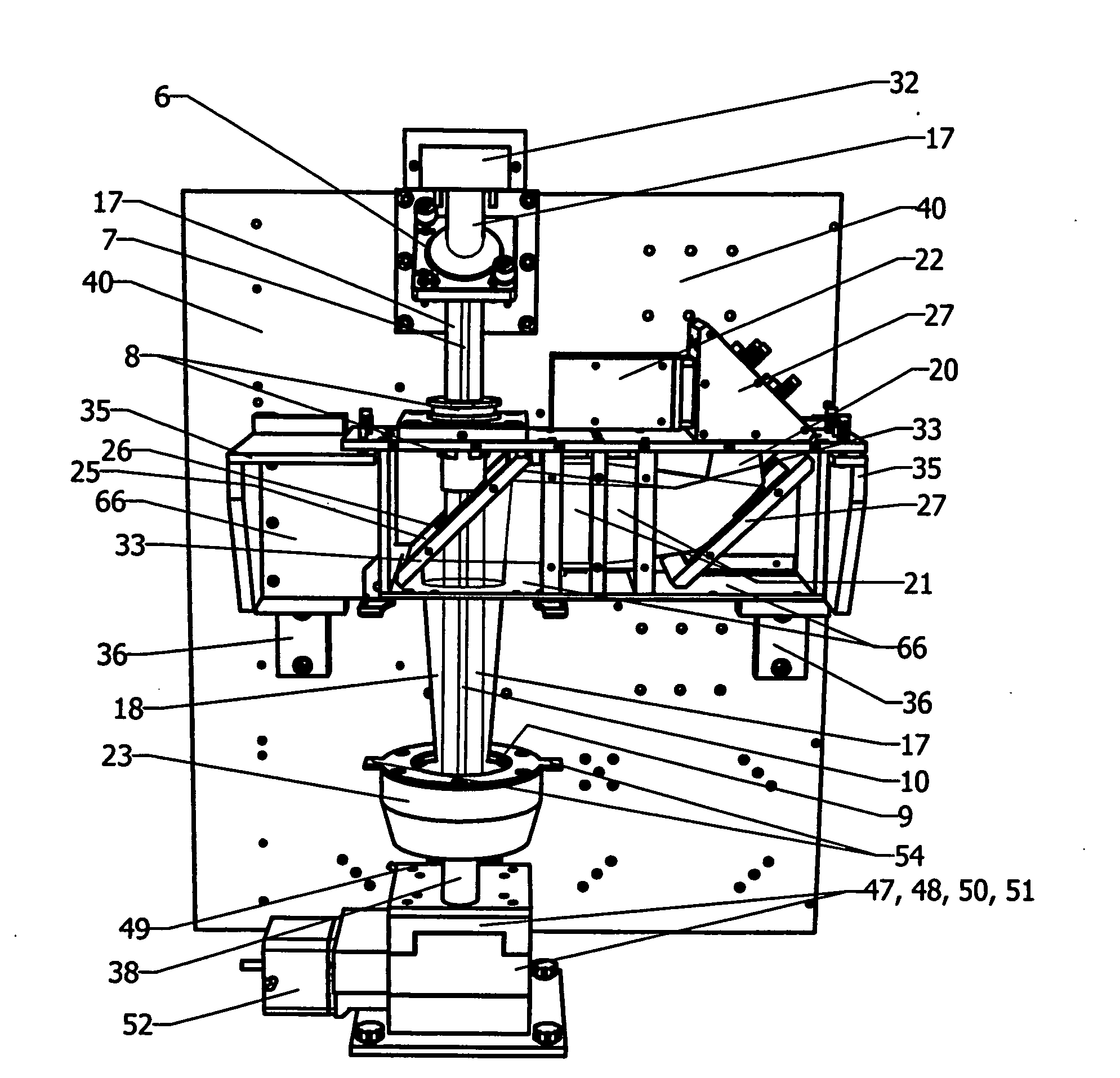

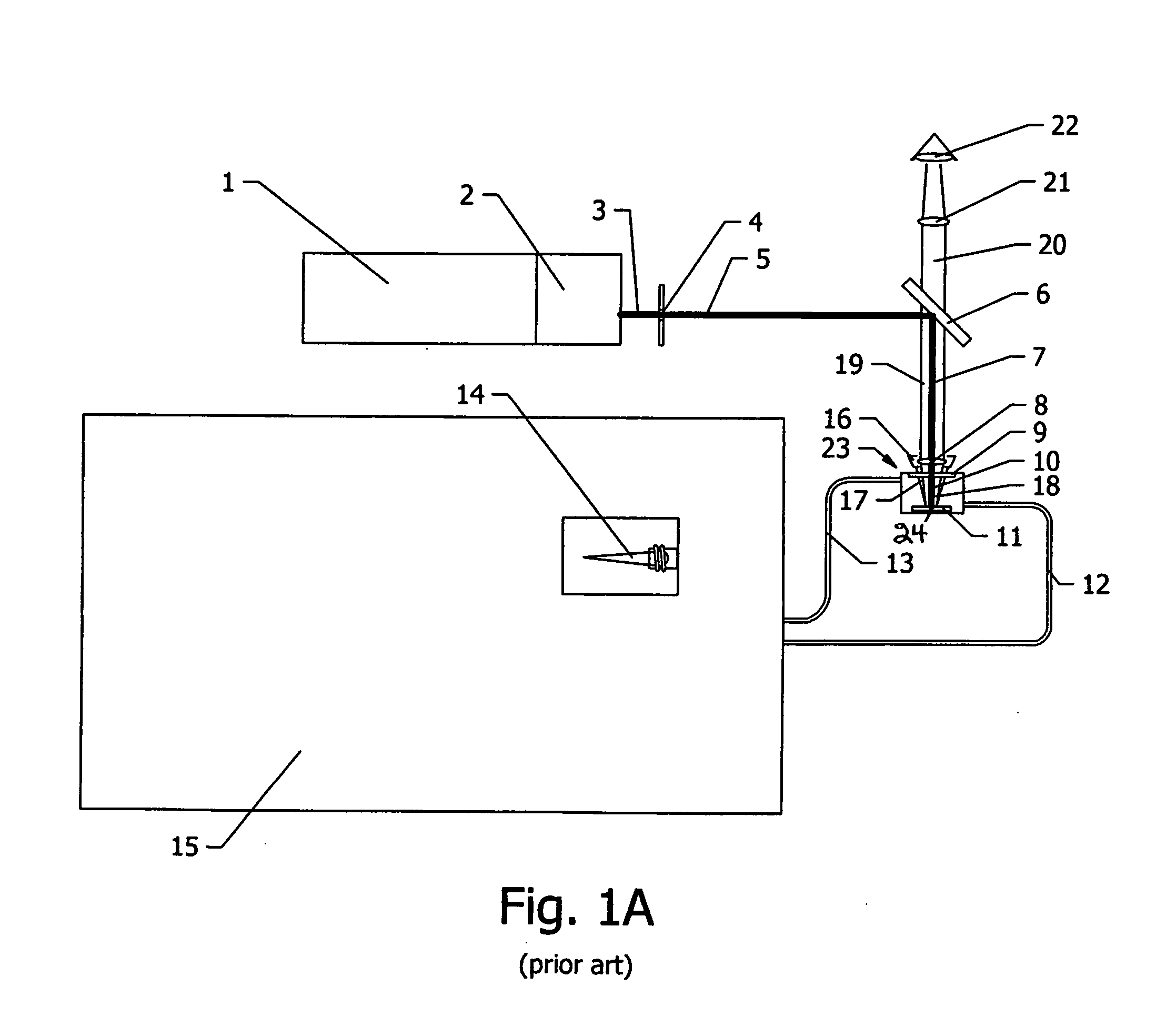

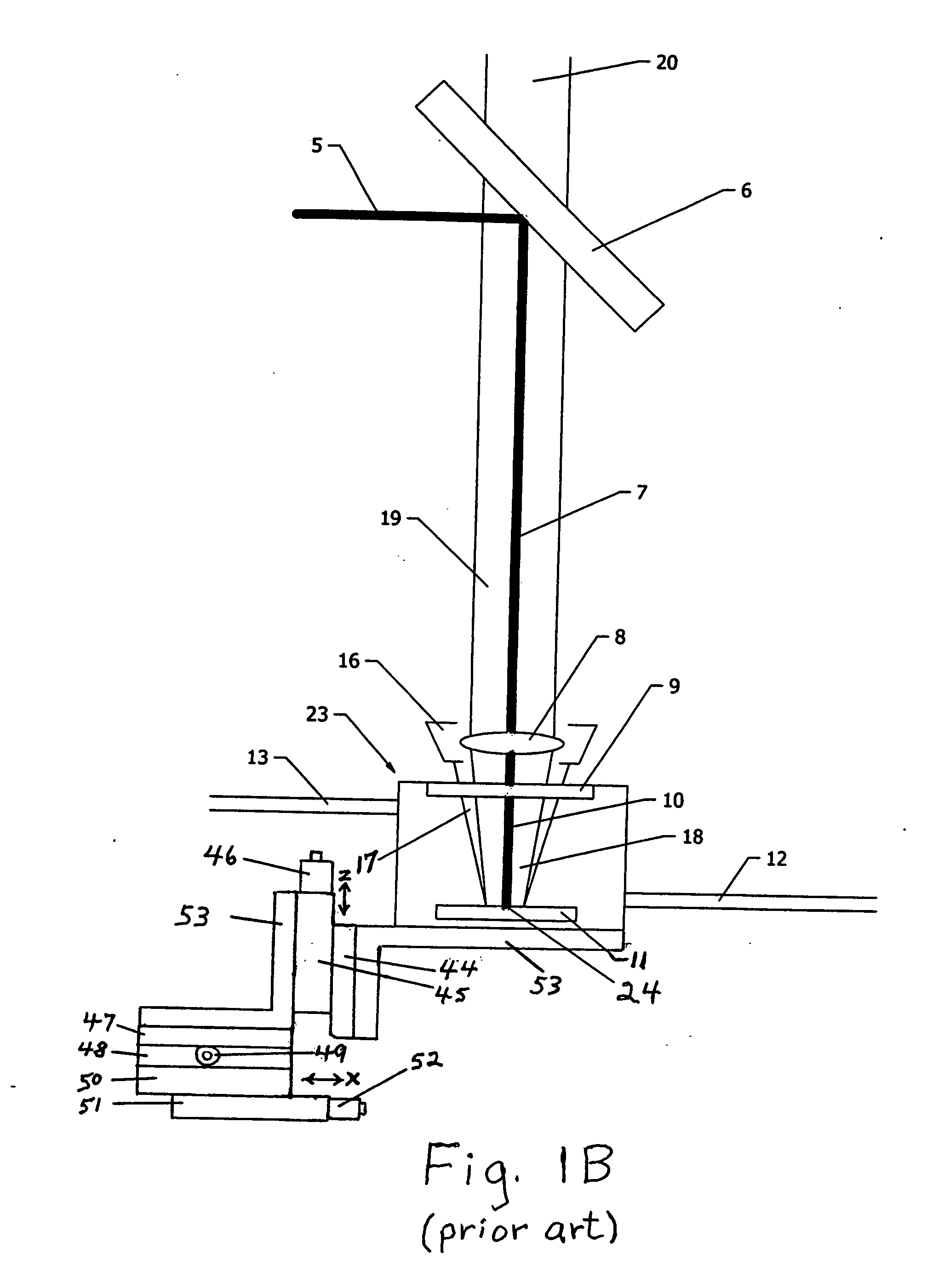

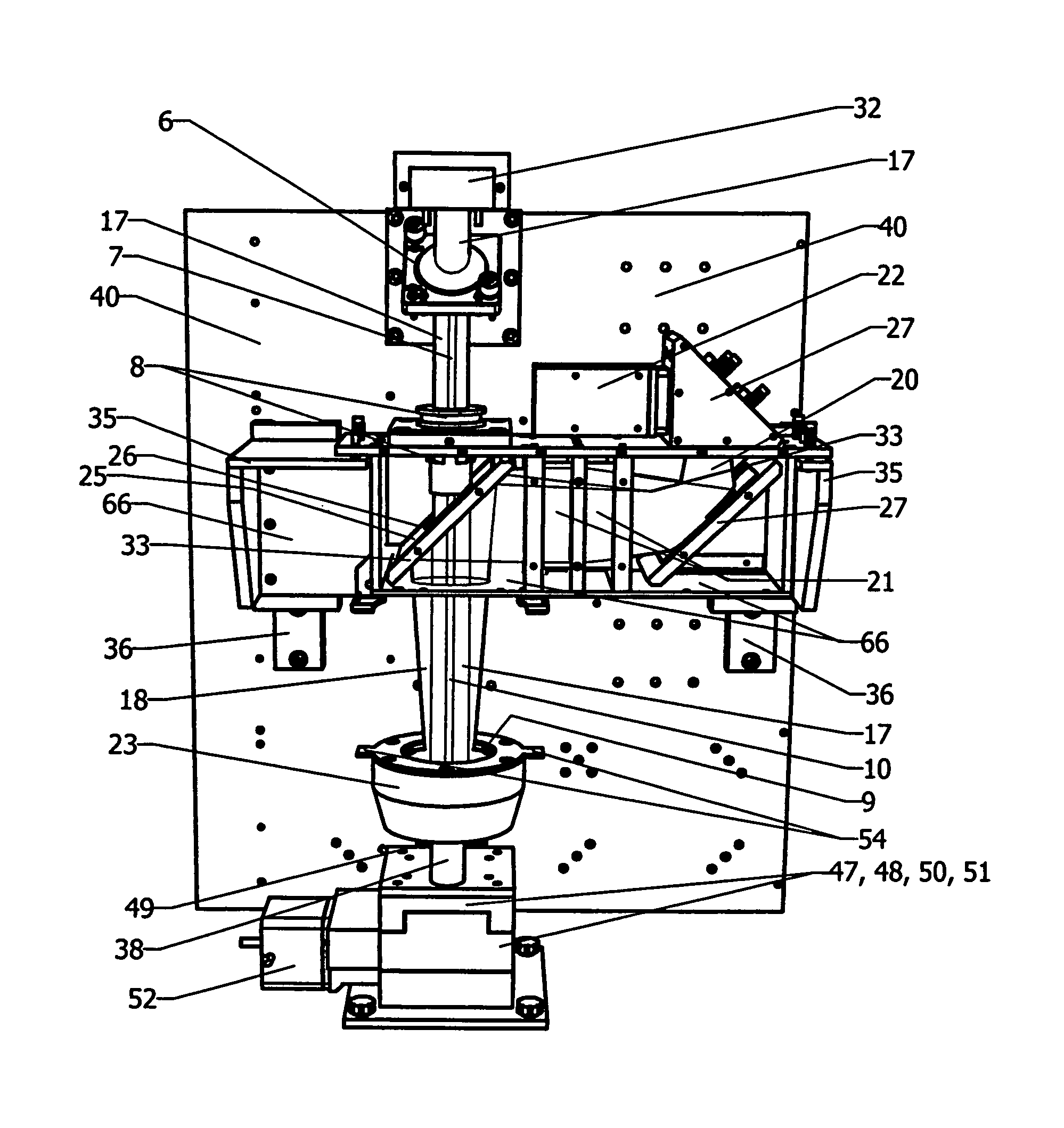

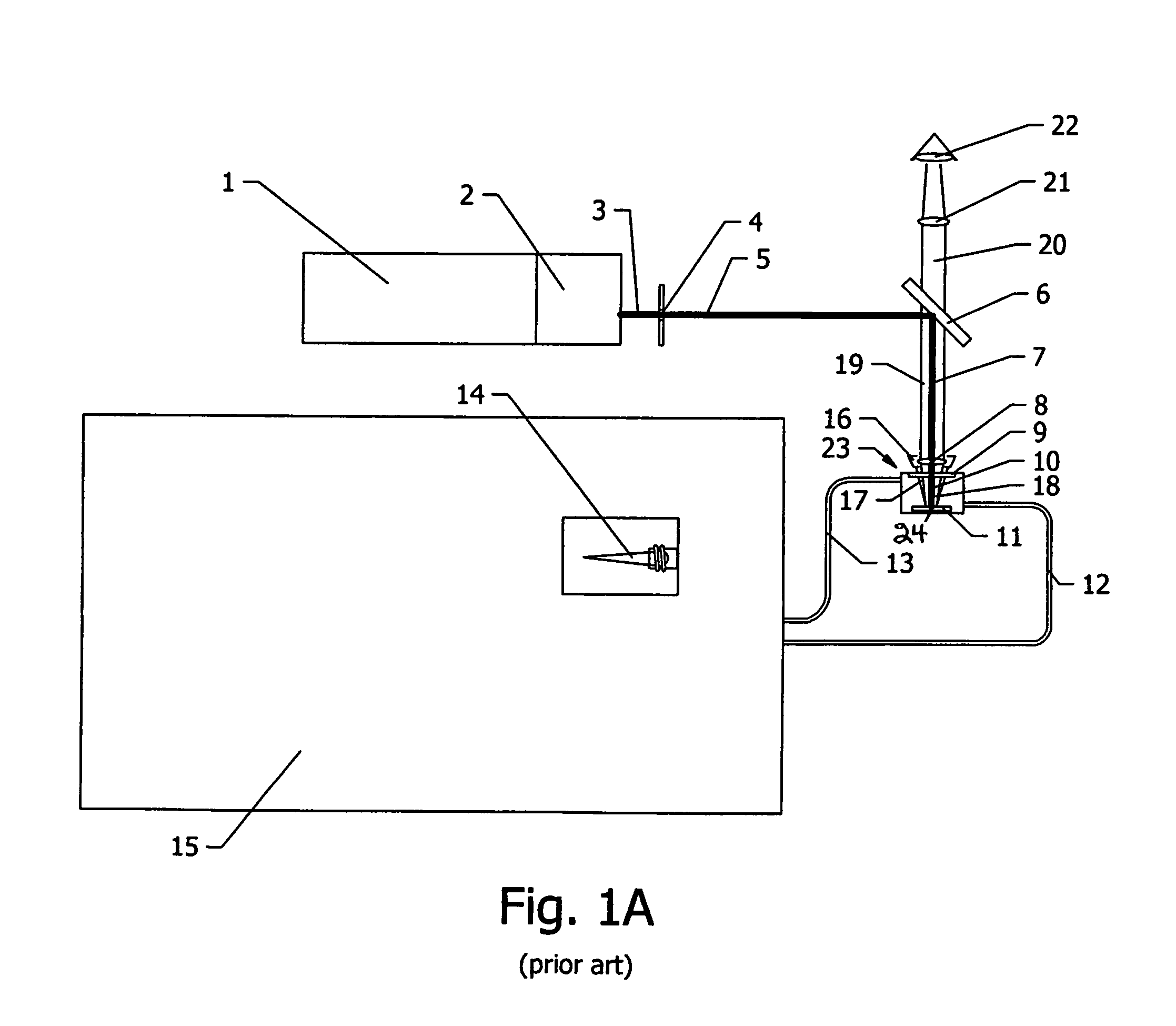

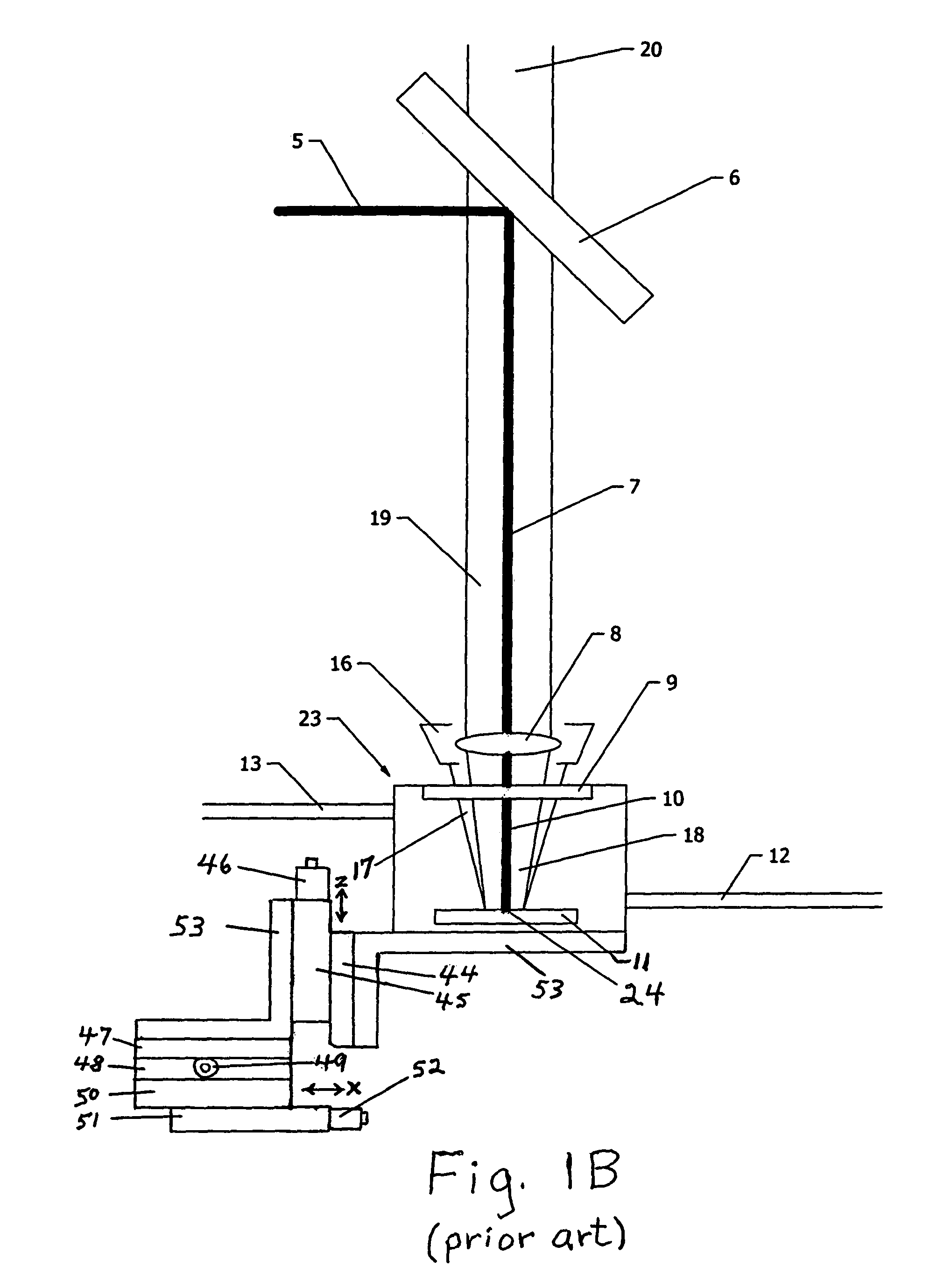

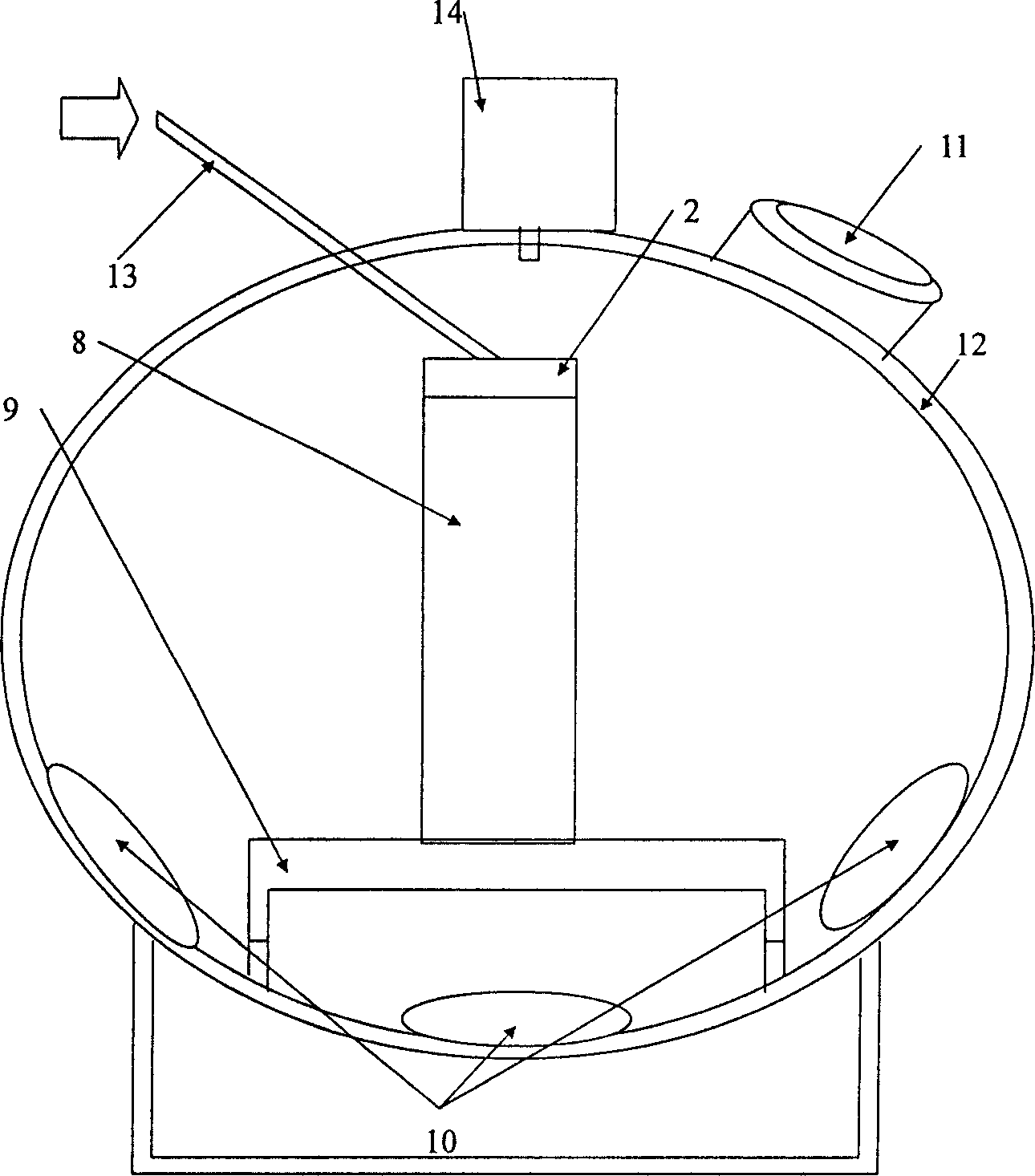

Analytical laser ablation of solid samples for ICP, ICP-MS, and FAG-MS analysis

InactiveUS20090073586A1High sensitivityReduce decreaseMirrorsAnalysis by thermal excitationMolecular analysisPath length

The present invention facilitates improvements in laser ablation of solid samples to be analyzed by an external inductively coupled plasma (ICP) emission spectrometer, ICP / mass-spectrometer (ICP-MS), or flowing afterglow (FAG) mass spectrometer (FAG-MS) for elemental analysis (ICP and ICP-MS) or molecular analysis (FAG-MS). A novel invention mirror-with-hole beam combiner eliminates chromatic aberration in the invention sample view and allows rad-hardening the laser ablation invention for use in a radiation hot cell for analysis of high activity nuclear waste. Many other novel invention rad-hardening attributes facilitate a comprehensive rad-hardened laser ablation system (the world's first). In other embodiments, invention novelties include unusually large homogeneous focused laser spot diameters, unusually long laser objective lens focal length, wide range operationally variable laser path length with built-in re-alignment, operationally variable demagnification ratio and diameter of the focused laser spot, the use of significantly higher powered SMR lasers in a large spot diameter to facilitate high sensitivity bulk analysis of solid samples, a demountable and gravitationally self-sealing stack assembly laser ablation cell, and the world's first auto-samplers (mechanized sample changers) for analytical laser ablation.

Owner:FRY ROBERT C +3

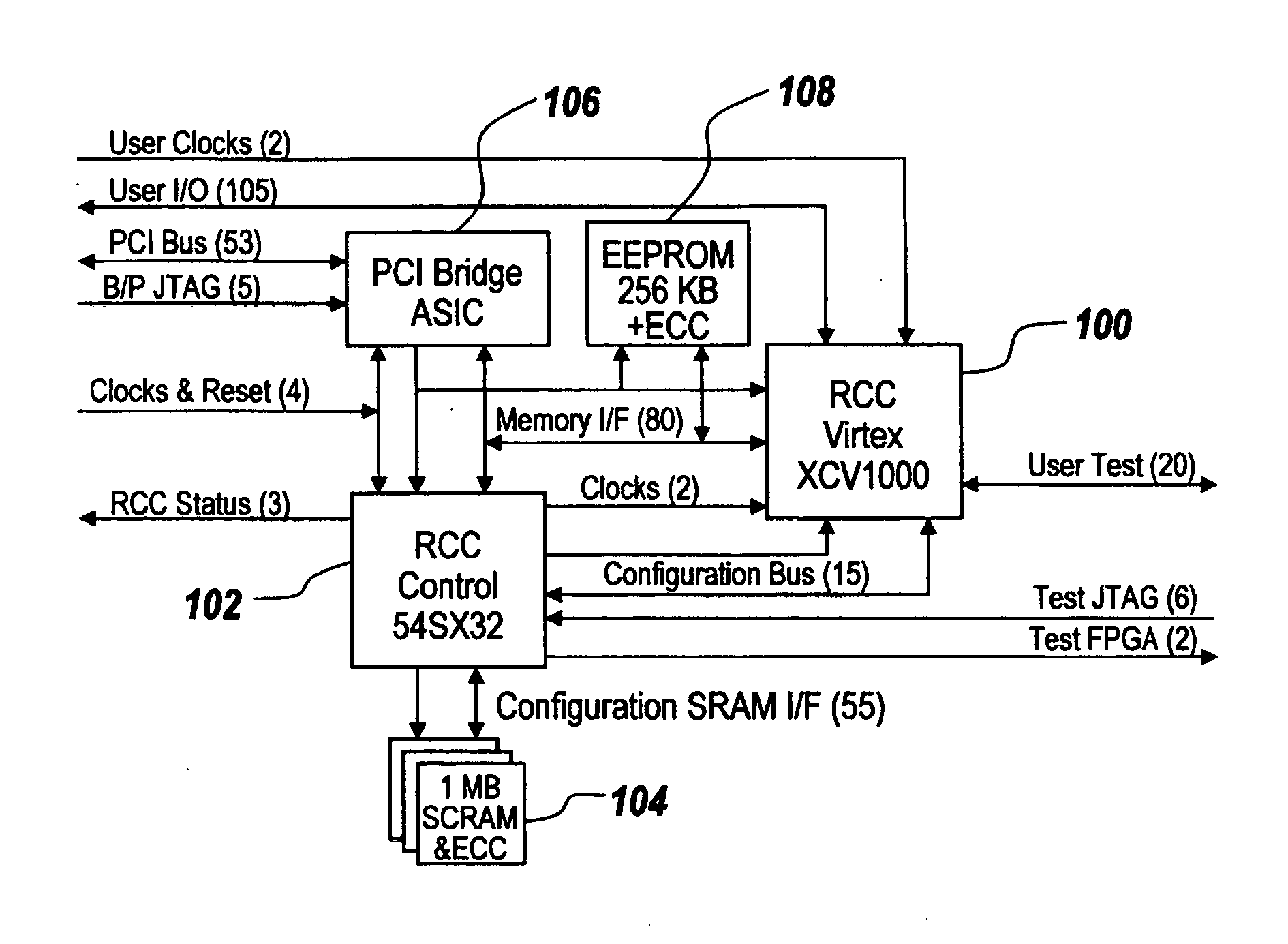

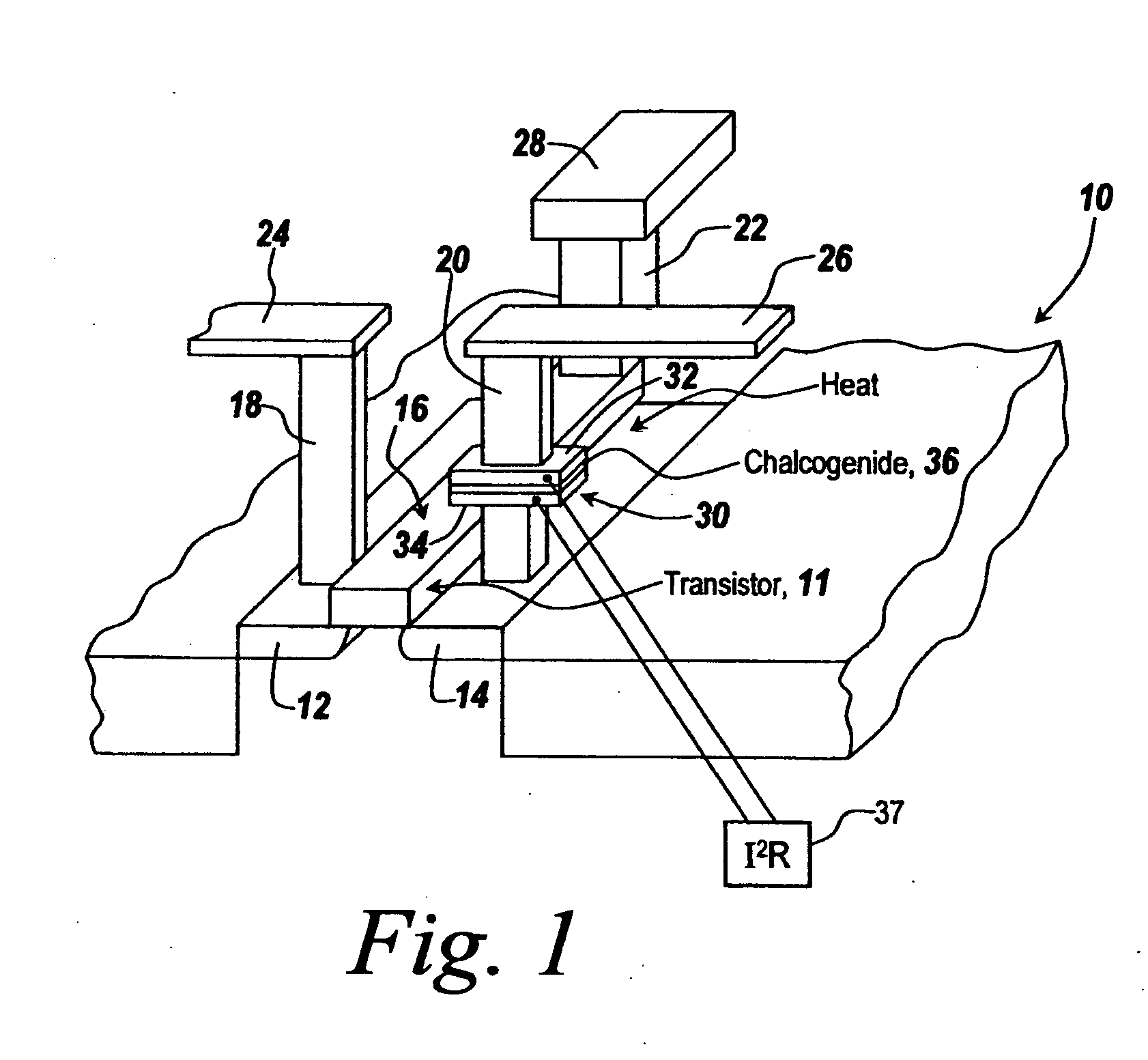

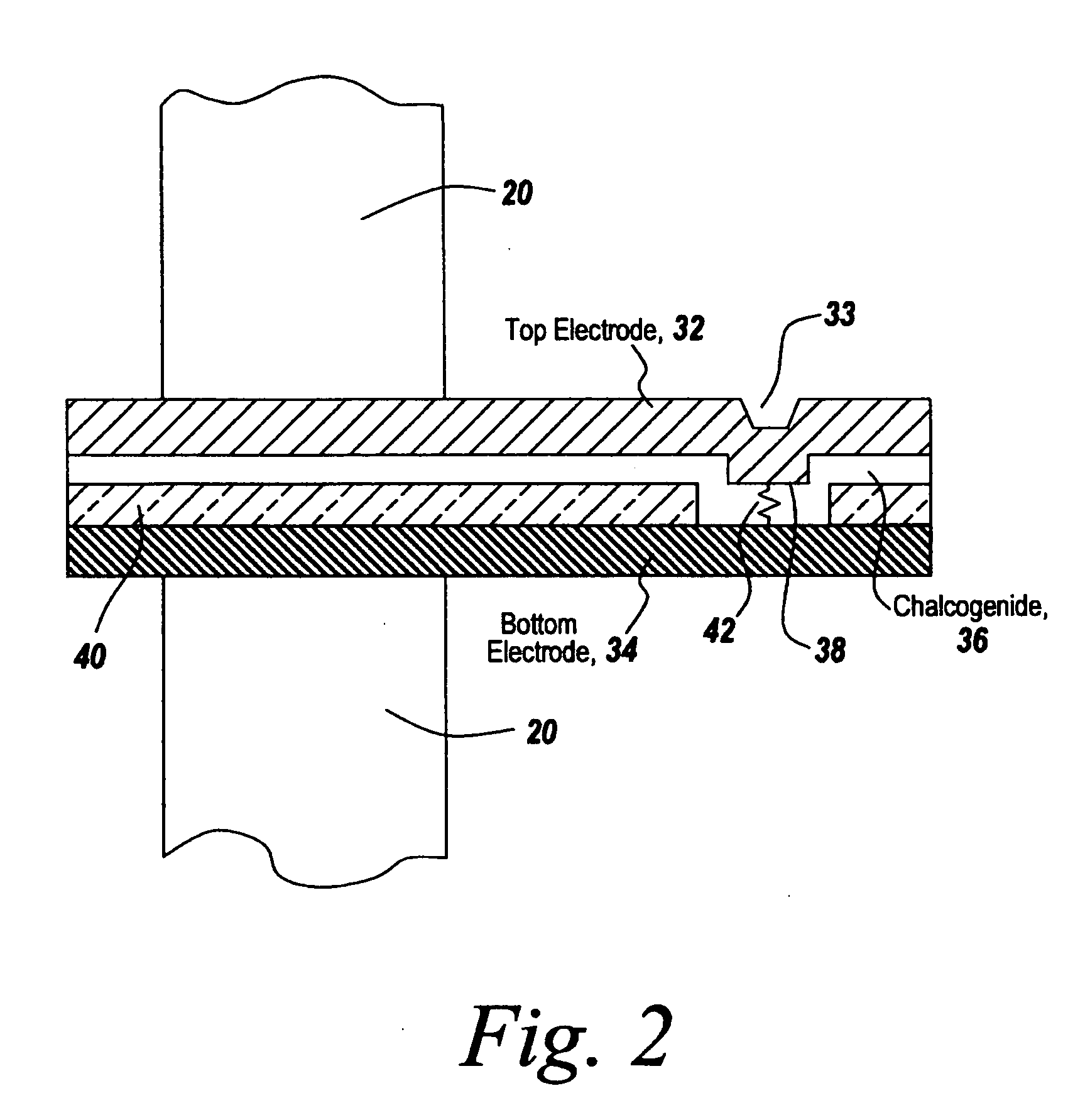

Use of radiation-hardened chalcogenide technology for spaceborne reconfigurable digital processing systems

ActiveUS20050027409A1Increase design complexityIncrease reliability riskCosmonautic vehiclesDigital data processing detailsComputer hardwareSingle chip

Chalcogenide technology is used for radiation hardening for spaceborne systems and more particularly in C-RAM form for processors, field programmable gate arrays, startup RAMs, shadow storage and single-chip systems to protect these units.

Owner:GULA CONSULTING LLC

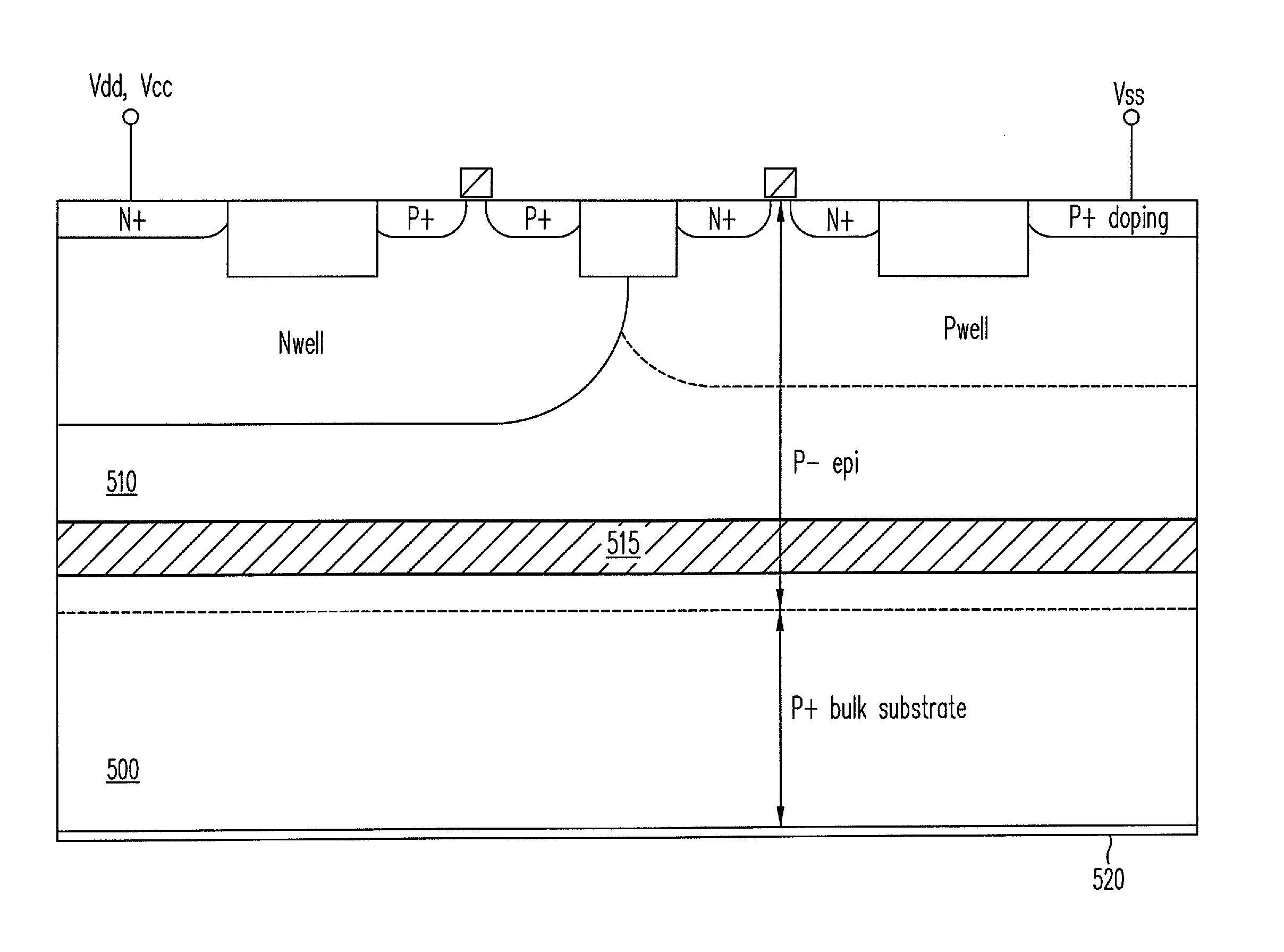

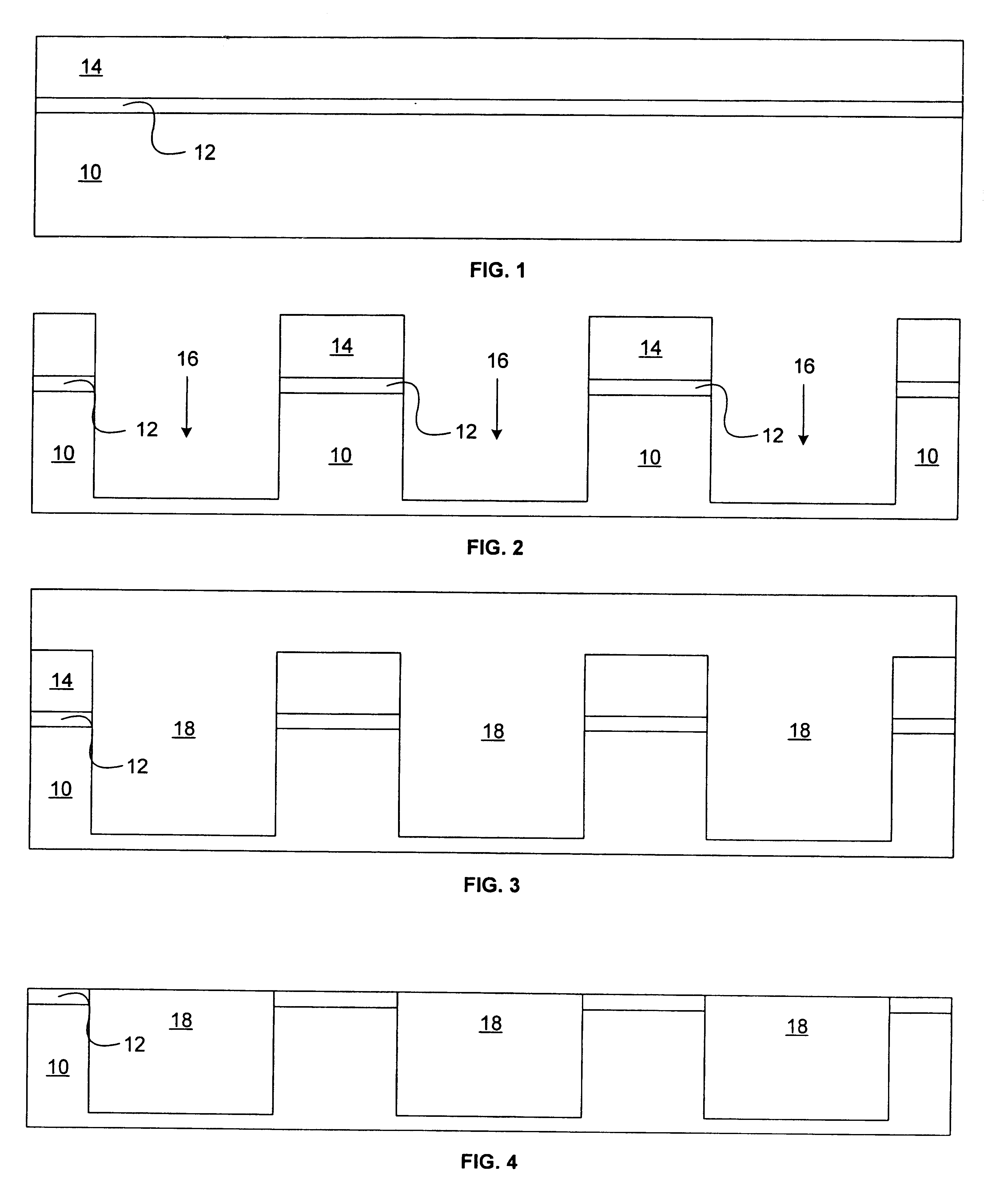

Fabrication methods for radiation hardened isolation structures

ActiveUS20100267212A1Reduce and eliminate effectLow costSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Semiconductor devices can be fabricated using conventional designs and process but including specialized structures to reduce or eliminate detrimental effects caused by various forms of radiation. Such semiconductor devices can include one or more parasitic isolation devices and / or buried layer structures disclosed in the present application. The introduction of design and / or process steps to accommodate these novel structures is compatible with conventional CMOS fabrication processes, and can therefore be accomplished at relatively low cost and with relative simplicity.

Owner:SILICON SPACE TECH

High performance, low power vertical integrated CMOS devices

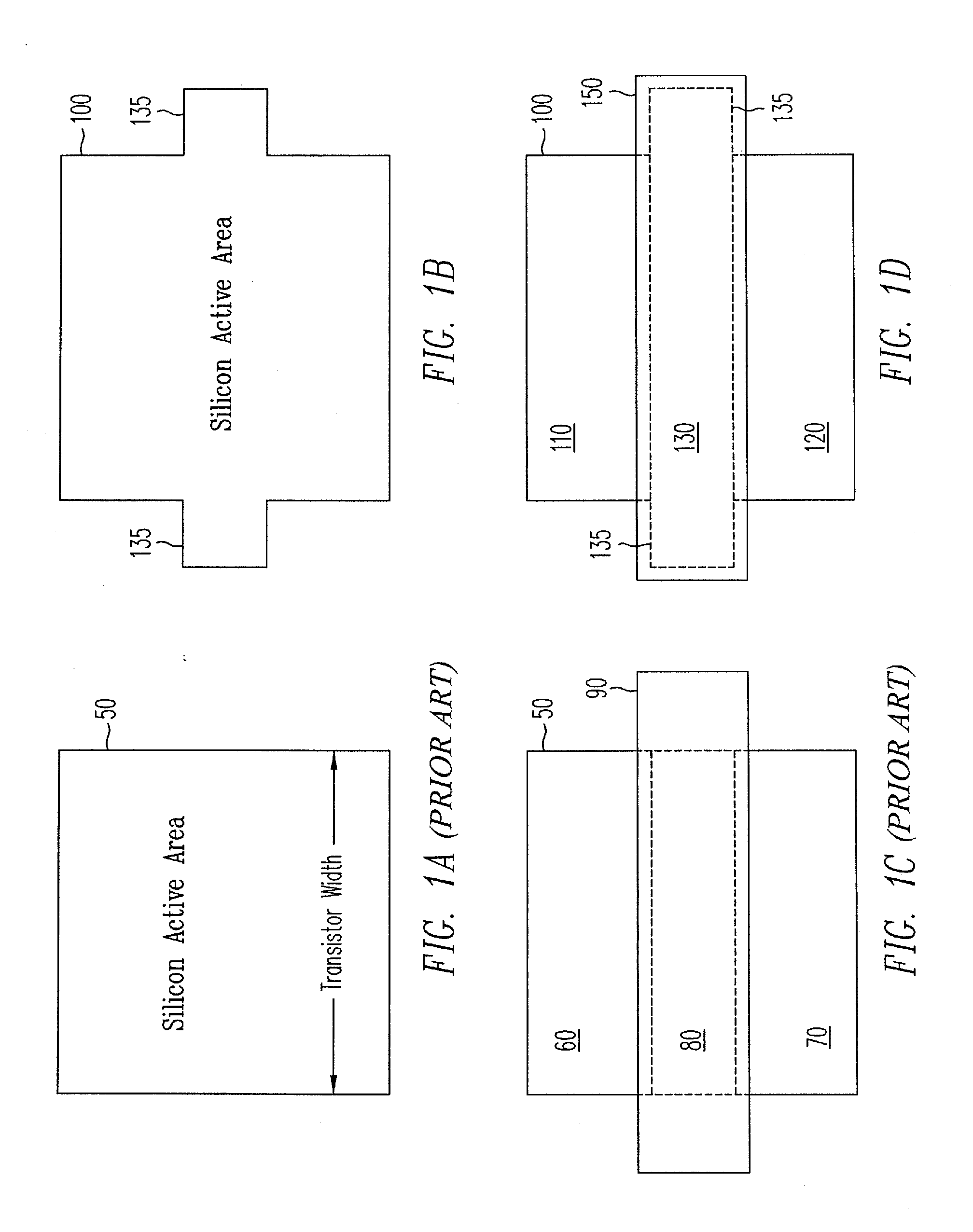

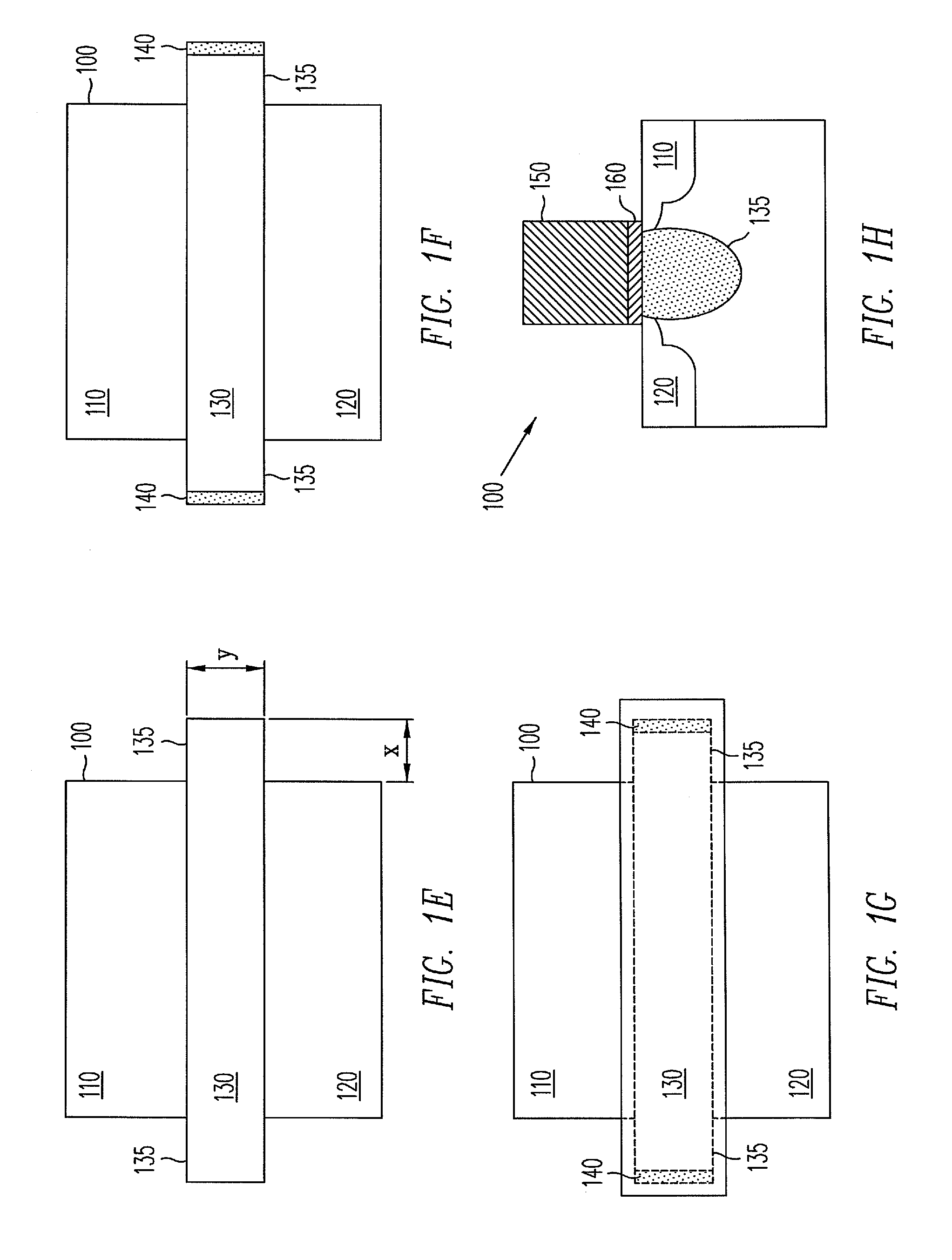

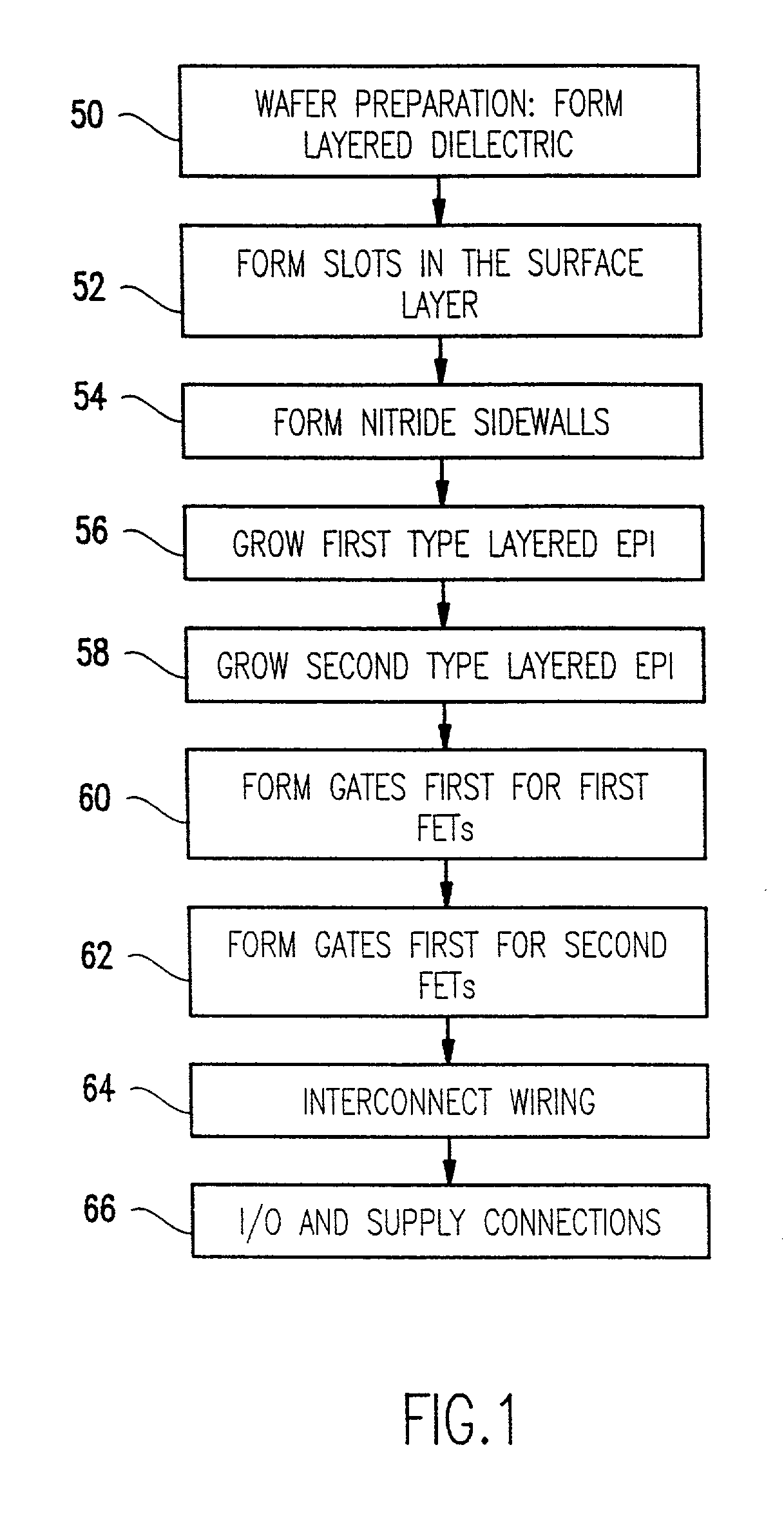

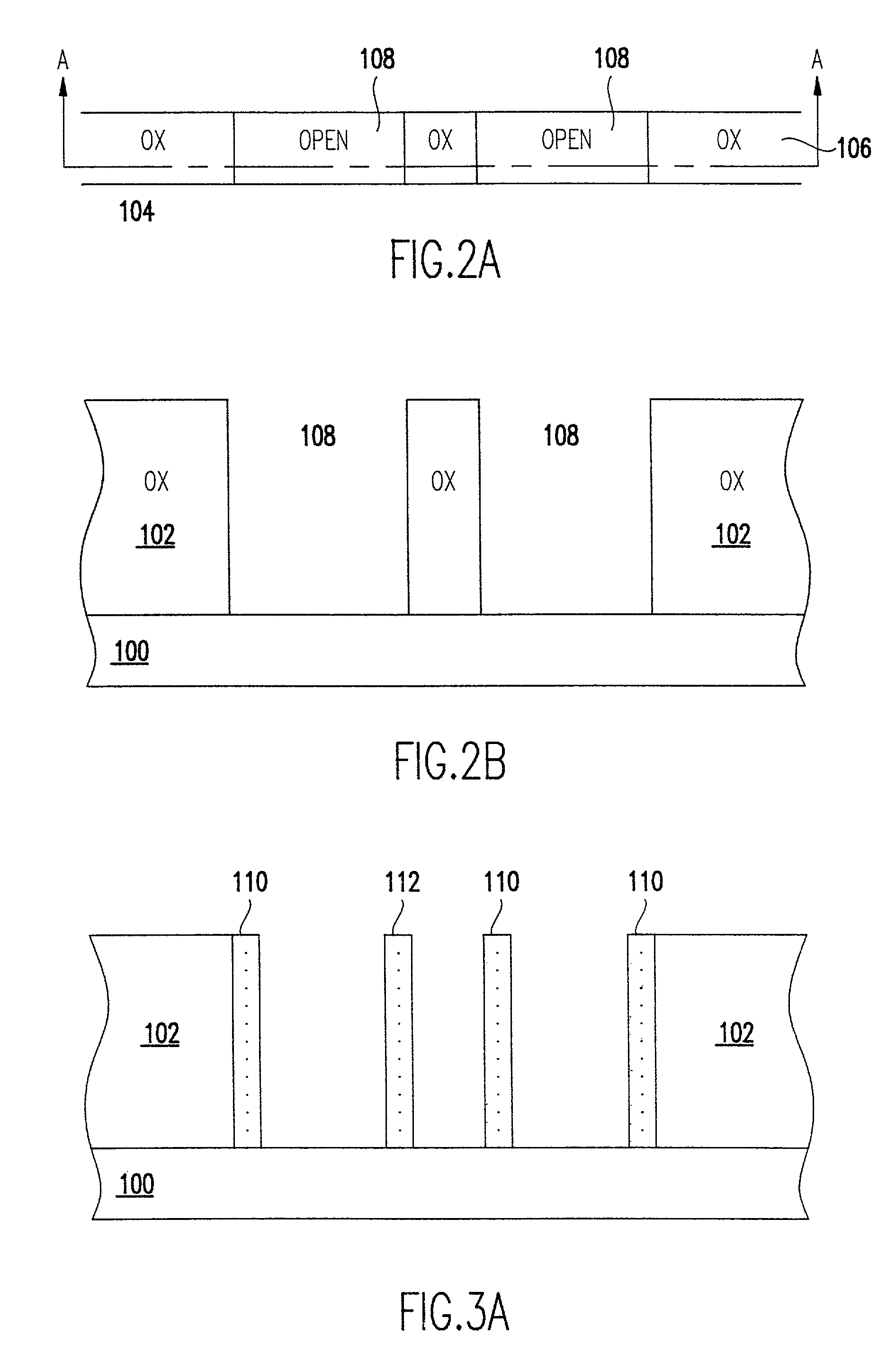

A vertical Field Effect Transistor (FET) that may be an N-type FET (NFET) or a P-type FET (PFET); a multi-device vertical structure that may be two or more NFETs or two or more PFETS; logic gates including at least one vertical FET or at least one multi-device vertical; a Static Random Access Memory (SRAM) cell and array including at least one vertical FET; a memory array including at least one such SRAM cell; and the process of forming the vertical FET structure, the vertical multi-device (multi-FET) structure, the logic gates and the SRAM cell. The vertical FETs are epitaxially grown layered stacks of NPN or PNP with the side of a polysilicon gate layer adjacent the device's channel layer. The multi-FET structure may be formed by forming sides of two or more gates adjacent to the same channel layer or, by forming multiple channel layers in the same stack, e.g., PNPNP or NPNPN, each with its own gate, i.e., the side of a polysilicon gate layer. The SRAM cell may be radiation hardened by selectively thickening gate layers to increase storage node capacitance, providing high resistance cell wiring or by including a multi-layered gate oxide layer of NO or ONO, or by any combination thereof.

Owner:IBM CORP

Analytical laser ablation of solid samples for ICP, ICP-MS, and FAG-MS analysis

InactiveUS8274735B2Eliminate chromatic aberrationMirrorsAnalysis by thermal excitationMolecular analysisPath length

The present invention facilitates improvements in laser ablation of solid samples to be analyzed by an external inductively coupled plasma (ICP) emission spectrometer, ICP / mass-spectrometer (ICP-MS), or flowing afterglow (FAG) mass spectrometer (FAG-MS) for elemental analysis (ICP and ICP-MS) or molecular analysis (FAG-MS). A novel invention mirror-with-hole beam combiner eliminates chromatic aberration in the invention sample view and allows rad-hardening the laser ablation invention for use in a radiation hot cell for analysis of high activity nuclear waste. Many other novel invention rad-hardening attributes facilitate a comprehensive rad-hardened laser ablation system (the world's first). In other embodiments, invention novelties include unusually large homogeneous focused laser spot diameters, unusually long laser objective lens focal length, wide range operationally variable laser path length with built-in re-alignment, operationally variable demagnification ratio and diameter of the focused laser spot, the use of significantly higher powered SMR lasers in a large spot diameter to facilitate high sensitivity bulk analysis of solid samples, a demountable and gravitationally self-sealing stack assembly laser ablation cell, and the world's first auto-samplers (mechanized sample changers) for analytical laser ablation.

Owner:FRY ROBERT C +3

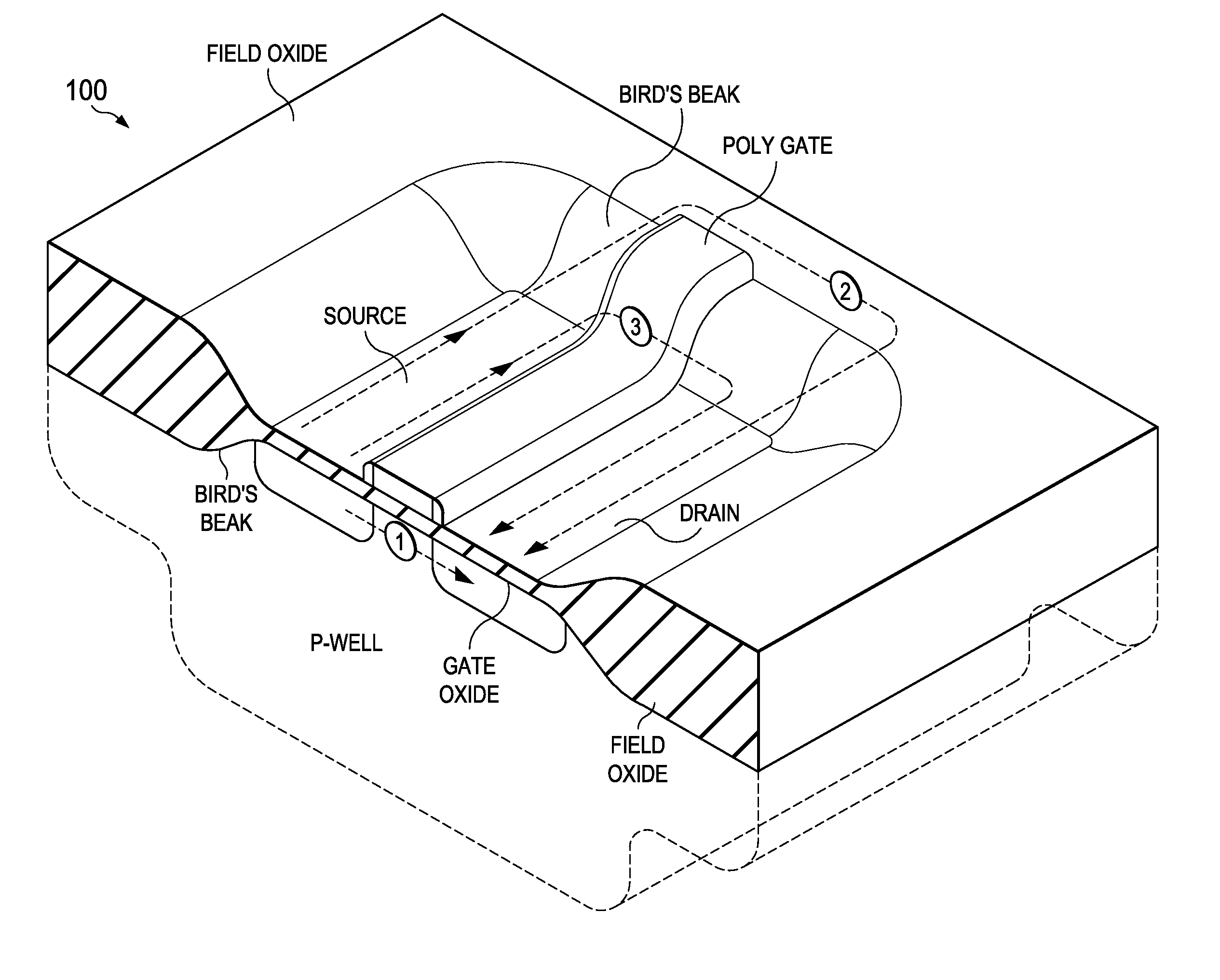

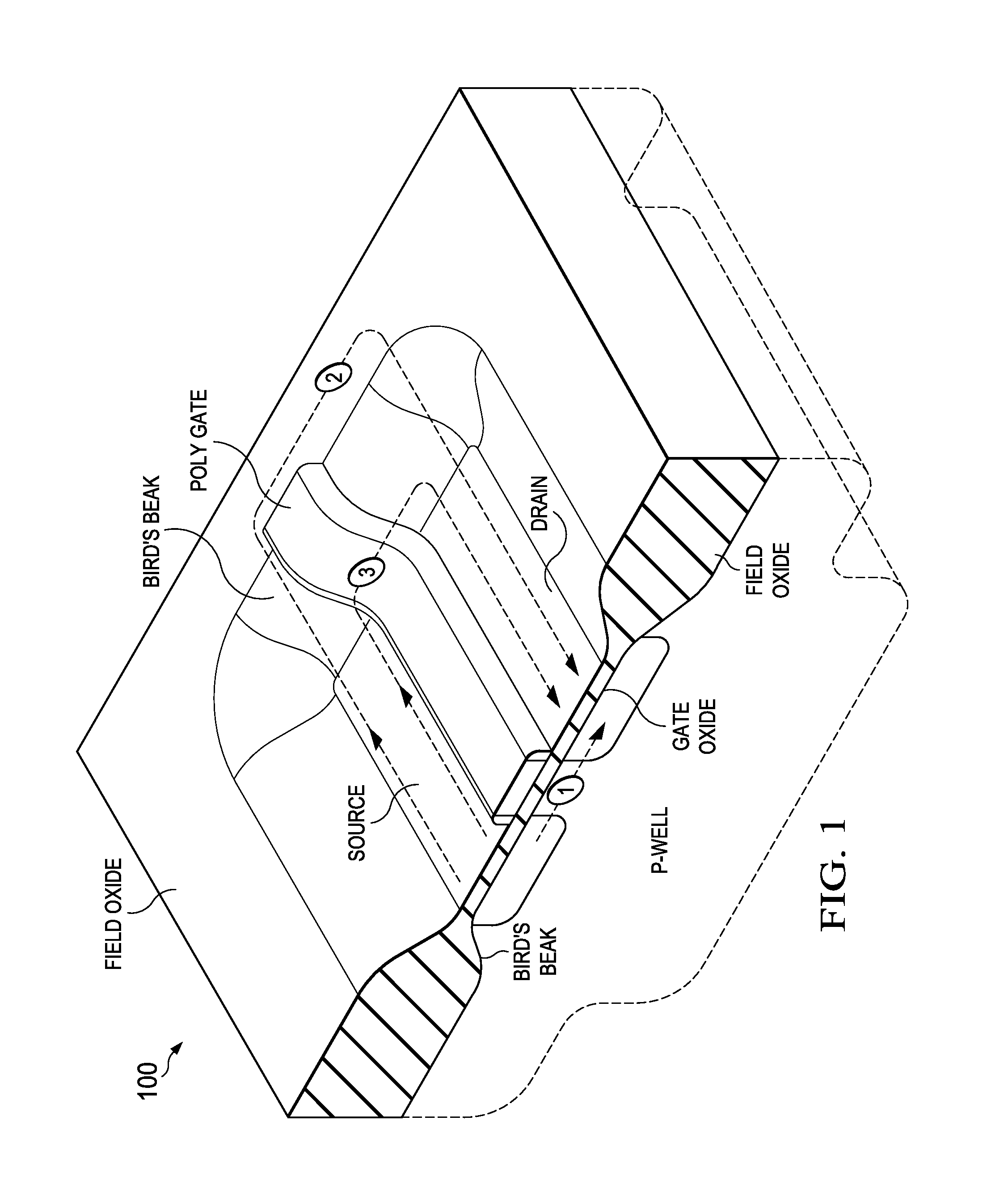

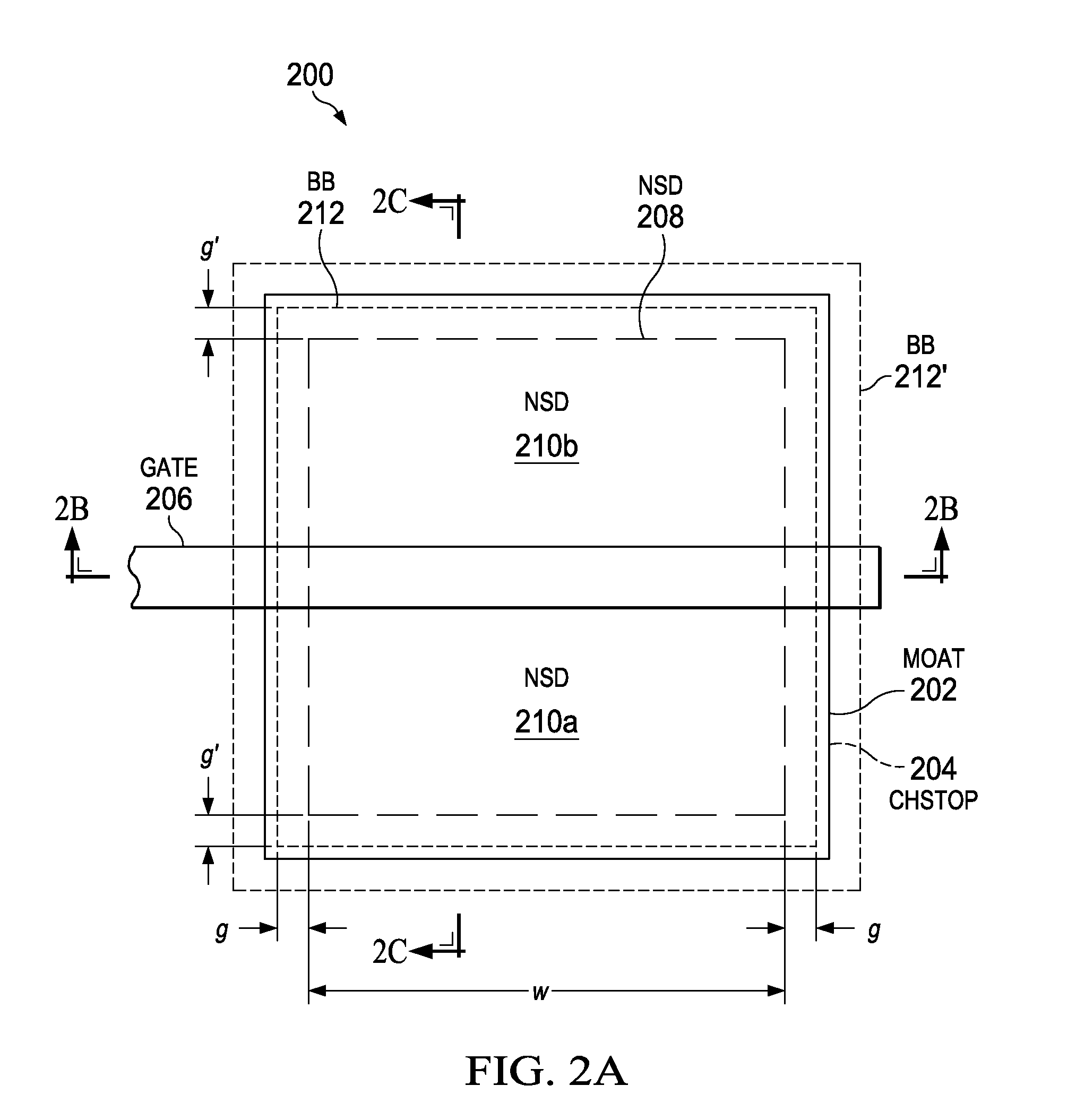

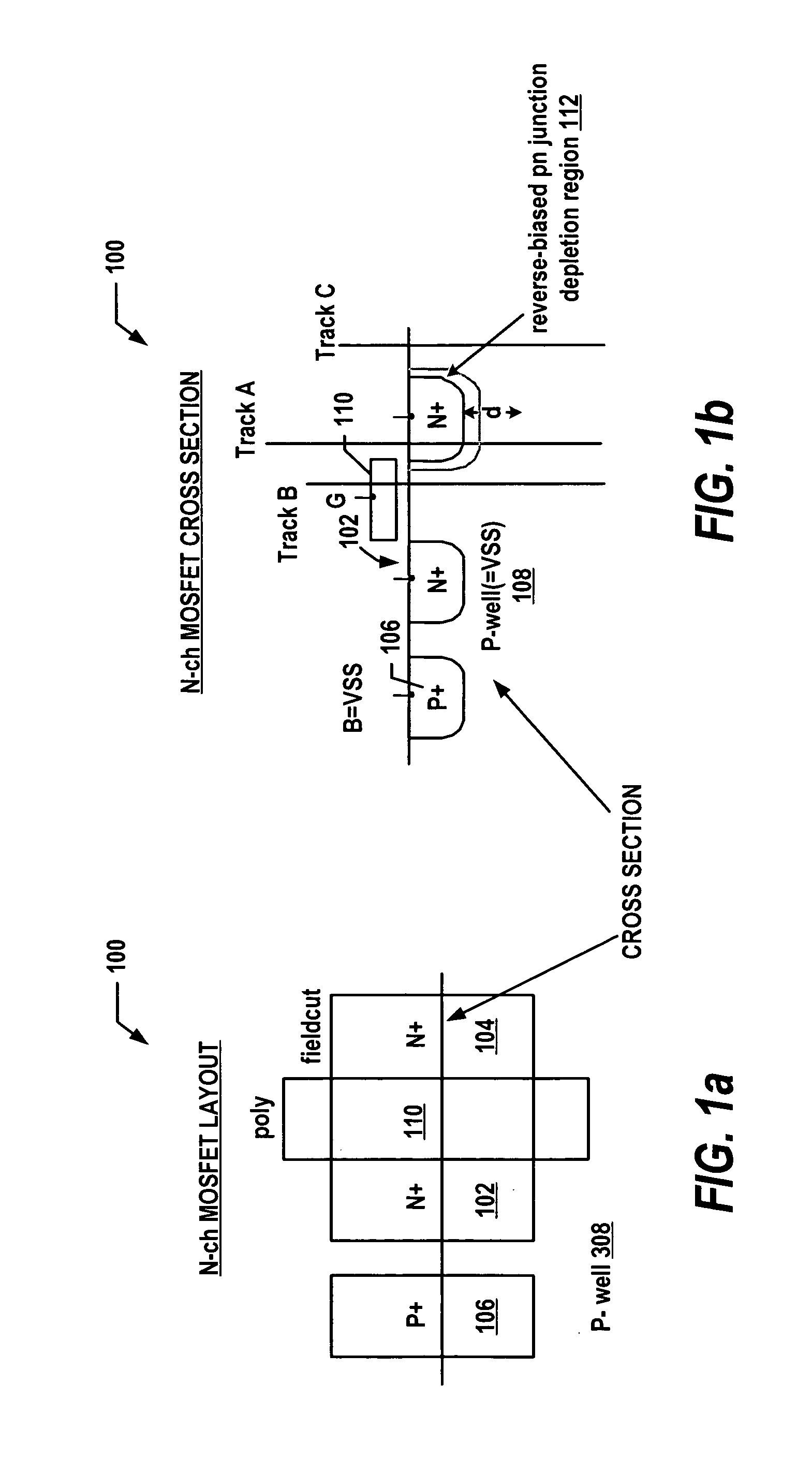

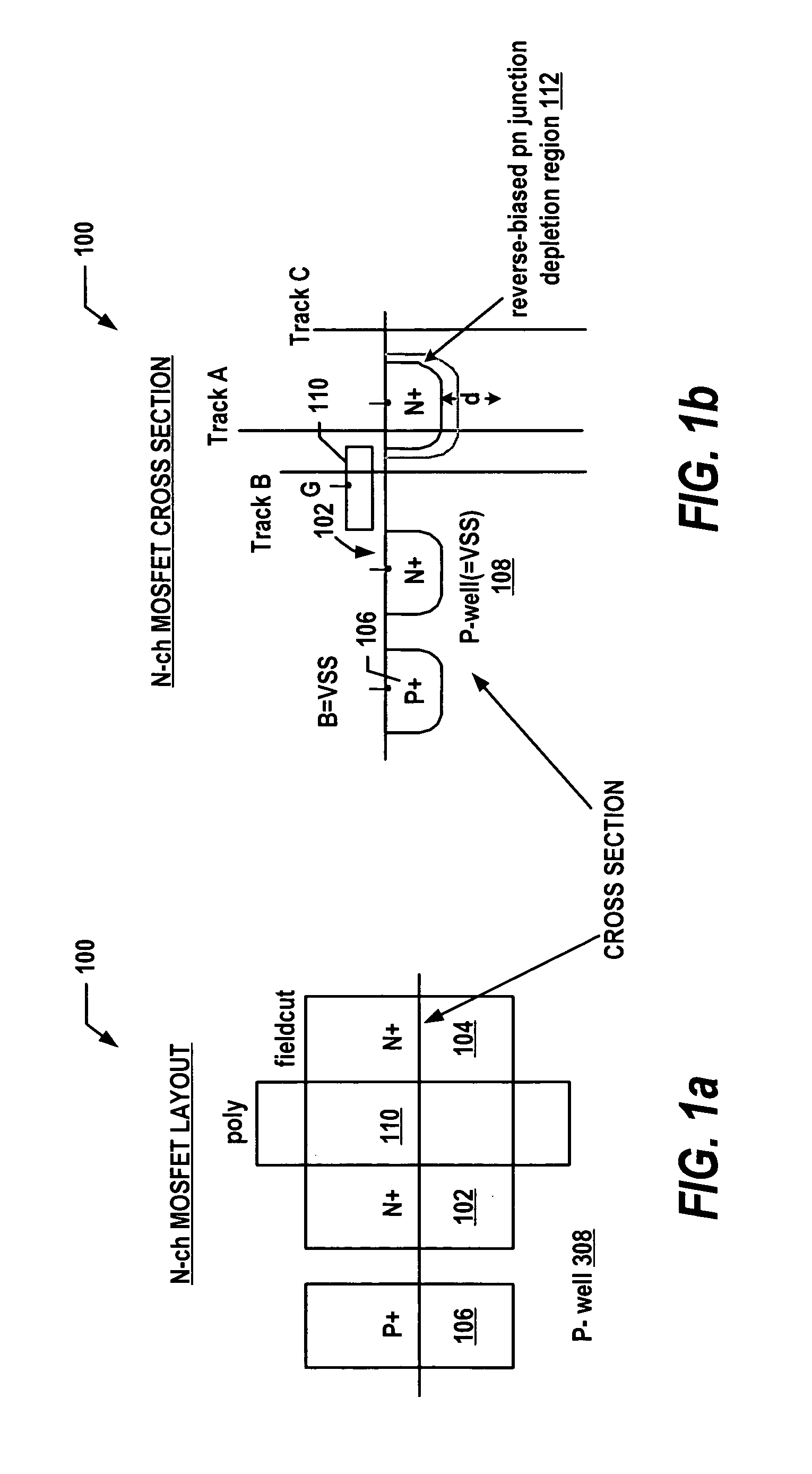

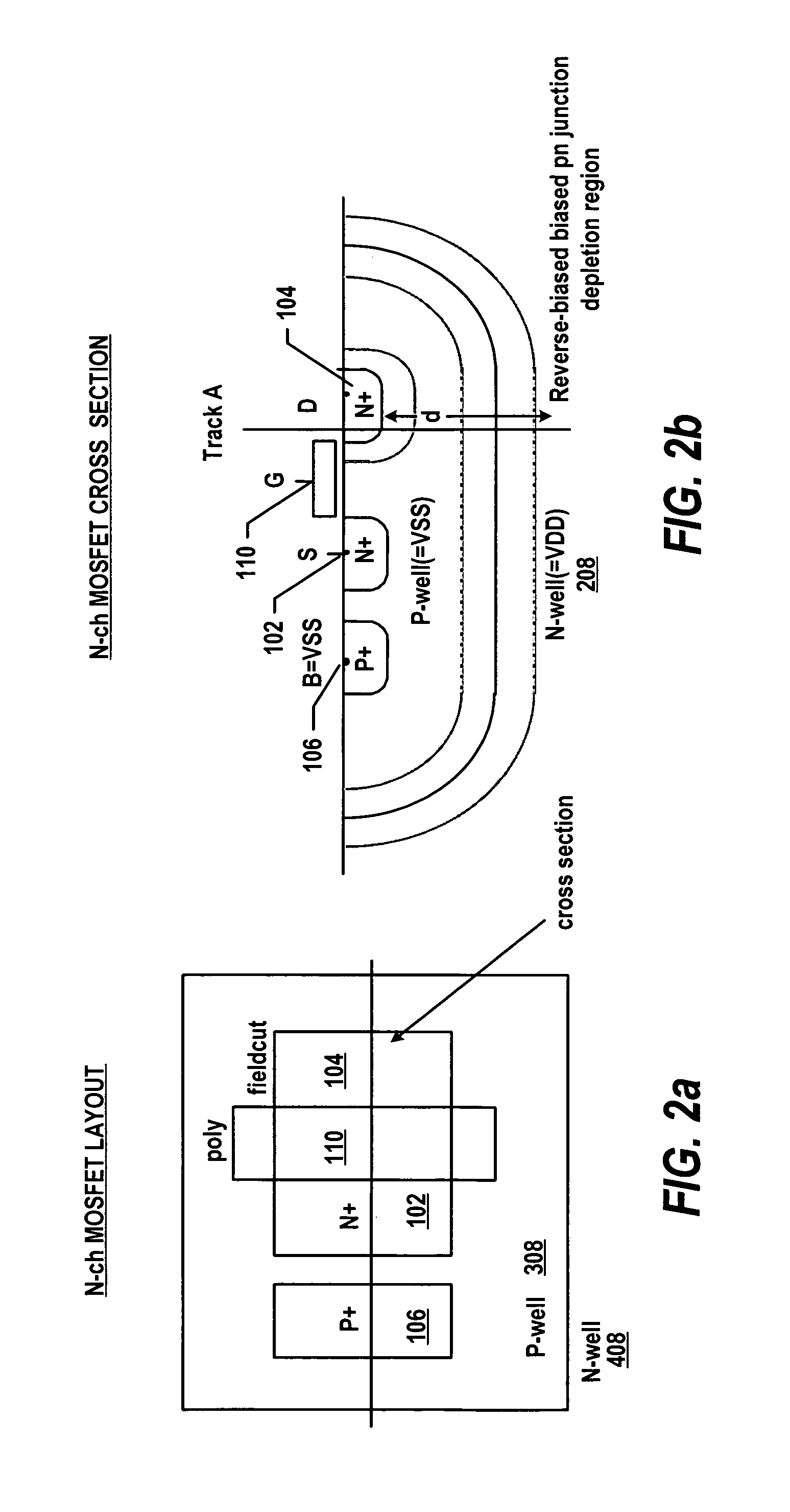

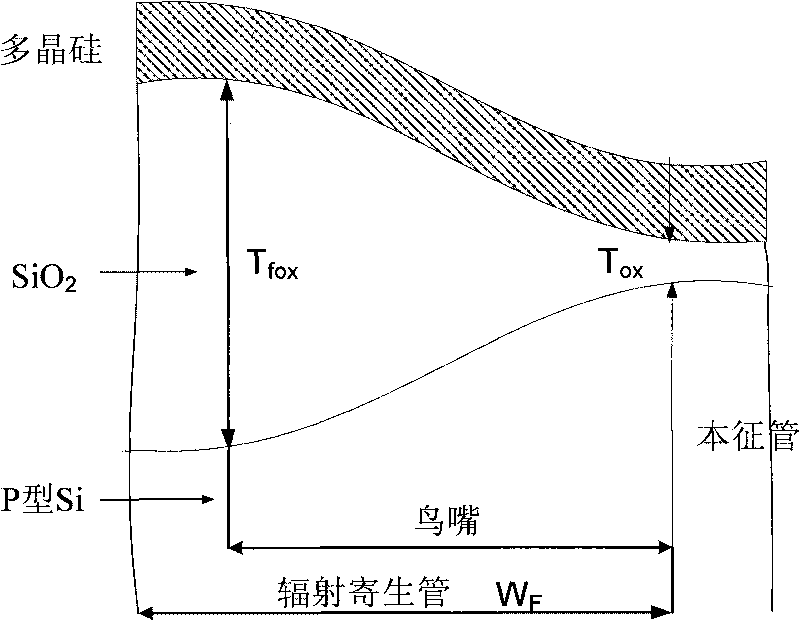

Radiation hardened mos devices and methods of fabrication

InactiveUS20110084324A1Improve radiation hardnessReducing radiation-induced leakageTransistorSolid-state devicesCMOSRadiation resistant

Radiation hardened NMOS devices suitable for application in NMOS, CMOS, or BiCMOS integrated circuits, and methods for fabricating them. A device includes a p-type silicon substrate, a field oxide surrounding a moat region on the substrate tapering through a bird's beak region to a gate oxide within the moat region, a heavily-doped p-type guard region underlying at least a portion of the bird's beak region and terminating at the inner edge of the bird's beak region, a gate crossing the moat region, and n-type source and drain regions spaced by a gap from the inner edge of the guard region. A variation of a local oxidation of silicon process is used with an additional bird's beak implantation mask as well as minor alterations to the conventional moat and n-type source / drain masks. The resulting devices have improved radiation tolerance while having a high breakdown voltage and minimal impact on circuit density.

Owner:TEXAS INSTR INC

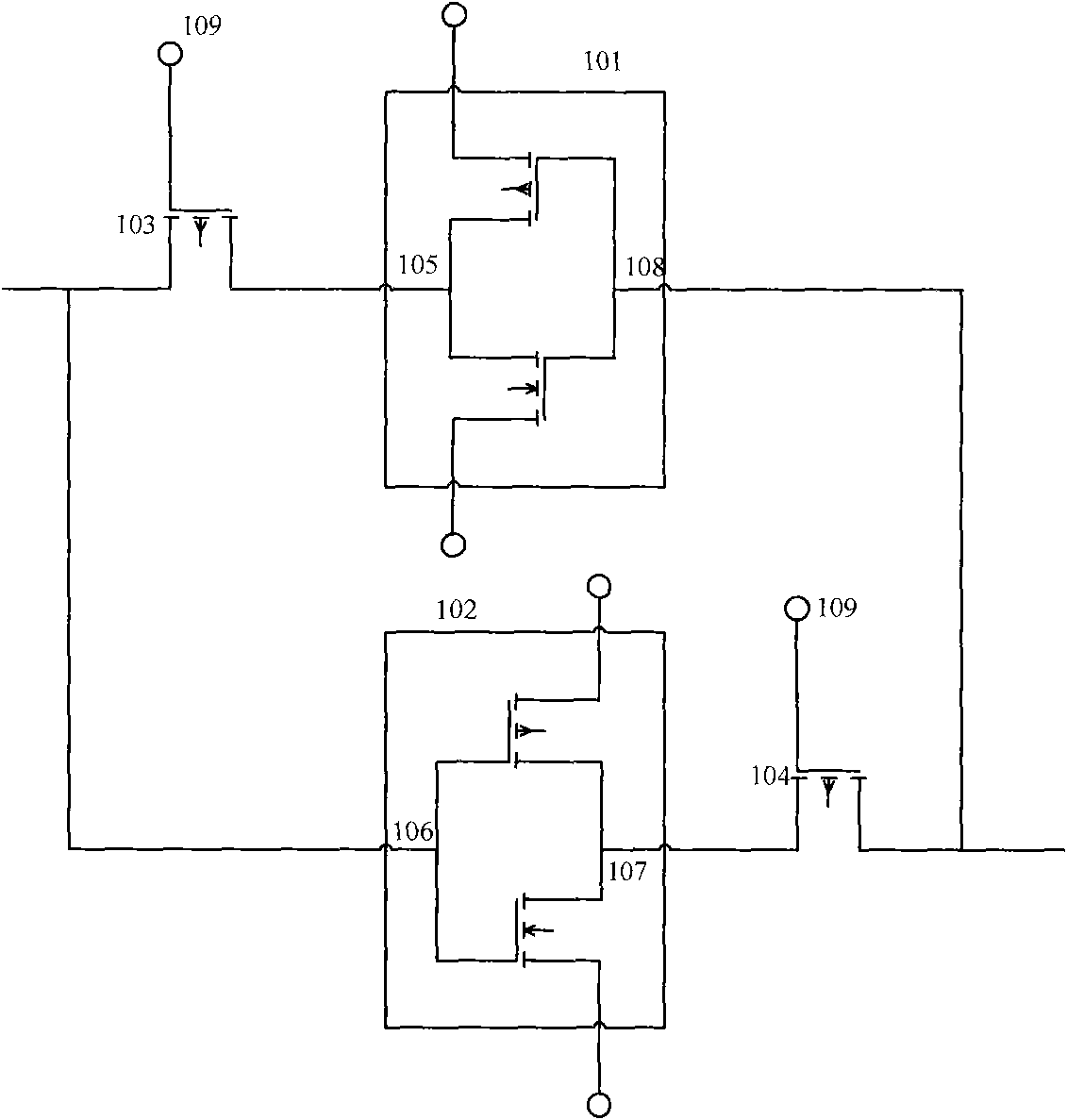

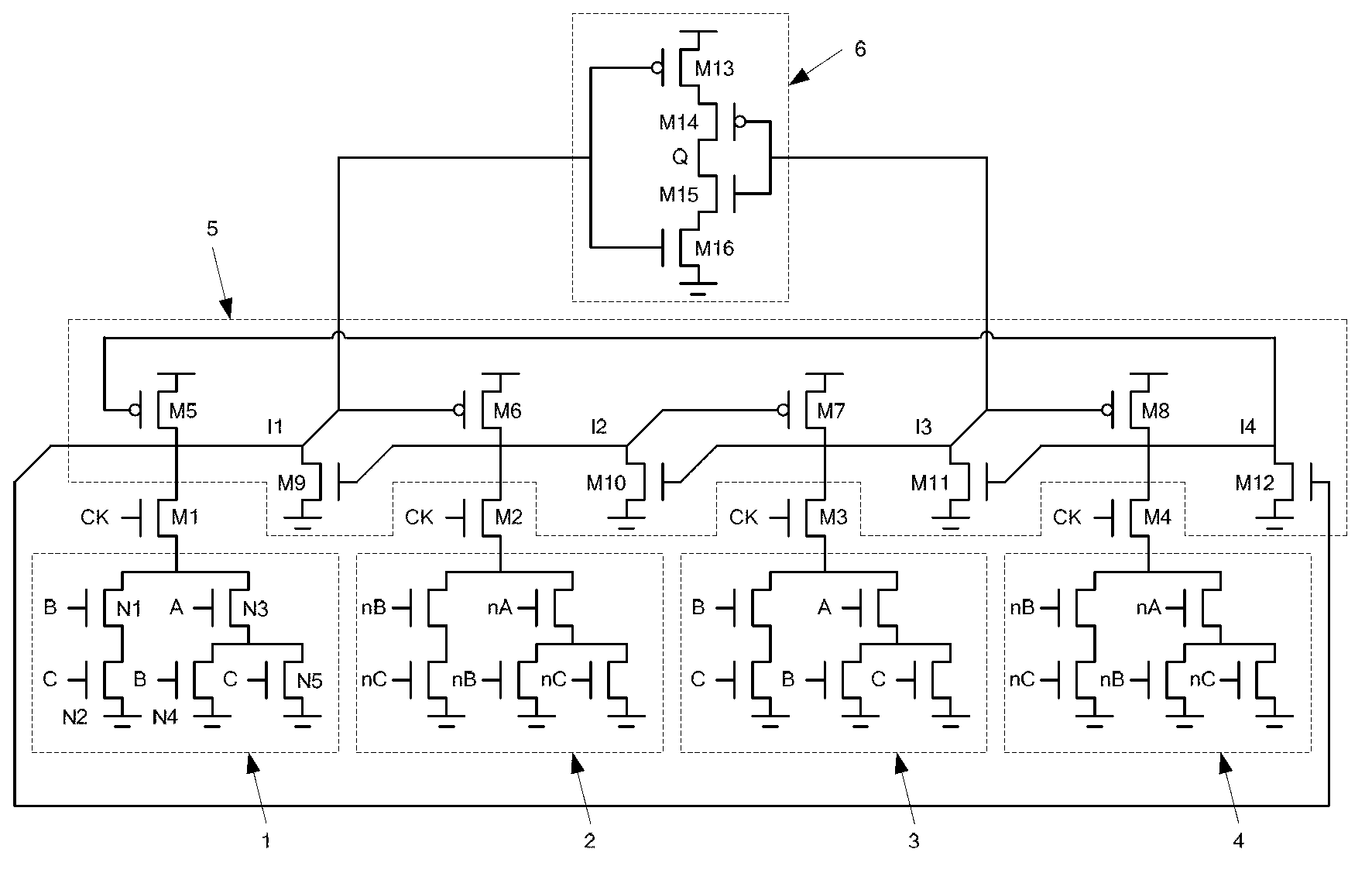

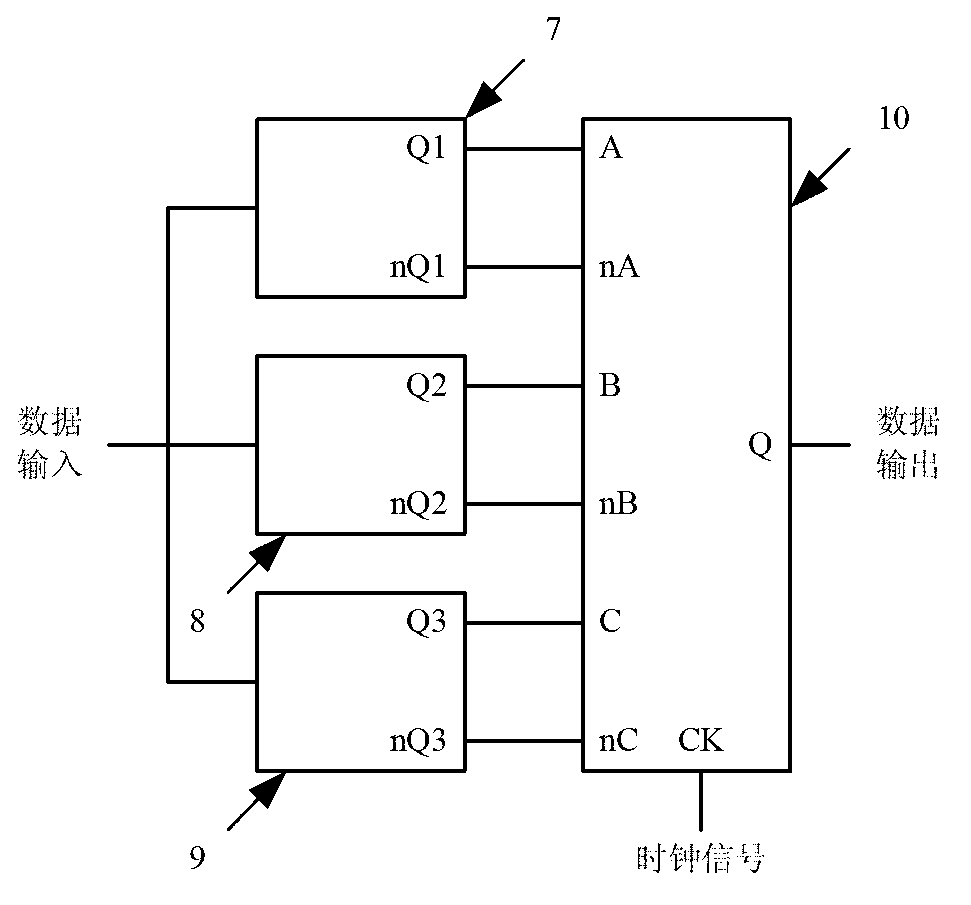

An anti-SEU storage cell circuit in an anti-radiation hardening FPGA chip

InactiveCN101552034AIncrease current pulse timeImprove Flip EffectDigital storageElectrical resistance and conductanceCross connection

The anti-SEU storage cell circuit in an anti-radiation hardening FPGA chip includes two inverters and two transistors. The two inverters are cross connected and realize the adjustment to the resistance values at the source terminals and drain terminals of the two transistors through controlling the grid voltage and substrate potential of the two transistors. The resistance values are not greater than 50 omega or not smaller than 1,000 omega. With respect to inverter design, a resistor is added to the existing circuit consisting of PMOS tube and NMOS tube. The resistor is connected between the drain terminals of PMOS transistor and NMOS transistor. Through adding a resistor into the inverter, the present invention realizes anti-SEU (single event upset) of the storage cell. Moreover, the storage circuit of the present invention has the following advantages: small noise, low power consumption, small area occupied, and easy realization of layout and process in the design of anti-radiation hardening FPGA chip.

Owner:BEIJING MXTRONICS CORP +1

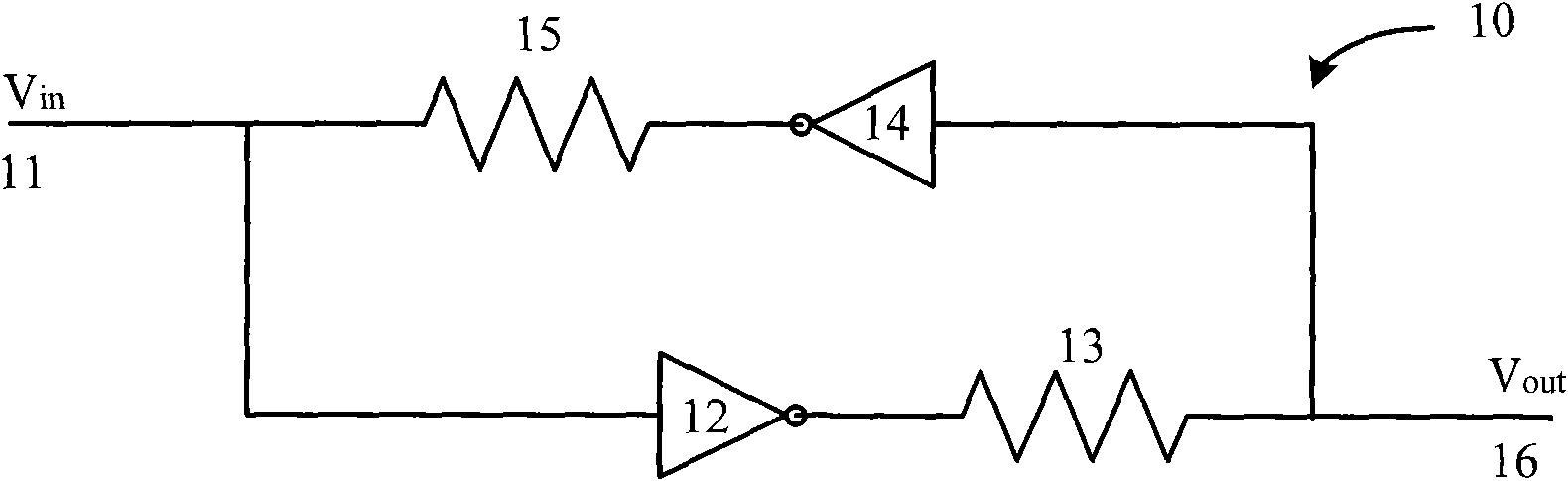

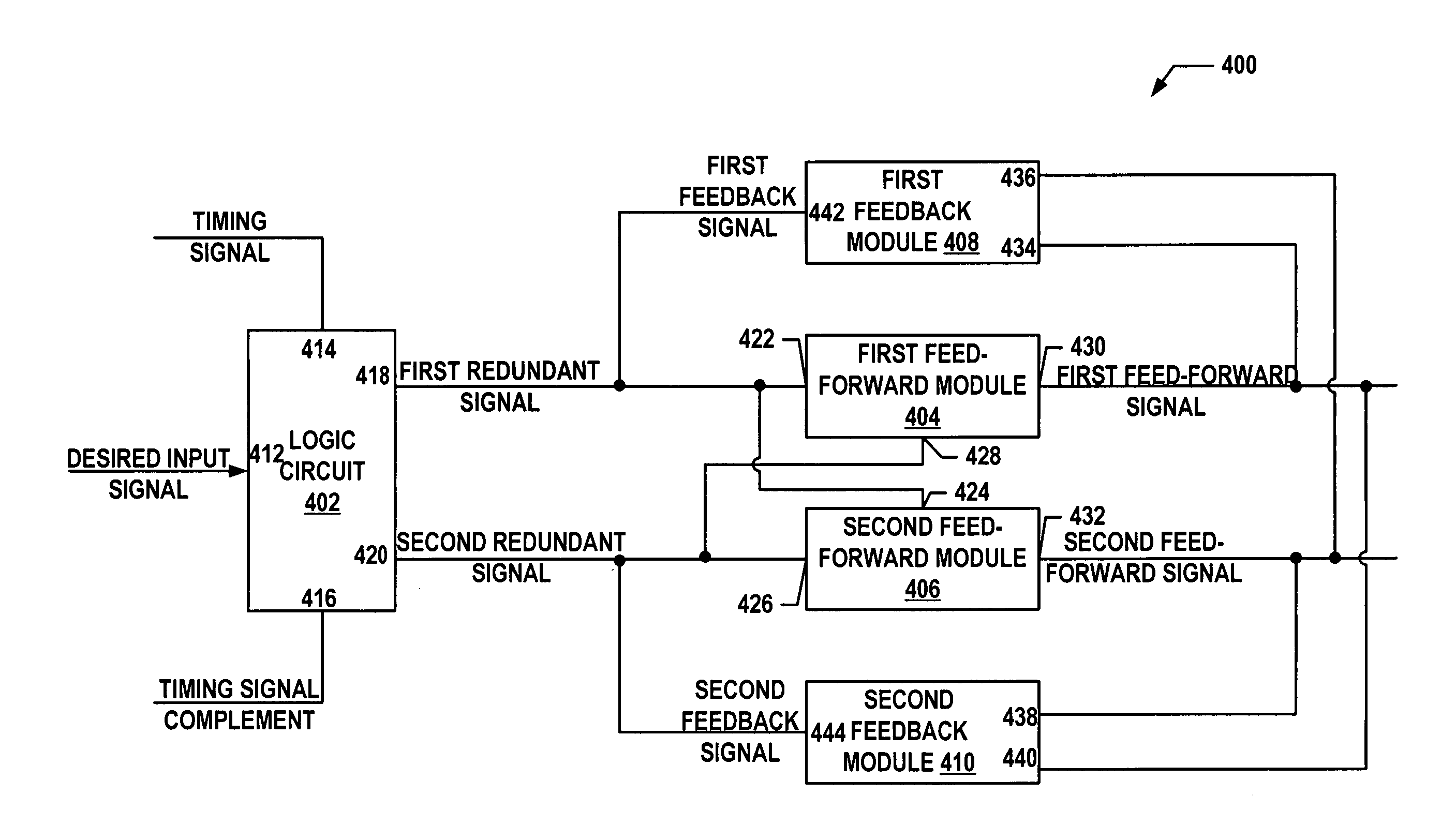

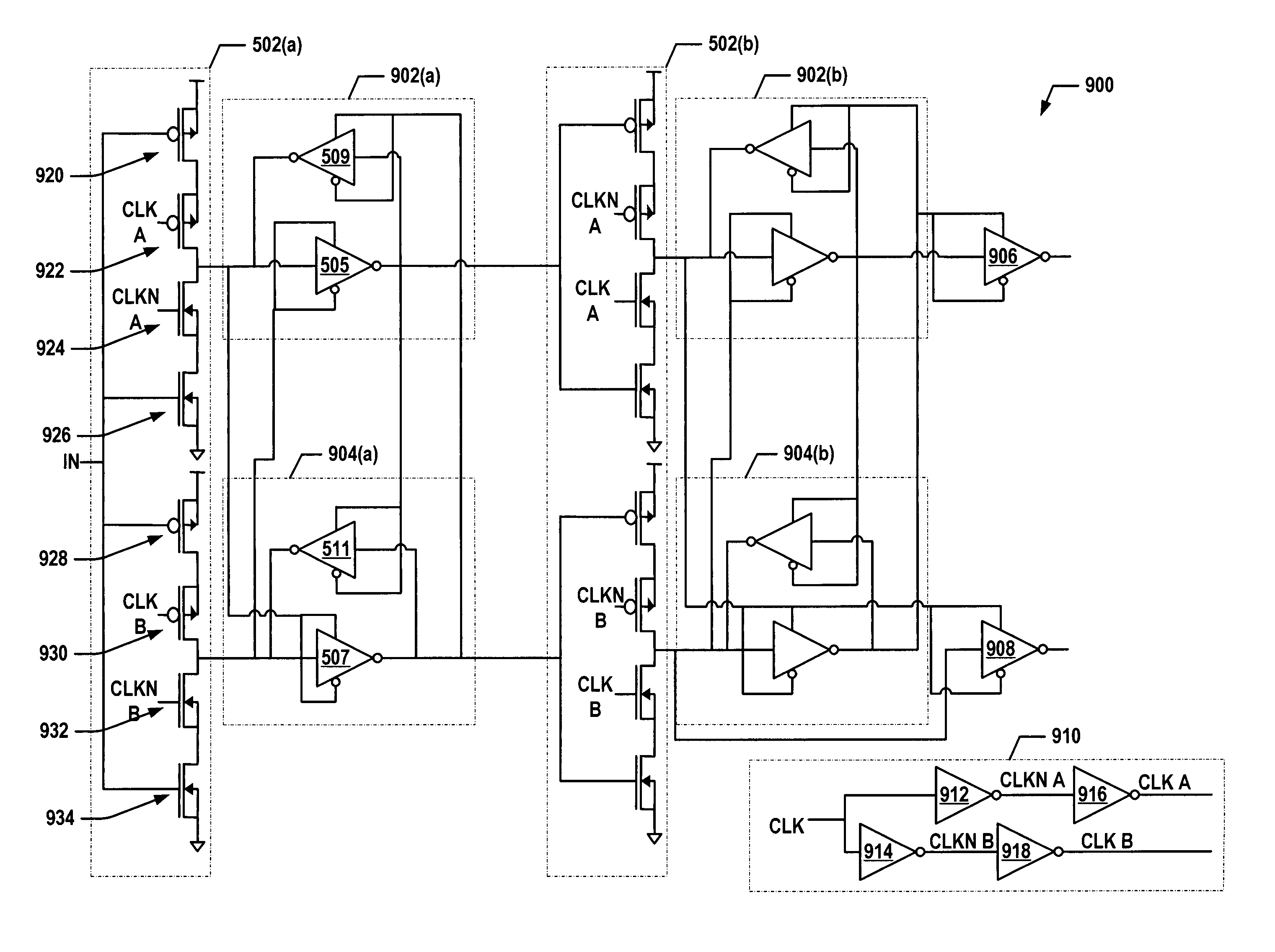

Radiation hardening of logic circuitry using a cross enabled, interlocked logic system and method

ActiveUS20050156620A1Reliability increasing modificationsFail-safe circuitsEngineeringLogic circuitry

A system and method for hardening a logic circuit against radiation-event effects is provided. The system may include a logic circuit, first and second feed-forward devices, and first and second feedback devices. The logic circuit may be operable to output independently-obtained first and second redundant signals responsive to a desired input signal. Each of the first and second feed-forward devices may receive both of the first and second redundant signals. When the first and second redundant signals are in expected states, then the first and second feed-forward devices may responsively provide respective first and second feed-forward signals. Each of the first and second feedback devices may receive both of the first and second feed-forward signals. When the first and second feed-forward signals are in expected states, then the first and second feedback devices responsively feed respective first and second feedback signals back to the respective first and second redundant signals.

Owner:HONEYWELL INT INC

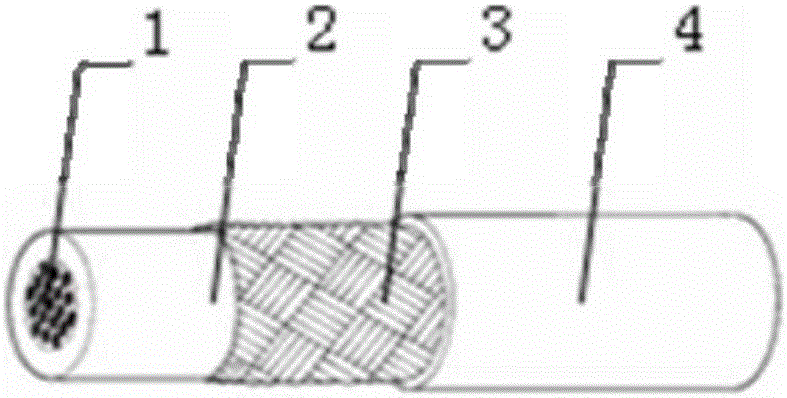

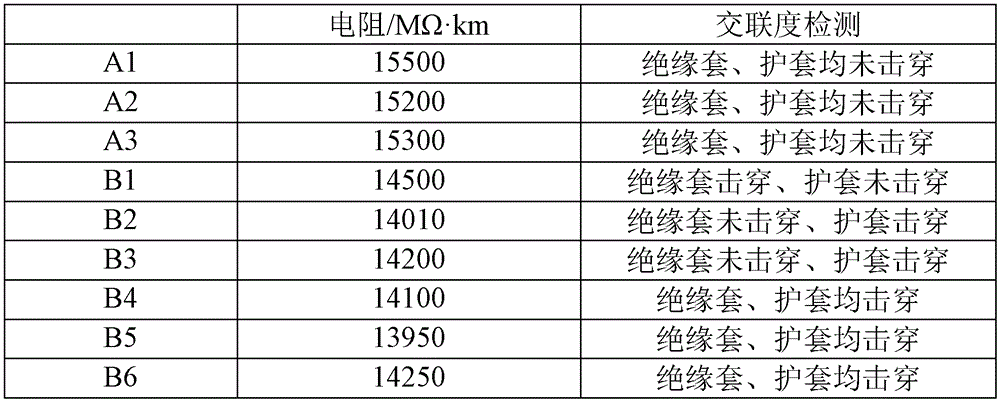

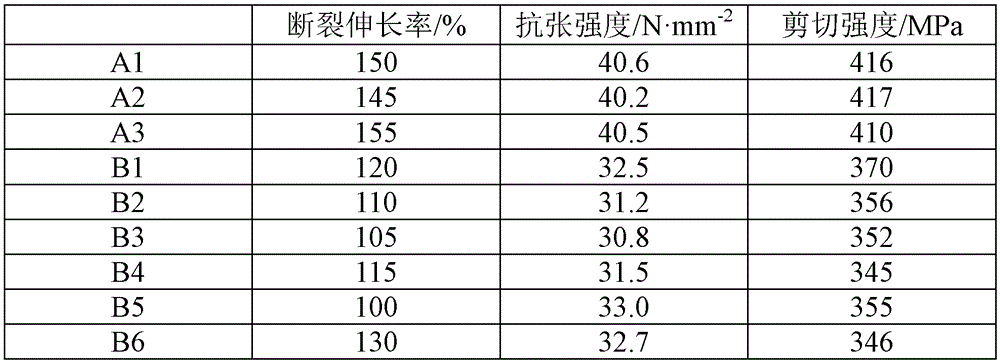

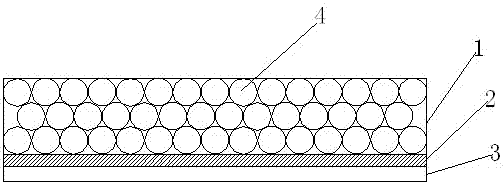

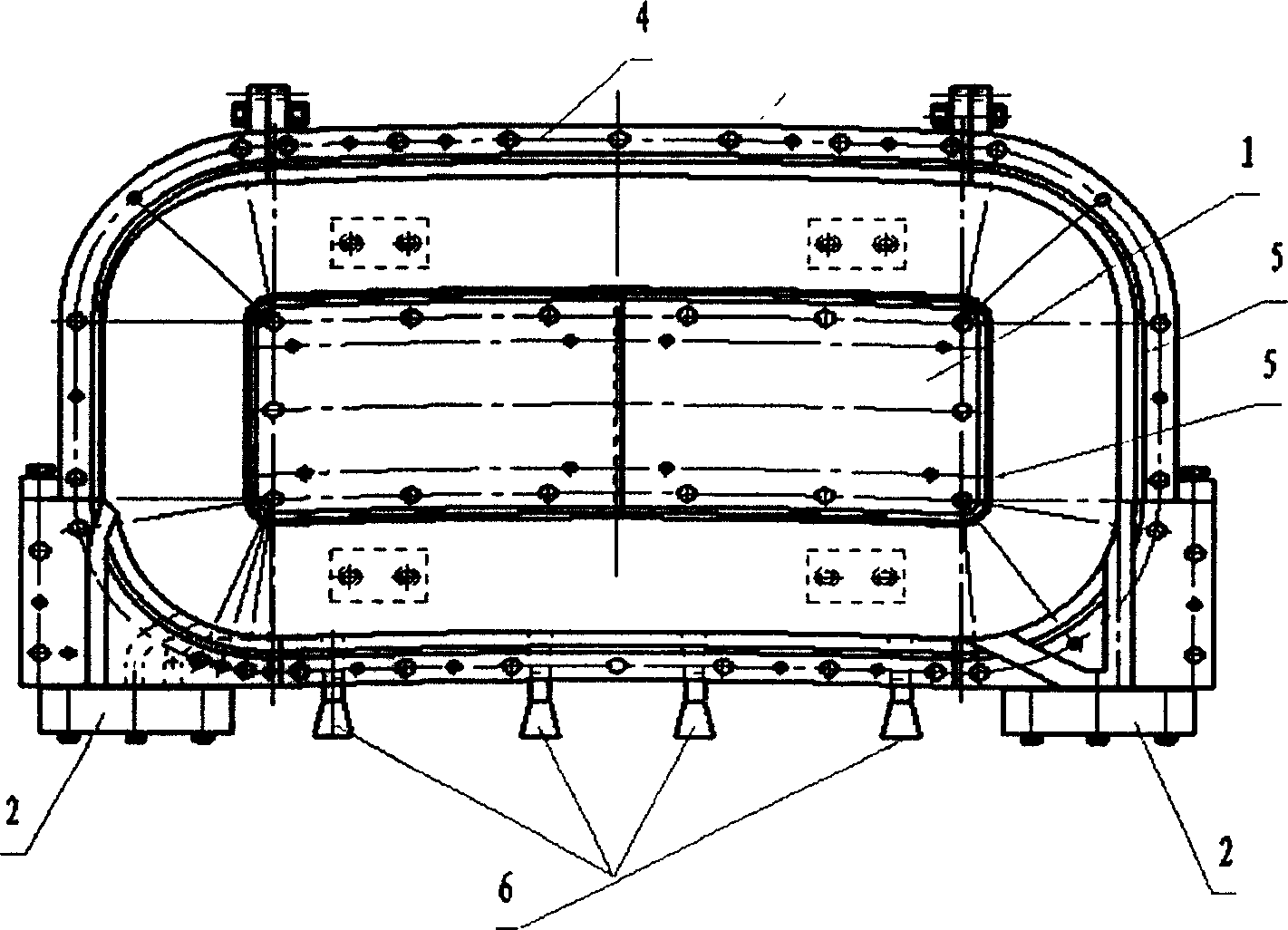

High-performance crosslinked ethylene and tetrafluoroethene copolymer insulated cable and preparation method thereof

InactiveCN105355279AImprove mechanical propertiesGood chemical stabilityInsulated cablesCable/conductor manufactureTetrafluoroethyleneEngineering

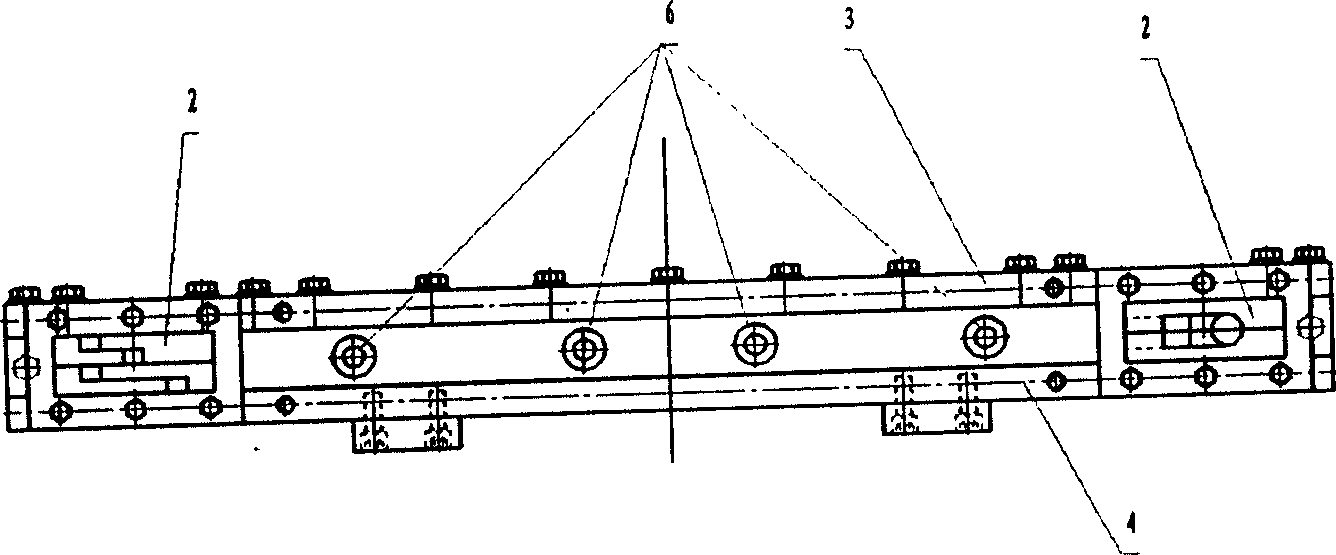

The invention discloses a high-performance crosslinked ethylene and tetrafluoroethene copolymer insulated cable and a preparation method thereof. The insulated cable comprises a lead (1), an insulation sleeve (2), a shielding sleeve (3) and a sheath (4), wherein the insulation sleeve (2), the shielding sleeve (3) and the sheath (4) sleeve the lead (1) successively from inside to outside, the insulation sleeve (2) and the sheath (4) include crosslinked ethylene and tetrafluoroethene copolymer sleeves respectively, and the shielding sleeve (3) is a silvered aramid fiber braided sleeve. The insulated cable prepared by the method is high in insulatiing, mechanical and radiation-hardening properties and is chemically stable in the vacuum environment.

Owner:WUHU HANGTIAN SPECIAL CABLE FACTORY

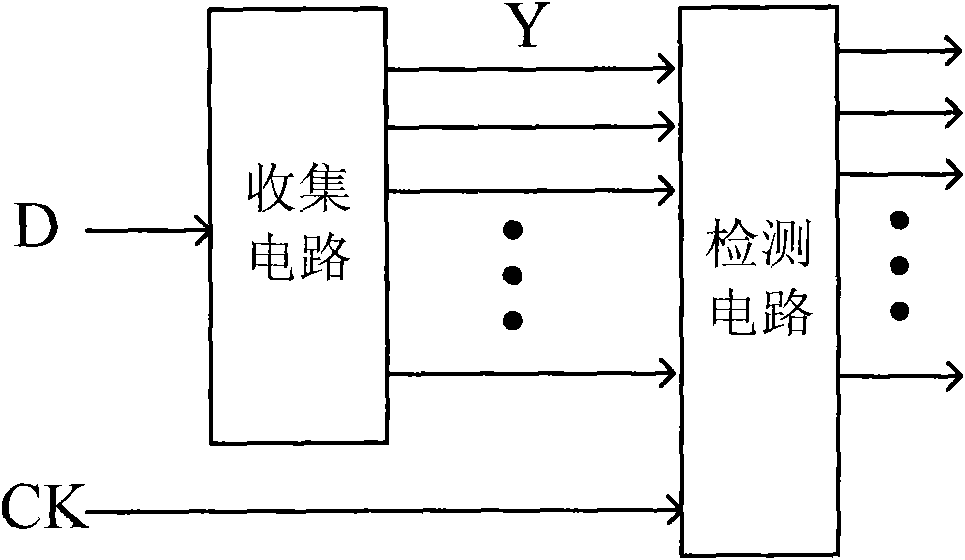

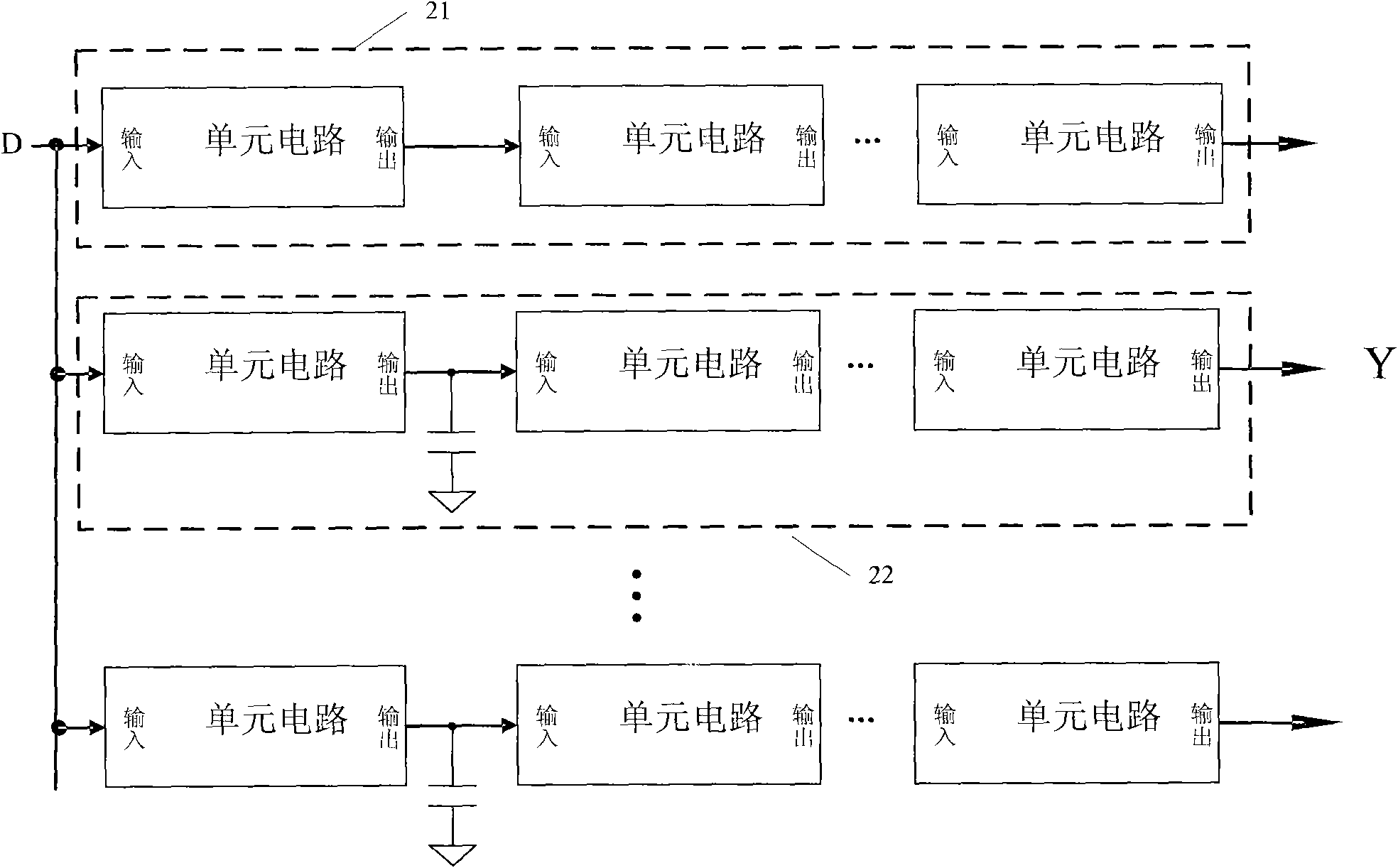

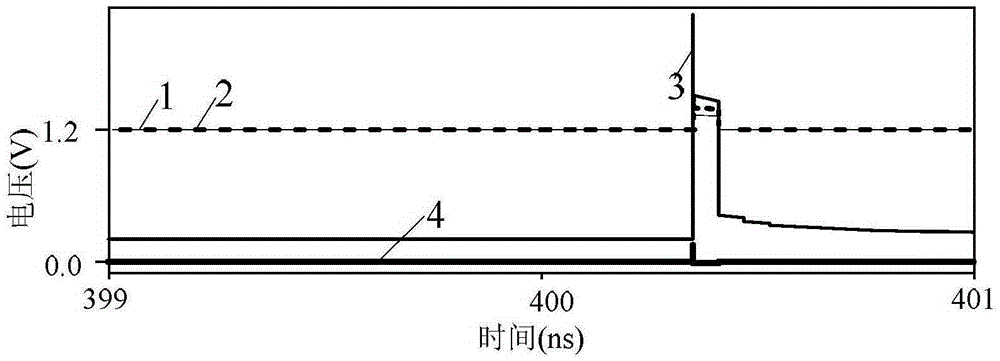

A structure of SET collecting and detecting circuit

InactiveCN101551421ADigital circuit testingPulse characteristics measurementsDigital electronicsRadiation hardening

A structure of SET collecting and detecting circuit comprises collecting circuit and detecting circuit. Level signal D outputs, through collecting circuit, N level signals Y which are in a same or reverse phase with level signal D. The event incidence into the collecting circuit triggers transient pulse of level signal Y. Under the effect of clock signal CLK, the detecting circuit captures the transient pulse. The collecting circuit has N links formed through cascading of cell circuits. The component links of the collecting circuit in the present invention reflect the states of most of the common circuit nodes in digital circuit. Through obtaining the single-event transient pulse width distribution of the circuit structure, the transient pulse status of most of the common circuit nodes in digital circuit after single-event incidence may be reflected. The present invention may be used to effectively assess the SET sensitivity of digital circuits and the processes on which digital circuits are based and provides a basis for anti-single event radiation hardening of digital circuits.

Owner:BEIJING MXTRONICS CORP +1

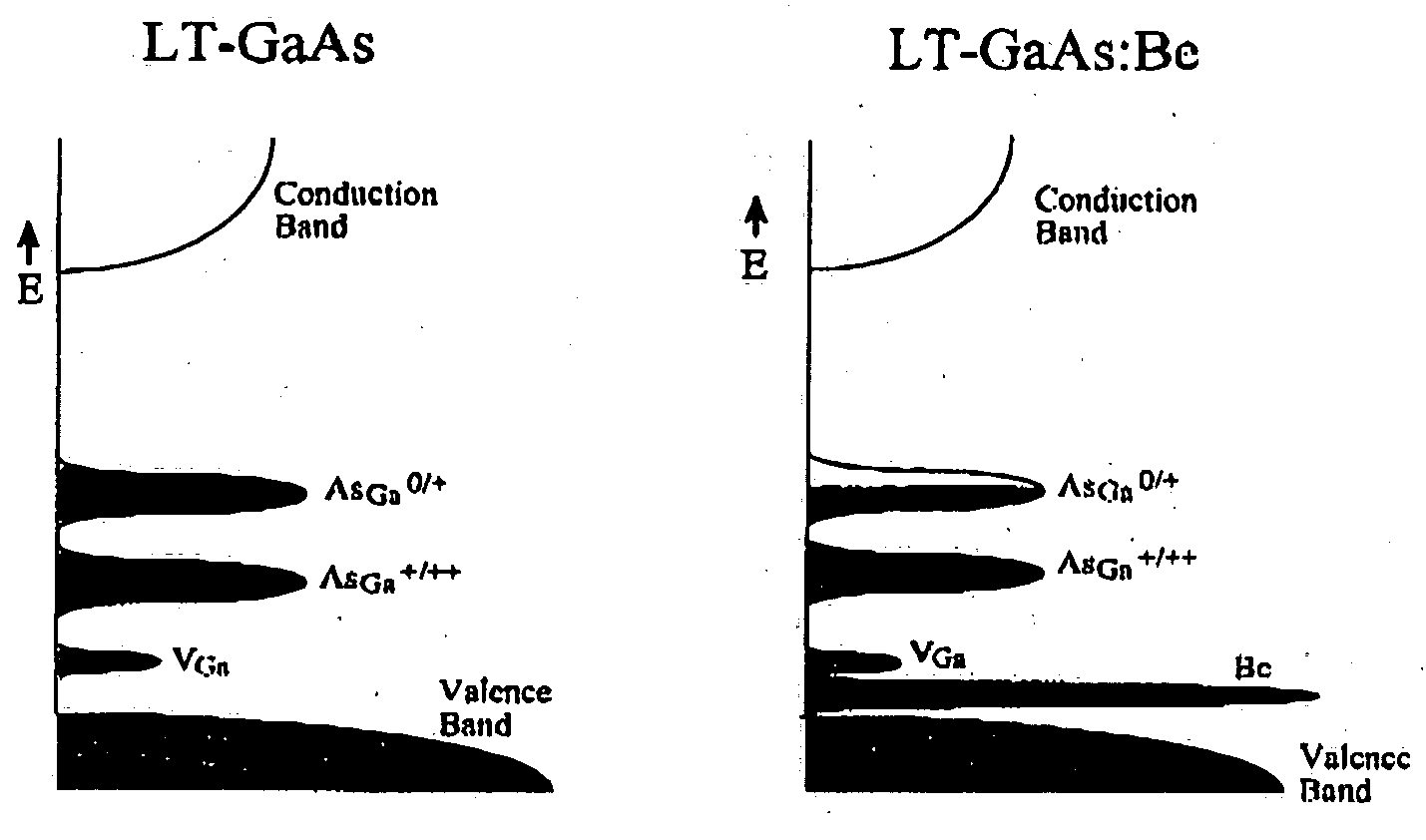

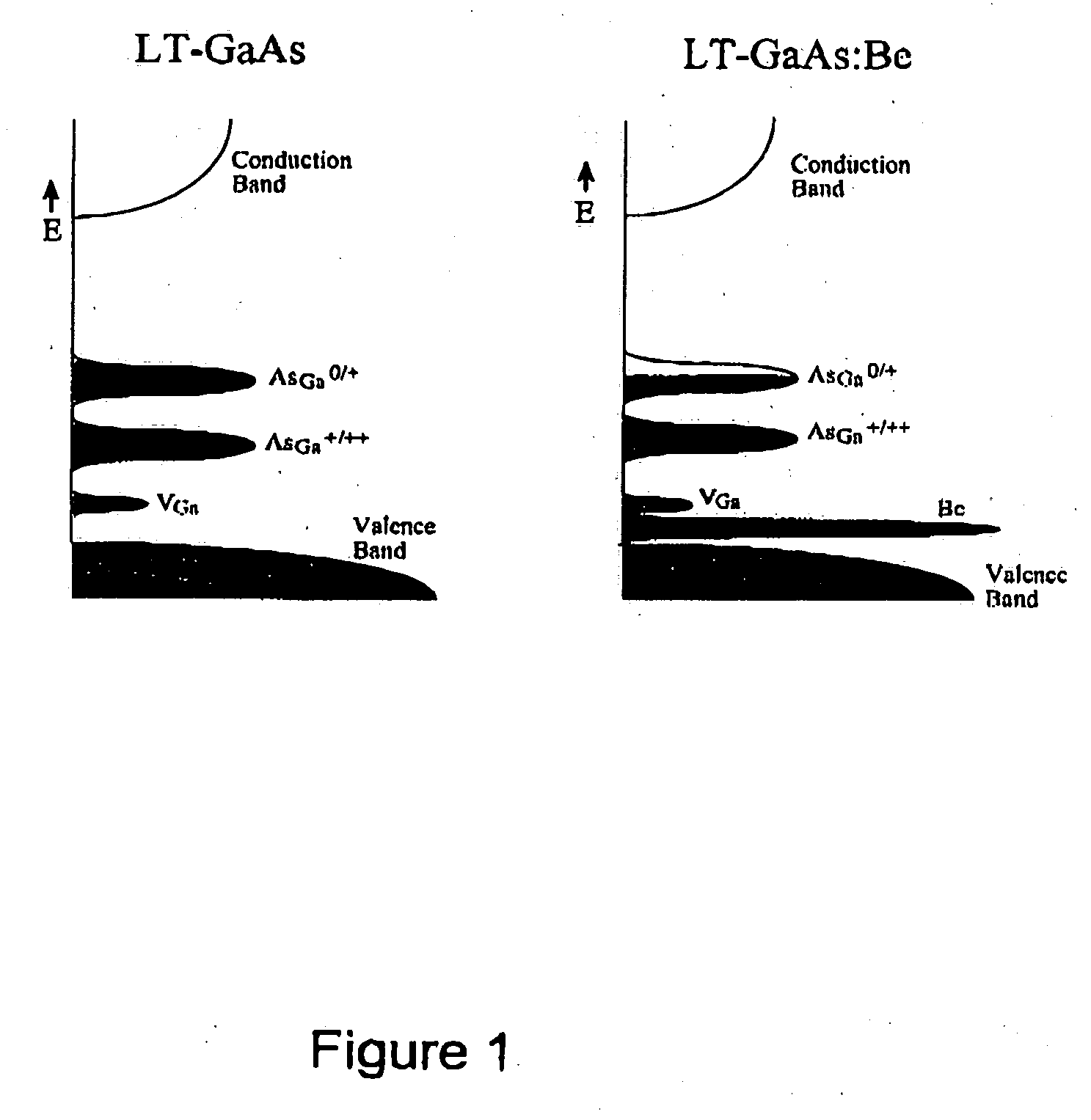

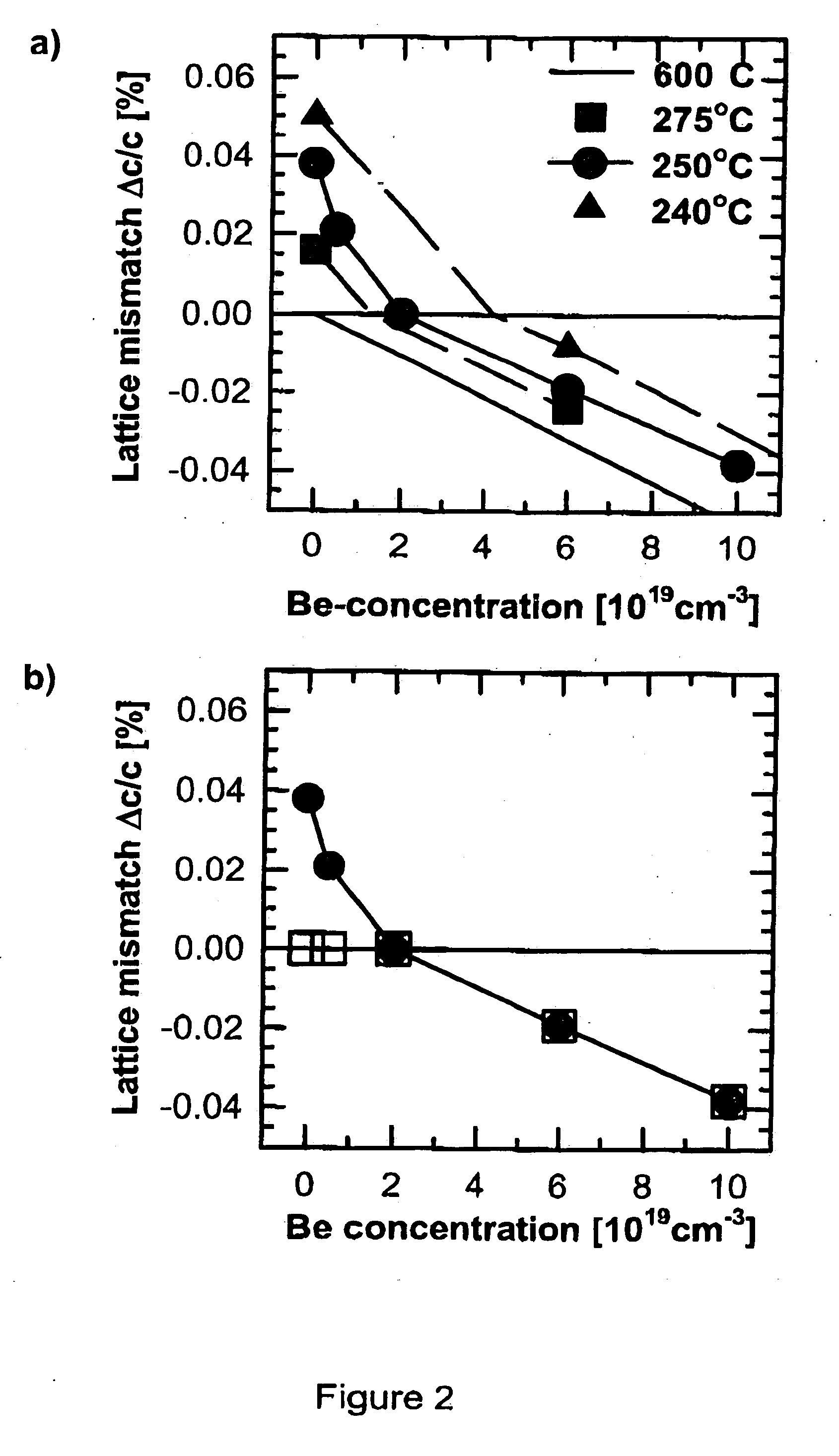

Doping-assisted defect control in compound semiconductors

InactiveUS20050020033A1High resistivityGood reproducibilityPolycrystalline material growthSemiconductor/solid-state device manufacturingTrappingHigh resistivity

The present invention relates to the production of thin film epilayers of III-V and other compounds with acceptor doping wherein the acceptor thermally stabilizes the epilayer, stabilize the naturally incorporated native defect population and therewith maintain the epilayer's beneficial properties upon annealing among other advantageous effects. In particular, balanced doping in which the acceptor concentration is similar to (but does not exceed) the antisite defects in the as-grown material is shown to be particularly advantageous in providing thermal stability, high resistivity and ultrashort trapping times. In particular, MBE growth of LT-GaAs epilayers with balanced Be doping is described in detail. The growth conditions greatly enhance the materials reproducibility (that is, the yield in processed devices). Such growth techniques can be transferred to other III-V materials if the growth conditions are accurately reproduced. Materials produced herein also demonstrate advantages in reproducibility, reliability and radiation hardening.

Owner:RGT UNIV OF CALIFORNIA +1

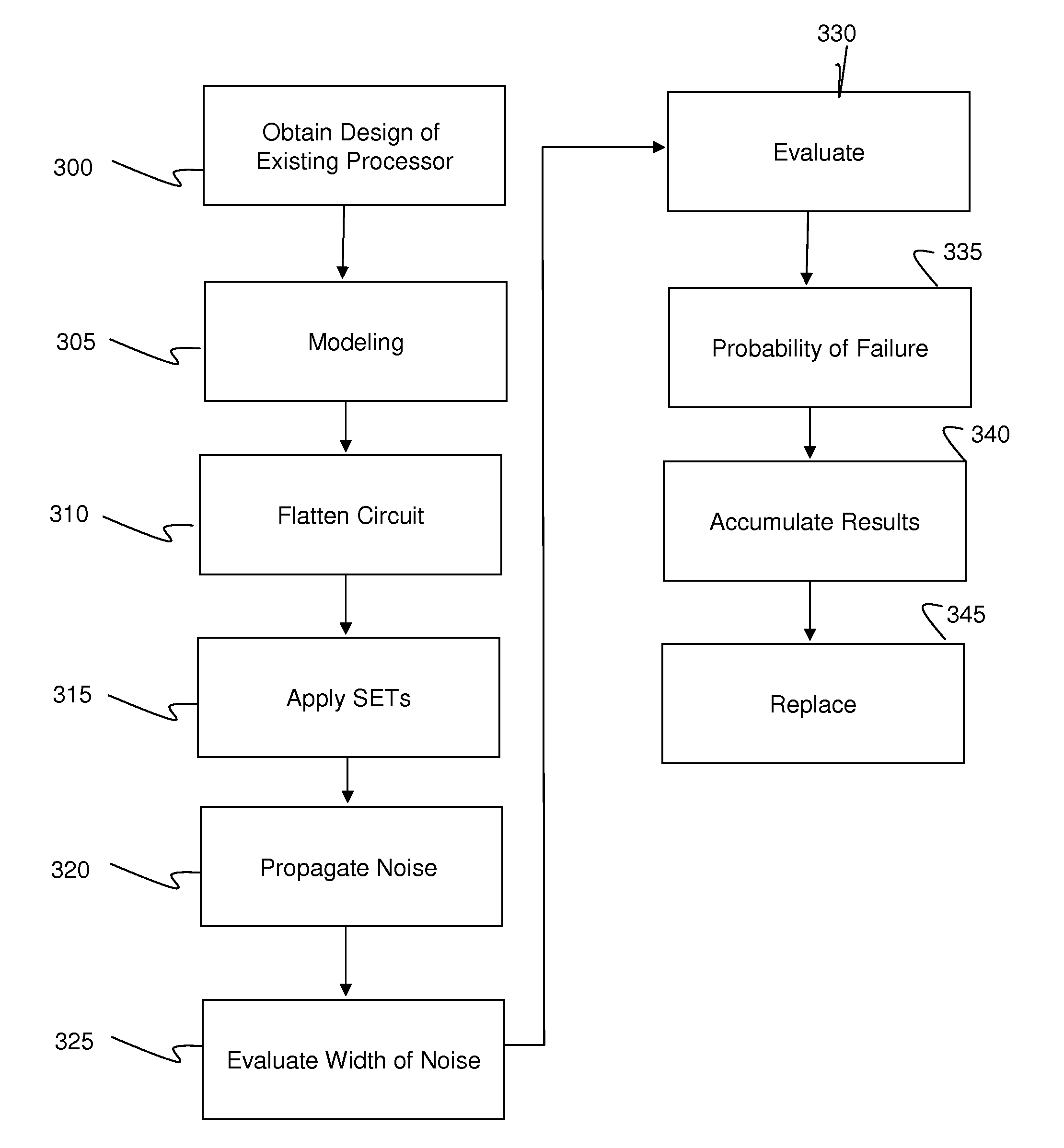

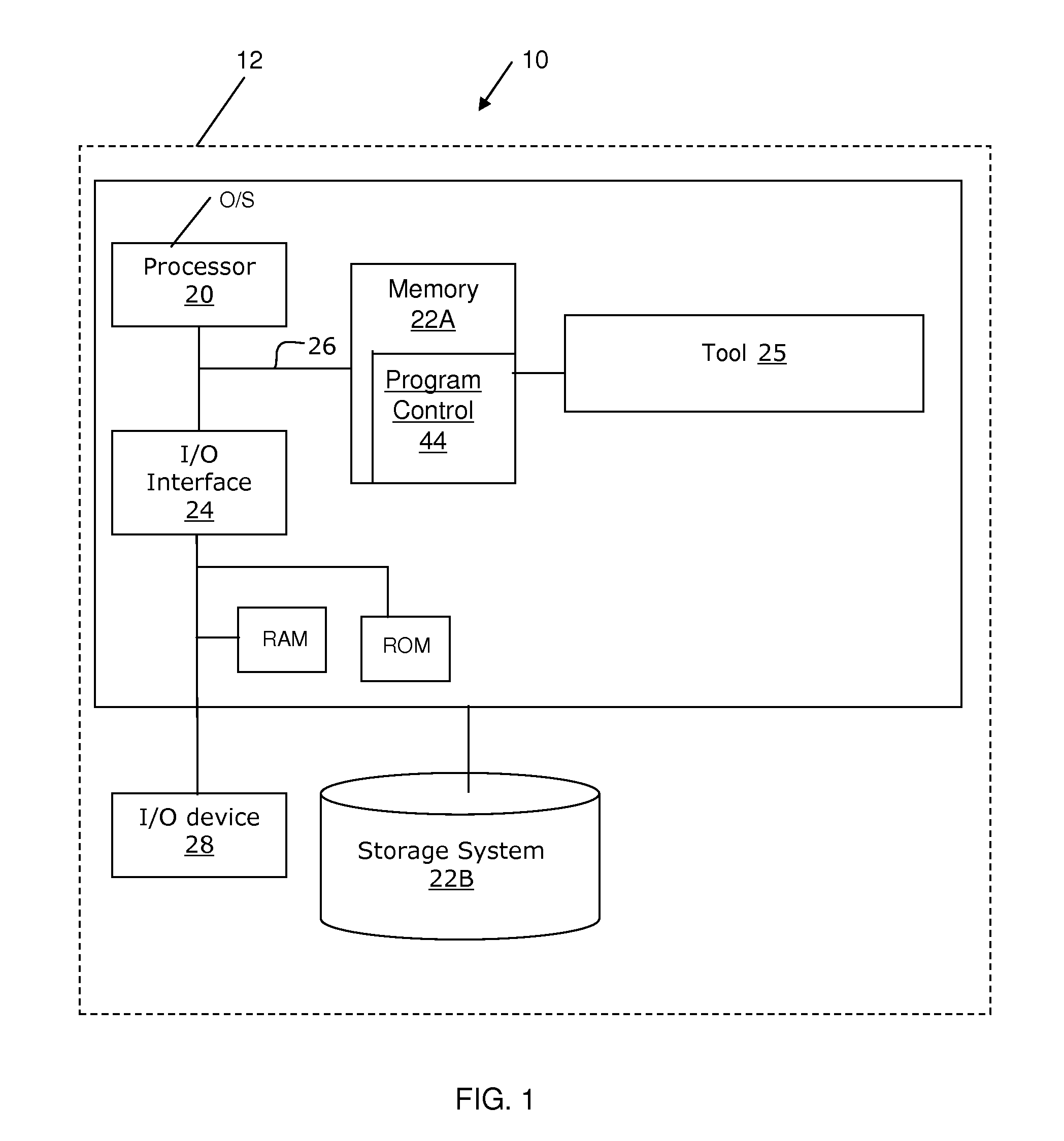

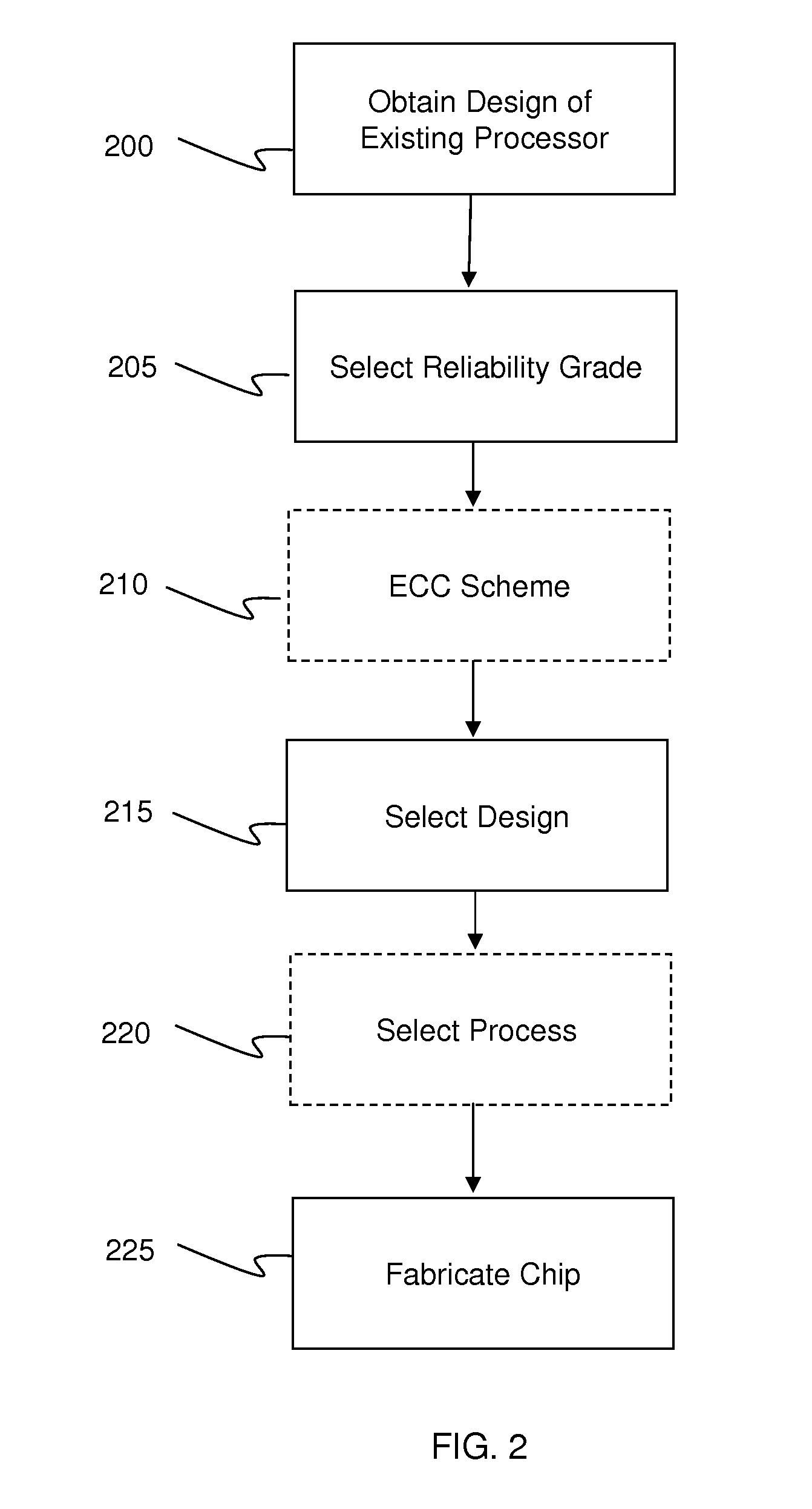

Method for conversion of commercial microprocessor to radiation-hardened processor and resulting processor

A method is provided to convert commercial microprocessors to radiation-hardened processors and, more particularly, a method is provided to modify a commercial microprocessor for radiation hardened applications with minimal changes to the technology, design, device, and process base so as to facilitate a rapid transition for such radiation hardened applications. The method is implemented in a computing infrastructure and includes evaluating a probability that one or more components of an existing commercial design will be affected by a single event upset (SEU). The method further includes replacing the one or more components with a component immune to the SEU to create a final device.

Owner:GLOBALFOUNDRIES INC

Radiation hardening of logic circuitry using a cross enabled, interlocked logic system and method

A system and method for hardening a logic circuit against radiation-event effects is provided. The system may include a logic circuit, first and second feed-forward devices, and first and second feedback devices. The logic circuit may be operable to output independently-obtained first and second redundant signals responsive to a desired input signal. Each of the first and second feed-forward devices may receive both of the first and second redundant signals. When the first and second redundant signals are in expected states, then the first and second feed-forward devices may responsively provide respective first and second feed-forward signals. Each of the first and second feedback devices may receive both of the first and second feed-forward signals. When the first and second feed-forward signals are in expected states, then the first and second feedback devices responsively feed respective first and second feedback signals back to the respective first and second redundant signals.

Owner:HONEYWELL INT INC

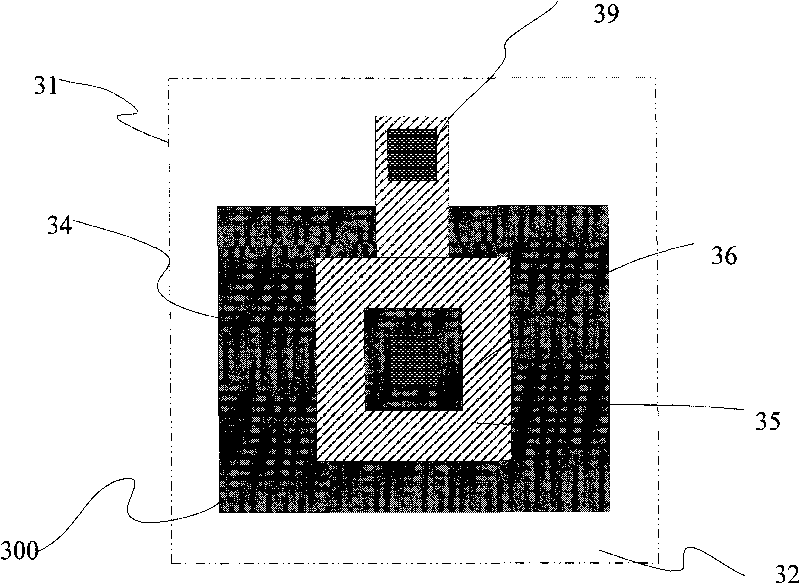

Total dose radiation hardening I-shaped gate layout structure

The invention relates to a total dose radiation hardening I-shaped gate layout structure, which comprises an active region, a field oxidation region outside the active region, and an I-shaped gate overlapped with the active region. The part on the active region, which is not overlapped with the I-shaped gate, is divided into a rectangle source region and a rectangle drain region. The total dose radiation hardening I-shaped gate layout structure arranges a gate oxidation layer below the I-shaped gate layer of the whole region where the I-shaped gate and the active region are overlapped, not only comprises an a region between the source region and the drain region, but also comprises b regions on the upper and lower parts of the source region and the drain region. The formation of the b regions pushes off the distances among the source region, the drain region and the field oxidation region, thus, the total dose radiation hardening I-shaped gate layout structure avoids a field region, cuts off the accesses between an edge radiation parasitic channel of the field oxidation region and the source region and the drain region, better solves the parasitic leakage problem caused by the ionizing radiation total-dose effect, improves the ionizing radiation resistance of the circuit, reduces the chip layout area, and can be applied into the large scale integrated circuit system.

Owner:BEIJING MXTRONICS CORP +1

Novel ceramic heat insulating coat and preparation process thereof

ActiveCN103158306ABlock free energyProtect independenceSynthetic resin layered productsReflecting/signal paintsMetallic materialsCeramic

The invention provides a novel ceramic heat insulating coat and a preparation process of the novel ceramic heat insulating coat. The coat comprises a three-layer structure, including a hollow ceramic micro-bead matrix heat insulating layer, a metal material coating film layer and a seal undercoat layer from outside to inside, wherein hollow ceramic micro-beads are arranged in the hollow ceramic micro-bead matrix heat insulating layer, and the interiors of the hollow ceramic micro-beads are vacuum. The coat and the preparation process disclosed by the invention has the advantages that the production process is simple, the use is economic and reasonable, the construction is convenient, the capacities of reflective heat insulation and radiation hardening can be realized, energy can be obviously saved, the development prospect is considerable.

Owner:HANGZHOU WILLIAM INVESTMENT MANAGEMENT

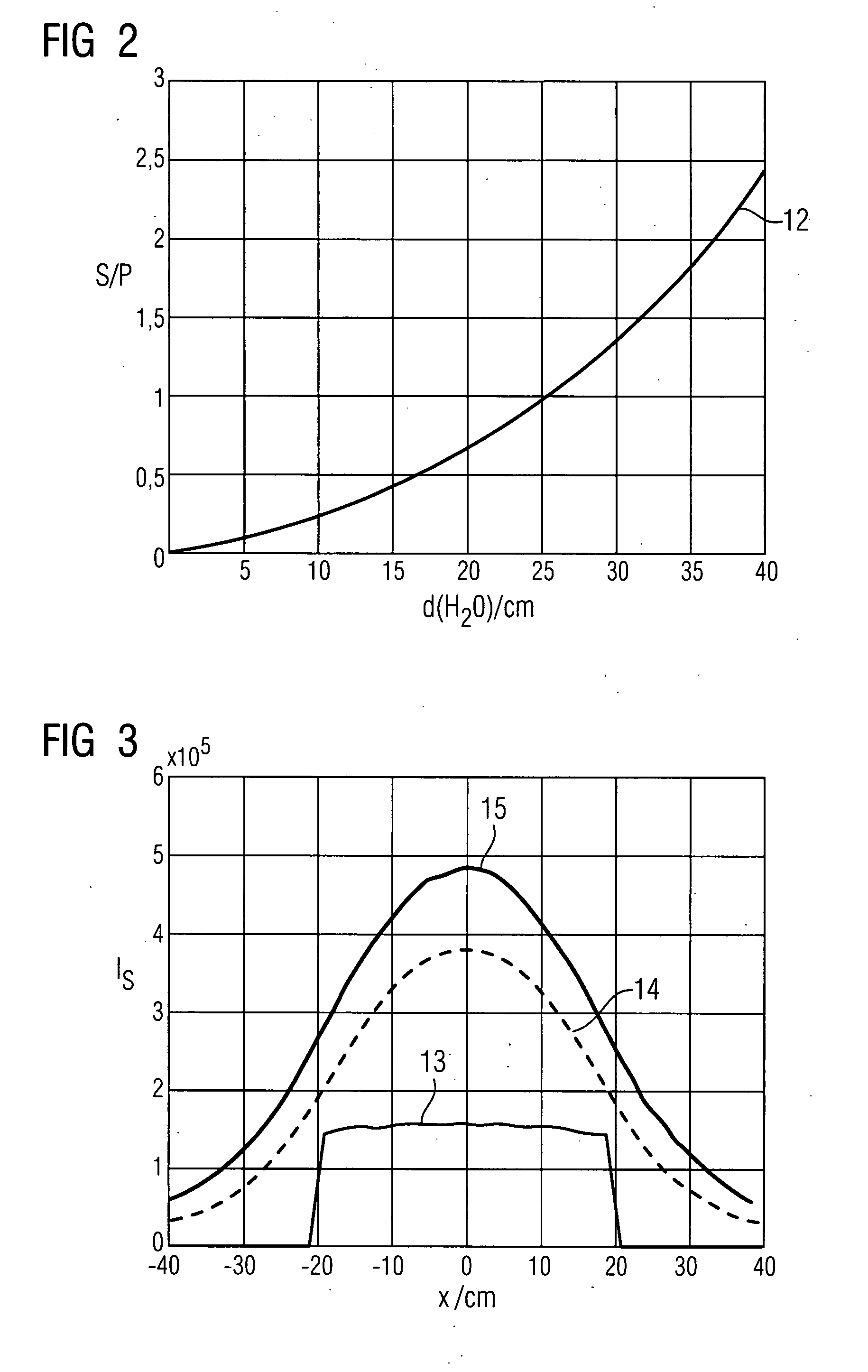

Method for combined bone hardening and scattered radiation correction in X-ray computed tomography

InactiveUS20080159469A1Accurate methodGood compensationMaterial analysis using wave/particle radiationRadiation/particle handlingSoft x rayArithmetic logic unit

The invention relates to a method for combined bone hardening and scattered radiation correction in X-ray computed tomography of a heterogeneous object with a CT system comprising an X-ray source moved around an object, a flat detector with a large number of distributed detector elements which detect measuring beams from a focal point of the X-ray tube, and a control and arithmetic-logic unit—by iterative reconstruction and segmented vectorial reprojection calculation, wherein a scattered radiation correction and a radiation hardening correction are carried out in each iteration cycle for at least two different material components of the object being examined. The invention also relates to an X-ray CT system for carrying out this method.

Owner:SIEMENS HEALTHCARE GMBH

Fabrication methods for radiation hardened isolation structures

ActiveUS8252642B2Reduce and eliminate effectLow costSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Semiconductor devices can be fabricated using conventional designs and process but including specialized structures to reduce or eliminate detrimental effects caused by various forms of radiation. Such semiconductor devices can include one or more parasitic isolation devices and / or buried layer structures disclosed in the present application. The introduction of design and / or process steps to accommodate these novel structures is compatible with conventional CMOS fabrication processes, and can therefore be accomplished at relatively low cost and with relative simplicity.

Owner:SILICON SPACE TECH

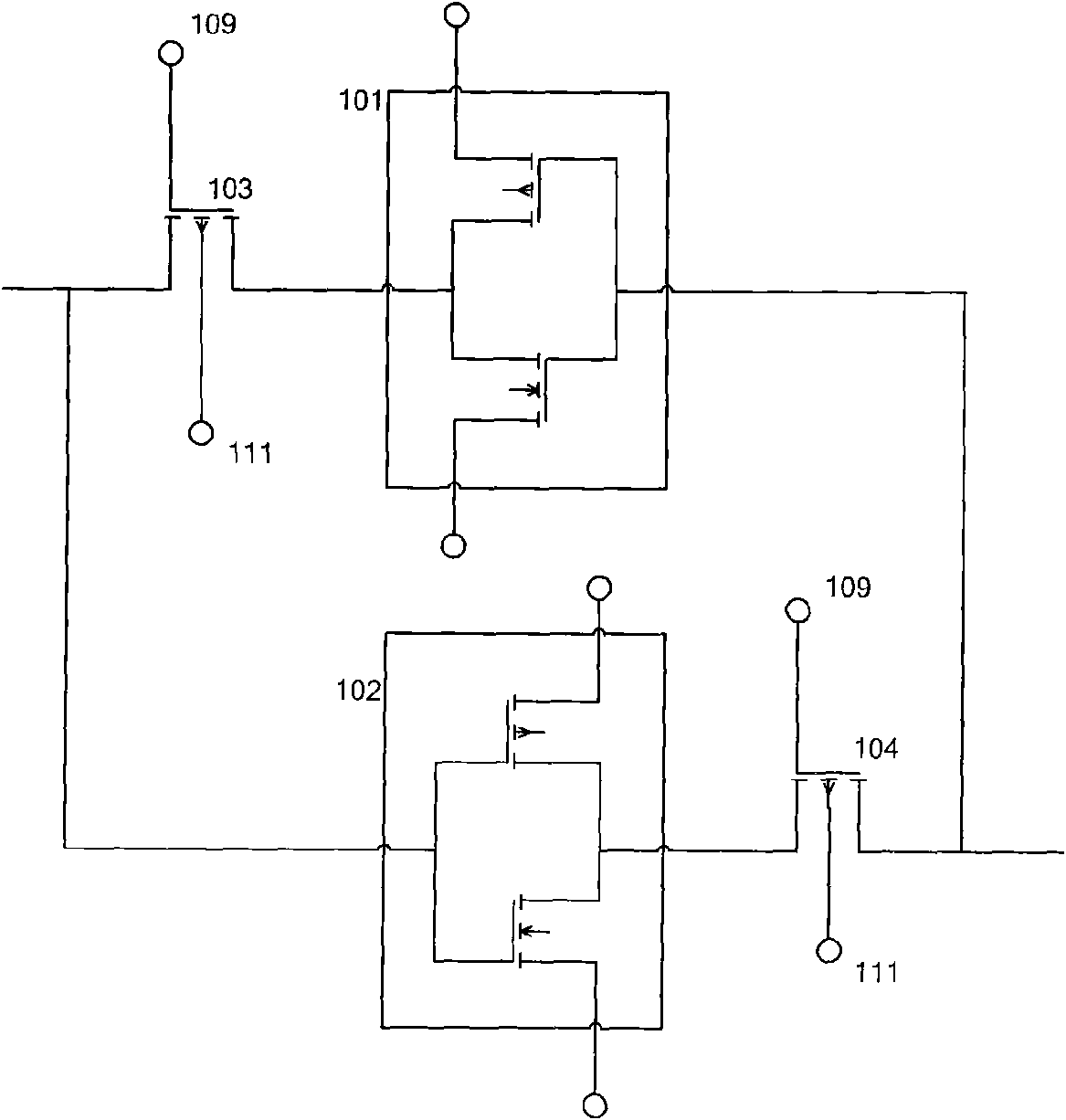

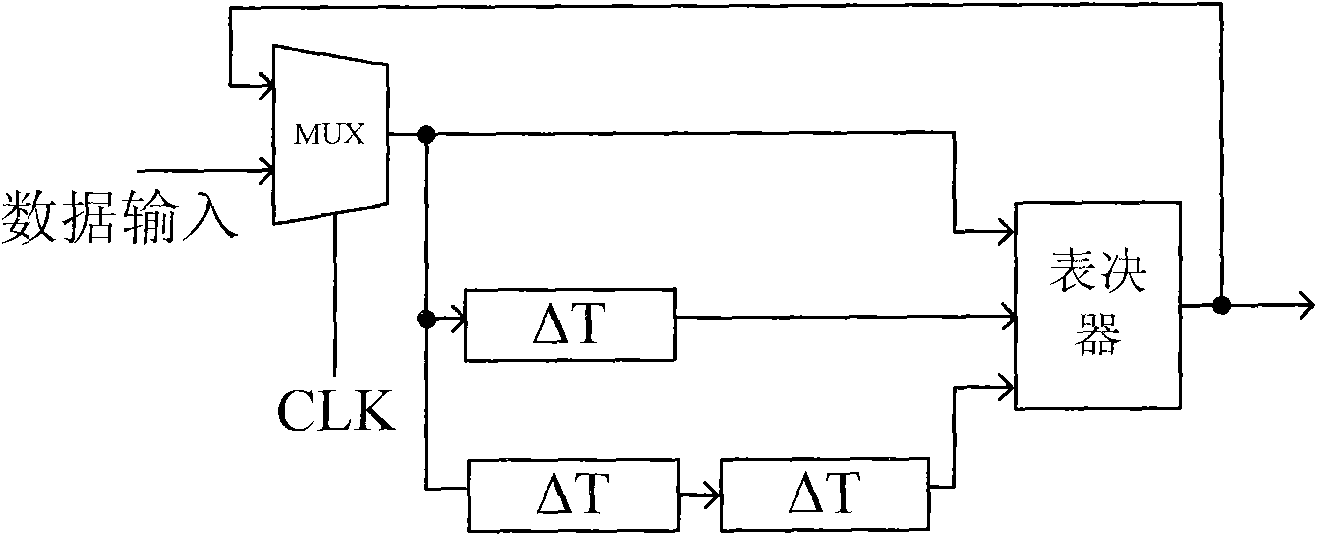

Anti-radiation hardening latch based on TMR and DICE

The invention relates to the field of anti-radiation integrated circuit design in microelectronics, and provides an anti-radiation hardening latch based on TMR and a DICE. In order to achieve protection of SEU of internal data, according to the technical scheme, the anti-radiation hardening latch based on the TMR and the DICE is characterized in that an input satge is composed of four voting modules 1, 2, 3 and 4, the voting module 1 and the voting module 3 receive in-phase input signals, the voting module 2 and the voting module 4 receive anti-phase input signals, N-type transistors M1, M2, M3 and M4 are controlled by a clock signal CK, the voting modules 1, 2, 3 and 4 achieve voting on selecting one from the front-stage input signals A, B and C and the anti-phase signals of the front-stage input signals A, B and C, the communication condition of the voting module 1 is the same as that of the voting module 3, the communication condition of the voting module 2 is the same as that of the voting module 4, and the communication condition of the voting module 1 is opposite to that of the voting module 2. The anti-radiation hardening latch based on the TMR and the DICE is mainly applied to the anti-radiation integrated circuit design.

Owner:TIANJIN UNIV

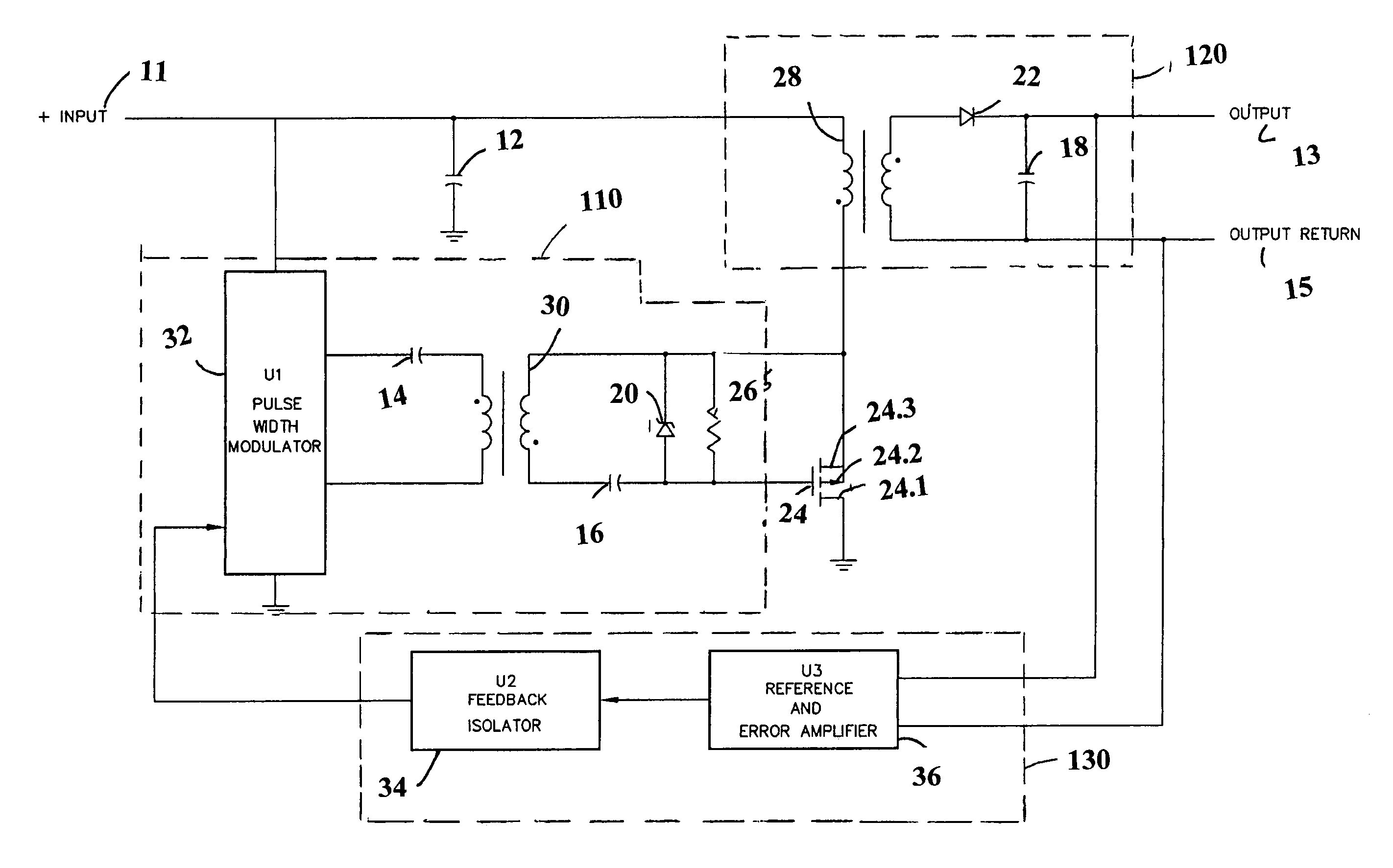

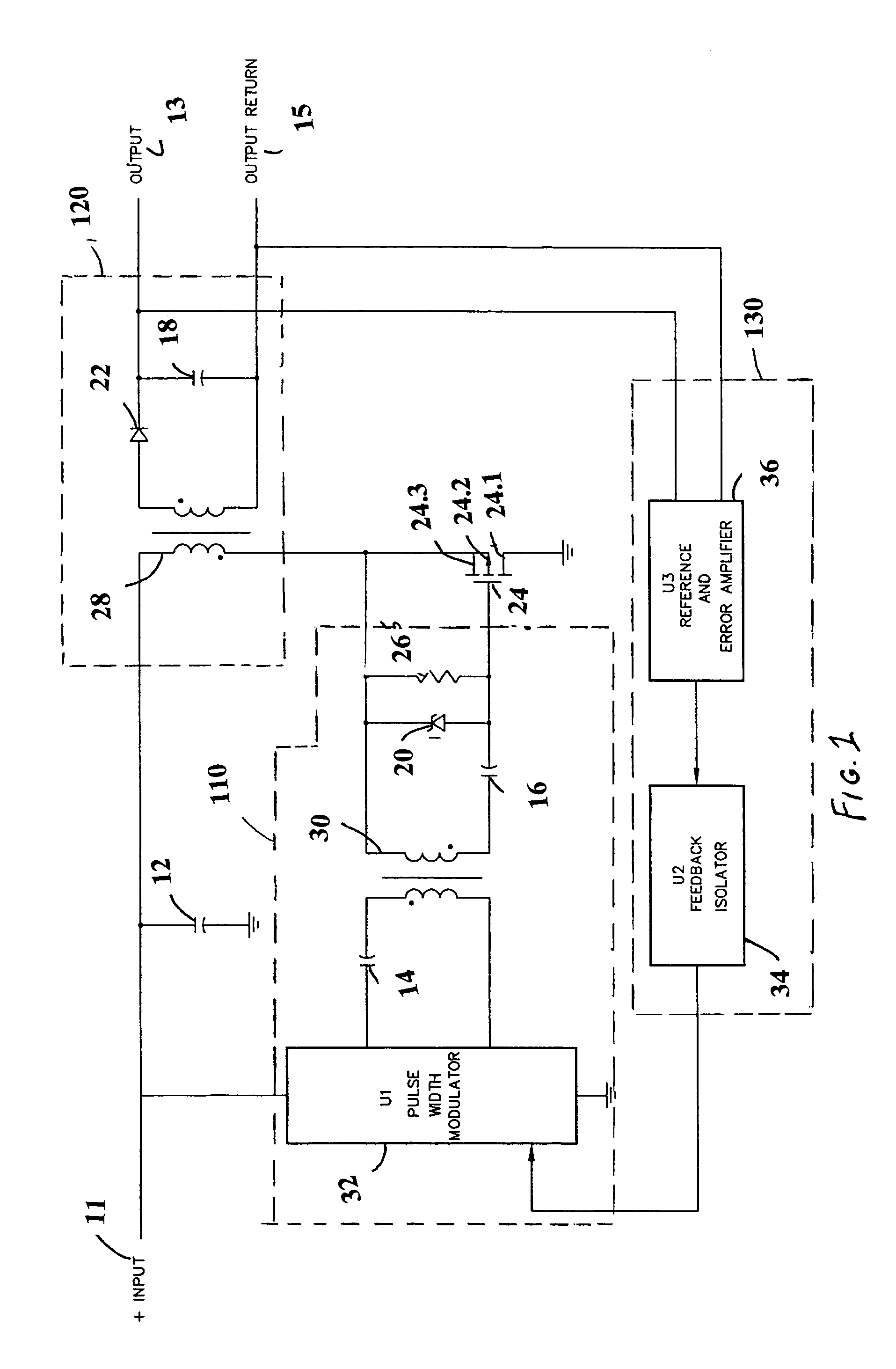

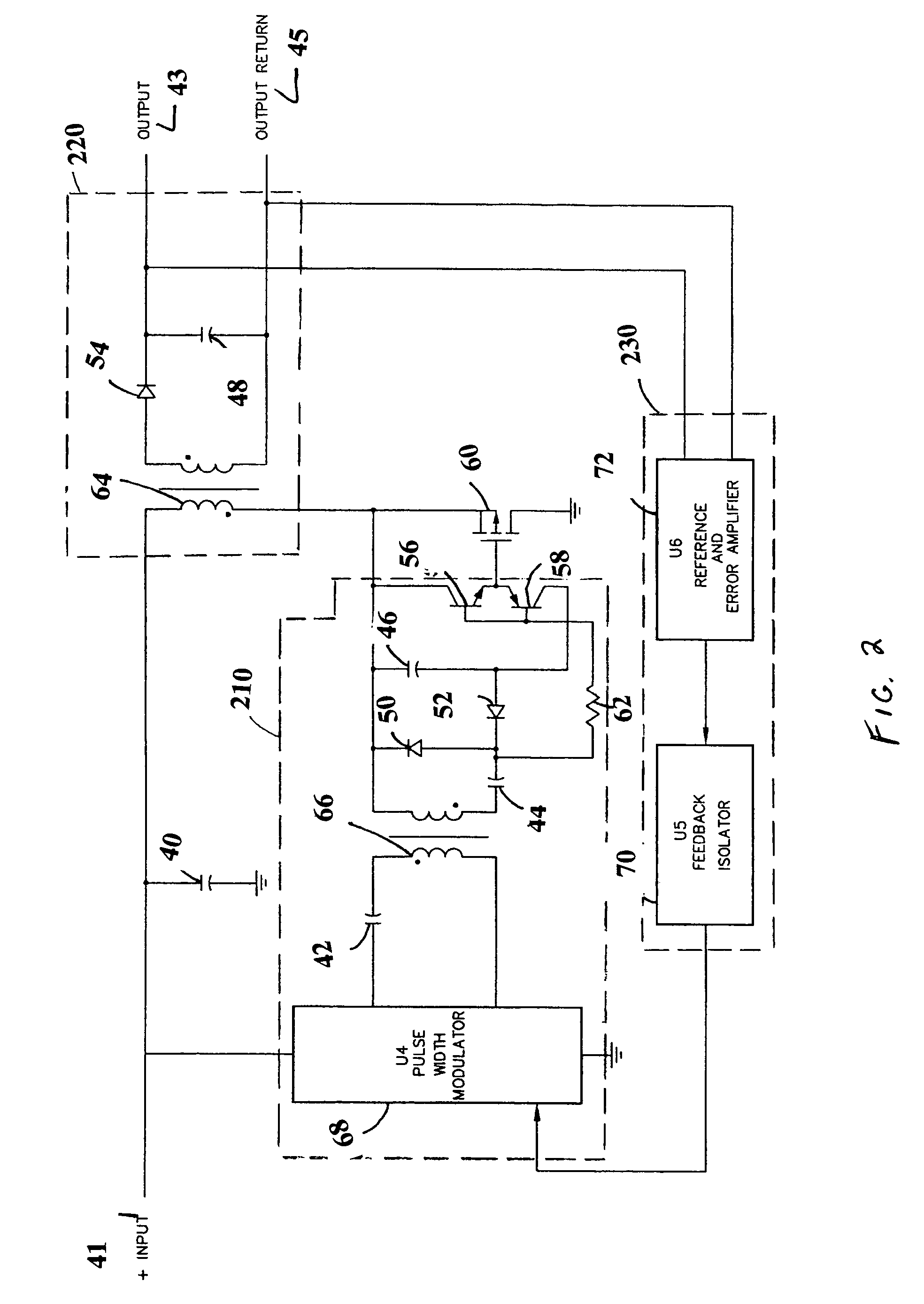

Radiation tolerant electrical component with non-radiation hardened FET

ActiveUS6982883B2Dc-dc conversionEmergency protective arrangements for automatic disconnectionMOSFETGate voltage

A radiation tolerant electrical component is provided without a radiation hardened material FET. A p-channel MOSFET provides switching capabilities in radiated environments because its gate voltage starts at a negative value and becomes more negative with exposure to radiation. Therefore, the gate is still controllable when exposed to radiation.

Owner:SUMMER STEVEN E

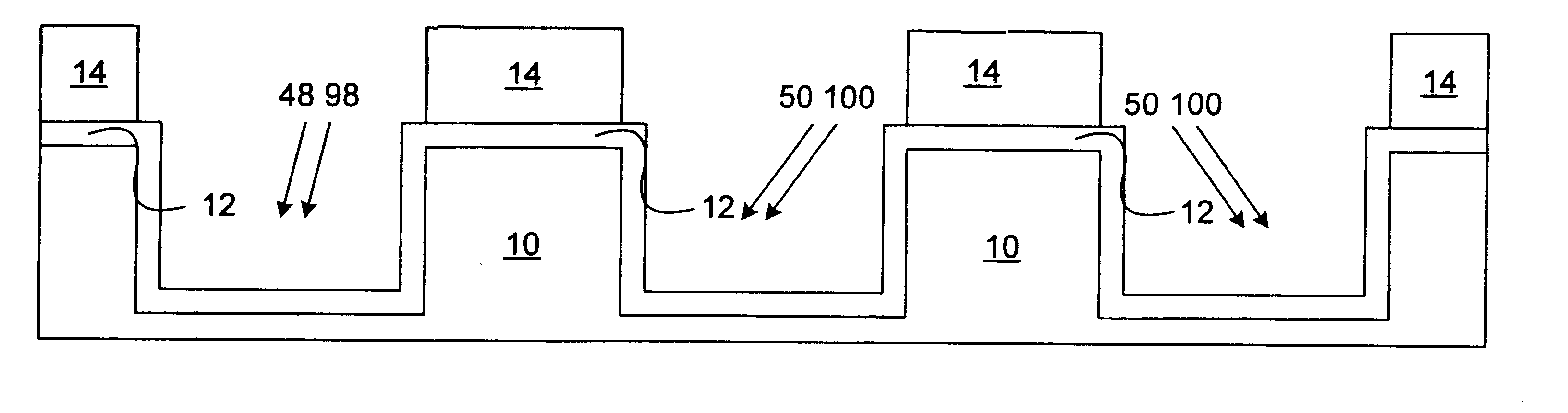

Method for rapid prototyping by using linear light as sources

InactiveUS20060100734A1Additive manufacturing apparatus3D object support structuresLiquid-crystal displayEngineering

A method for rapid prototyping by using linear light as sources employs DLP (Radiation Hardening Formation) or LCD, together with the portable devices and linear light source to treat the raw material in two stages. The first stage is to spread the raw material to a selected zone by nozzles or rollers and illuminating the material to let the material being processed and have physical o mechanical changes. The second stage is to use more powerful linear light source with the cooperation of the portable DMD (Digital Micromirror Device) or LCD (Liquid Crystal Display) to illuminate the material to make it have a second times of physical o mechanical changes. By the piling up the layers of the material, a complete 3-D work piece is obtained.

Owner:NAT CHENG KUNG UNIV

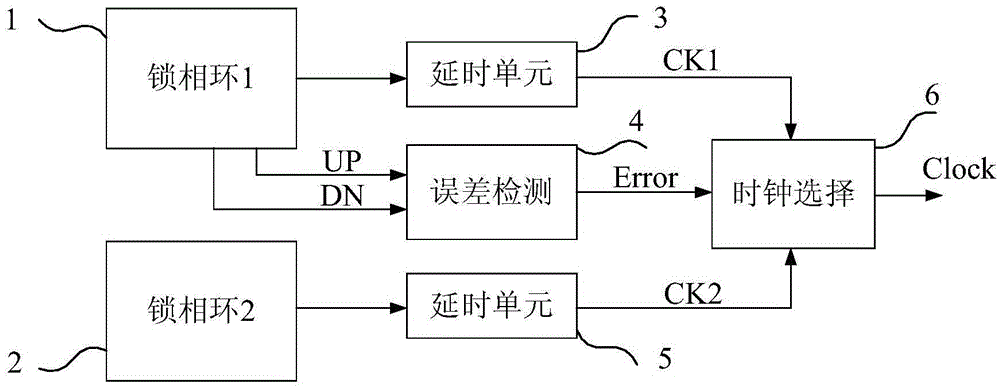

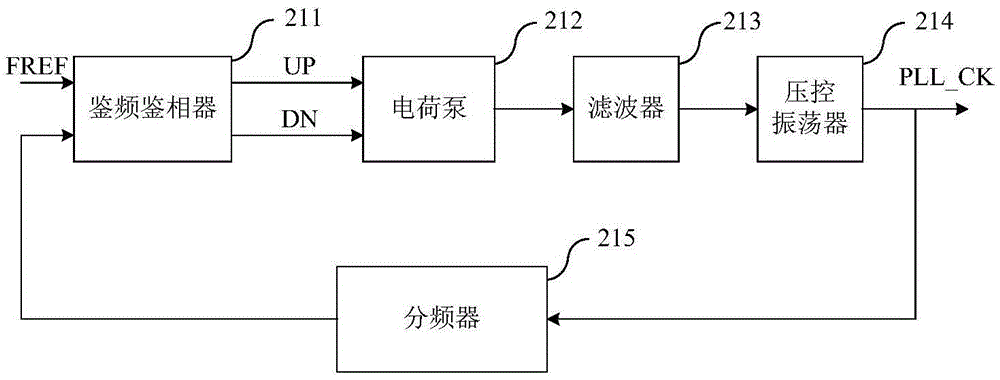

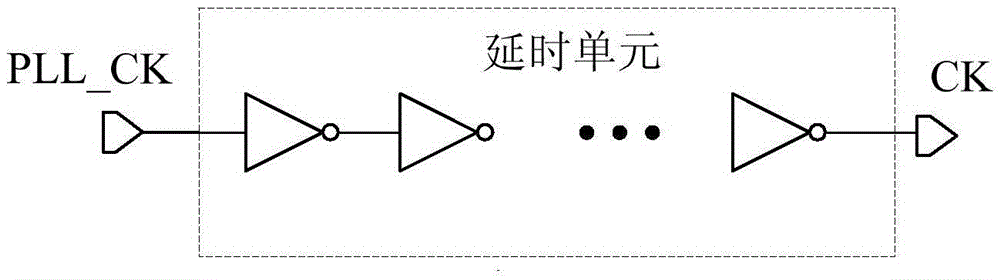

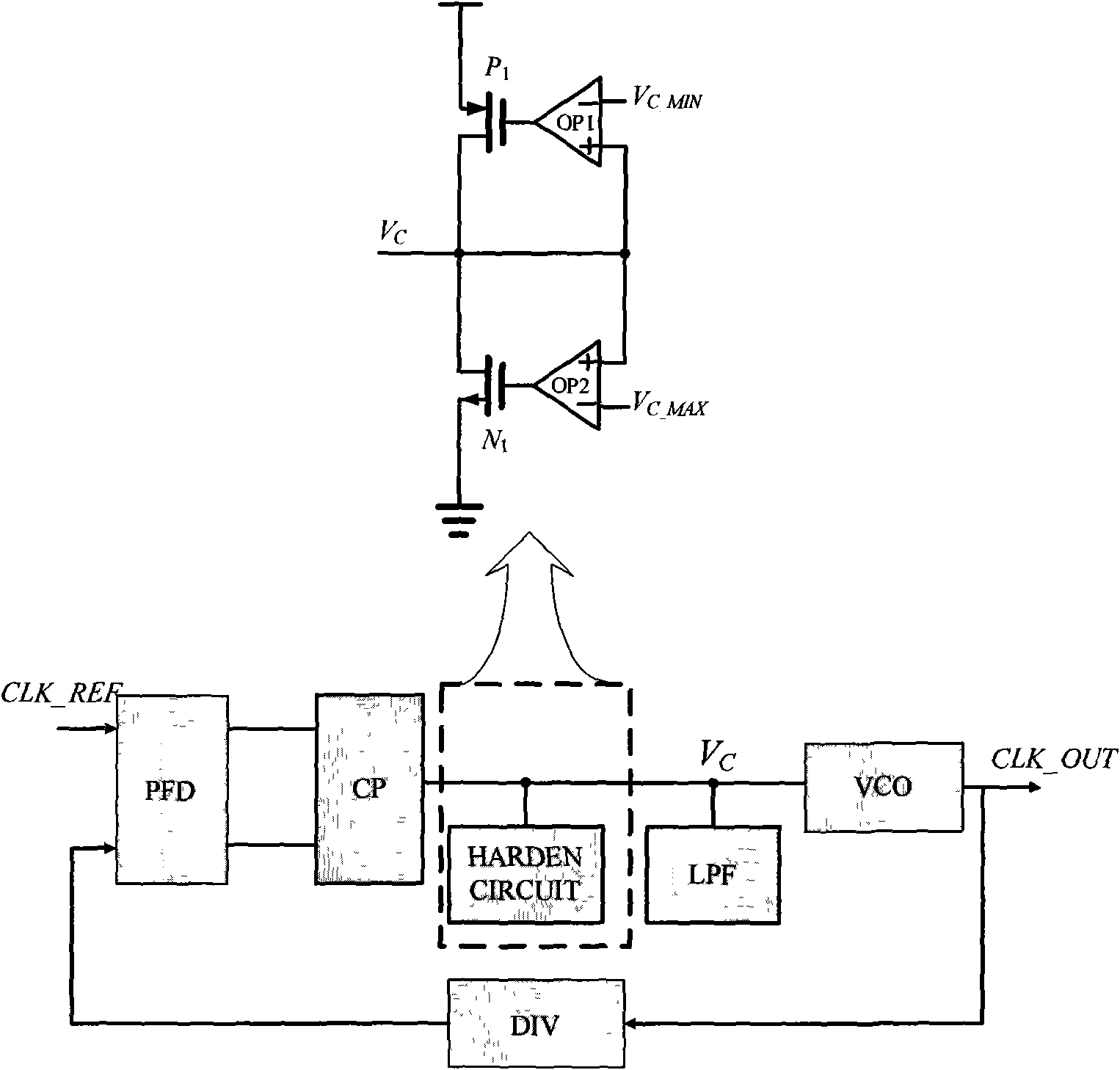

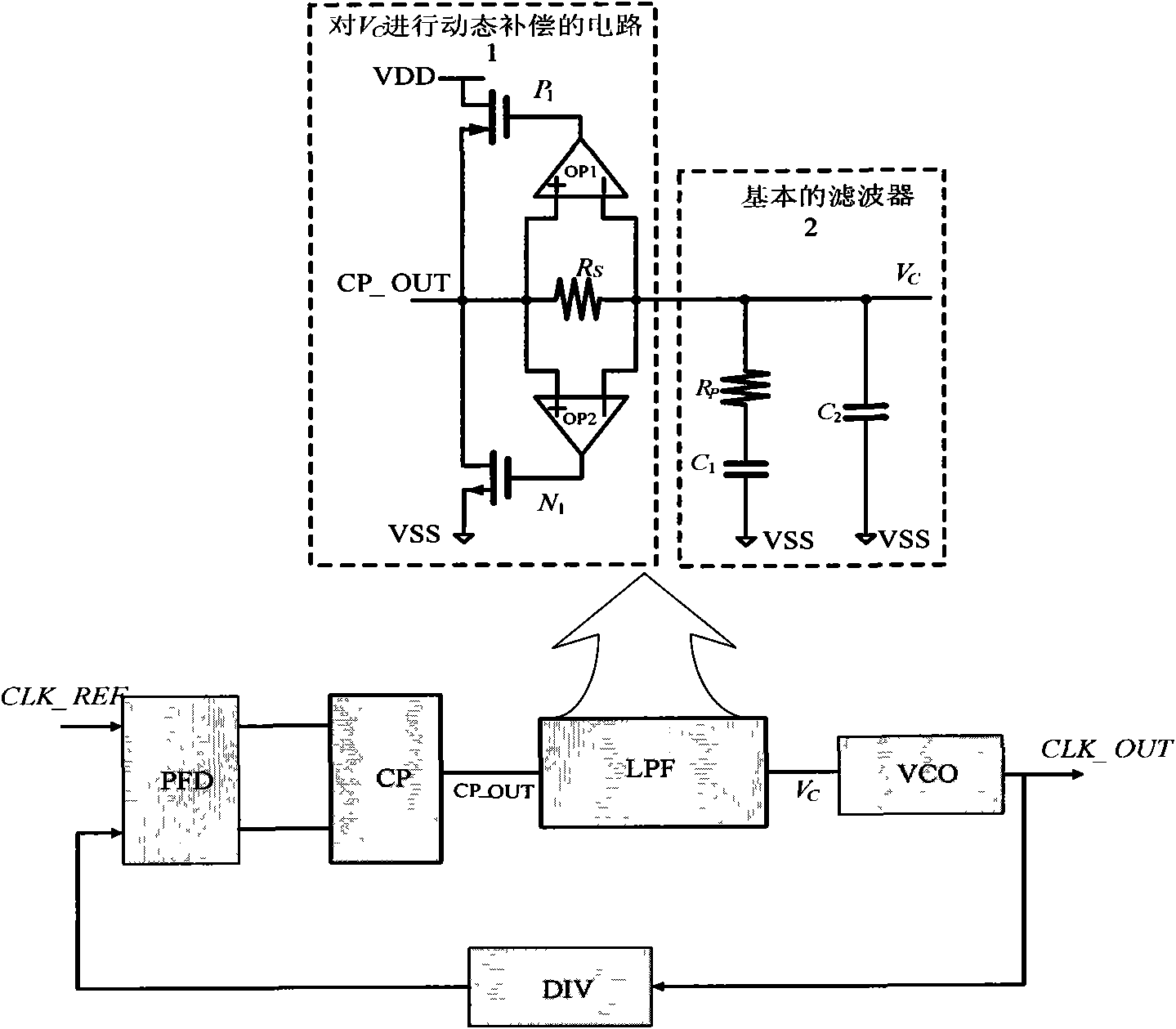

Dual-mode self switching radiation hardening clock generation circuit based on phase-locked loops

ActiveCN105610430AHigh immunity to single event transientsImprove immunityPulse automatic controlDual modePhase frequency detector

The invention provides a dual-mode self switching radiation hardening clock generation circuit based on phase-locked loops, which is mainly composed of two independent phase-locked loops, a delay unit, an error detection unit and a clock selection unit. The two independent phase-locked loops are charge pump phase-locked loops not subjected to radiation hardening, and used for providing corresponding clock output; the delay unit realizes the delay of output signals of the phase-locked loops; the error detection unit is used for detecting whether two output signals of a phase frequency detector in a main phase-locked loop are right and outputting corresponding indication signals; and the clock selection unit performs selective output on the delayed output of the two phase-locked loops as the final output. The dual-mode self switching radiation hardening clock generation circuit based on the phase-locked loops provided by the invention can eliminate interference of a single event effect in a radiation environment on a circuit working state to a great extent, ensure the stability of the phase-locked loops as clock signals, improve the reliability of the system, and has the advantages of being easy in implementation, small in area, low in power consumption and so on.

Owner:BEIJING MXTRONICS CORP +1

Epoxy cast technology for high tension coil of electron accelerator

The invention relates to a coil epoxy pouring technique. Its feature is that the technique includes the processes like deifilling, putting into vacuum dry room, preheating, vacuumizing, distributing epoxy, mixing glue, irrigating, topping up, solidifying, forming stripping, coil post treatment, etc. And taking the method in the state of definite vacuum extent pours the liquid oxygen in to the mould to a certain temperature and a certain speed to ensure according the technique that the epoxy far away from the casting head freezes first, then freezes towards to the casting head progressively and the freezing of the casting head itself is the last. The feature of the system needed in the technique is that it is made up of coil epoxy pouring mould, vacuum drying room, heater, stirring-bowl, mechanical pump of the stirring-bowl, thermometer, bogie, crane. The advantage of the invention is simple structure, convenience moulding, high insulating strength of the coil, radiation hardening, waterproof, moisture proof, reliable performance, low cost and can adapt for manufacturing.

Owner:上海克林技术开发有限公司

Radiation hardening method for shallow trench isolation in CMOS

InactiveUS6890832B1Reduce the probability of spreadingEliminate leaksSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSSemiconductor

A radiation-hardened STI process includes implanting a partially formed wafer with a fairly large dose (1013 to 1017 ions / cm2) of a large atom group III element, such as B, Al, Ga or In at an energy between about 30 and 500 keV. The implant is followed by an implant of a large group V element, such as P, As, Sb, or Bi using similar doses and energies to the group III element. The group V element compensates the group III element. The combination of the two large atoms decreases the diffusivity of small atoms, such as B, in the implanted areas. Furthermore, the combination of the group III and group V elements in roughly equal proportions creates recombination sites and electron traps in the field oxide, resulting in a radiation hardened semiconductor device.

Owner:CAES COLORADO SPRINGS LLC

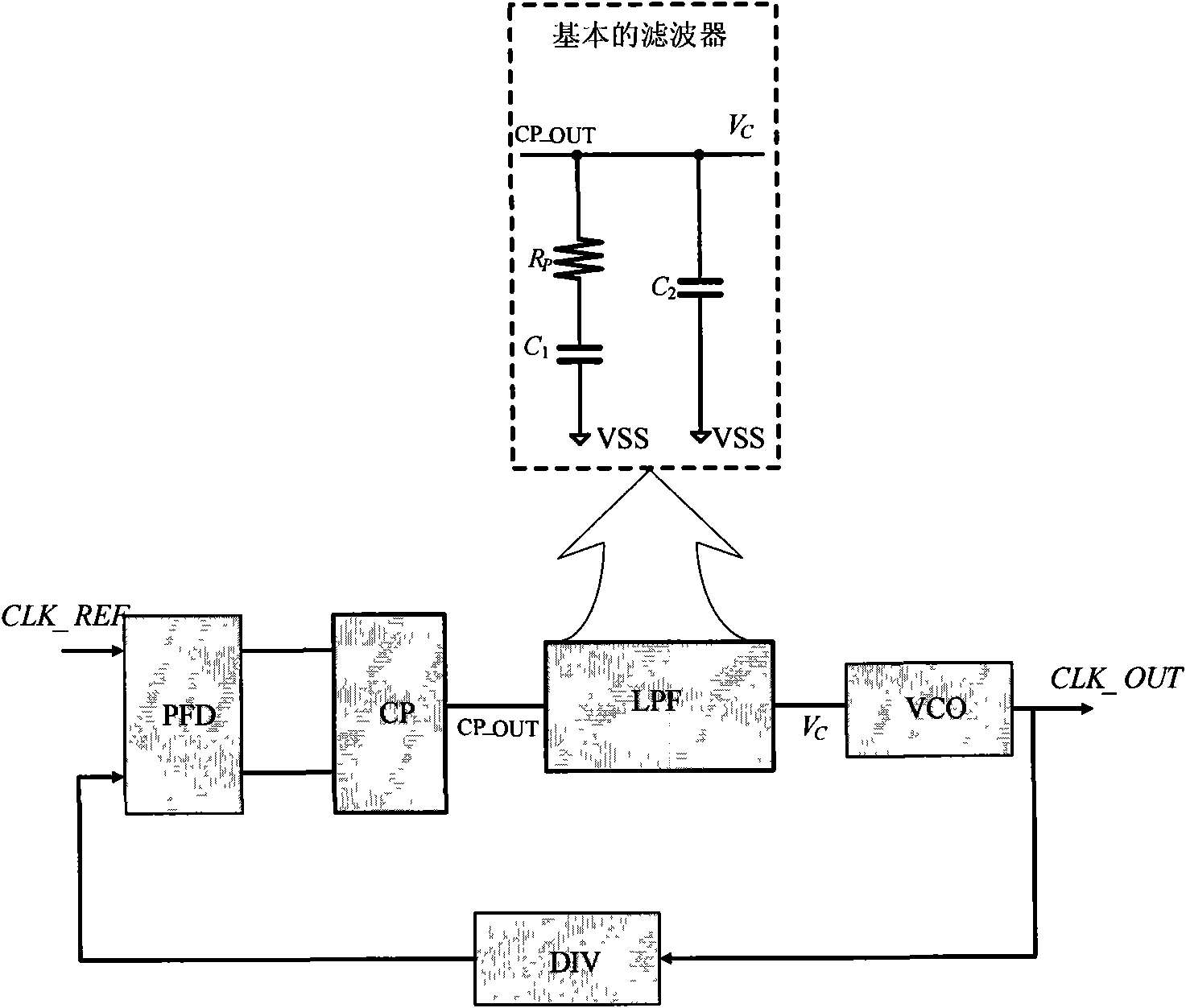

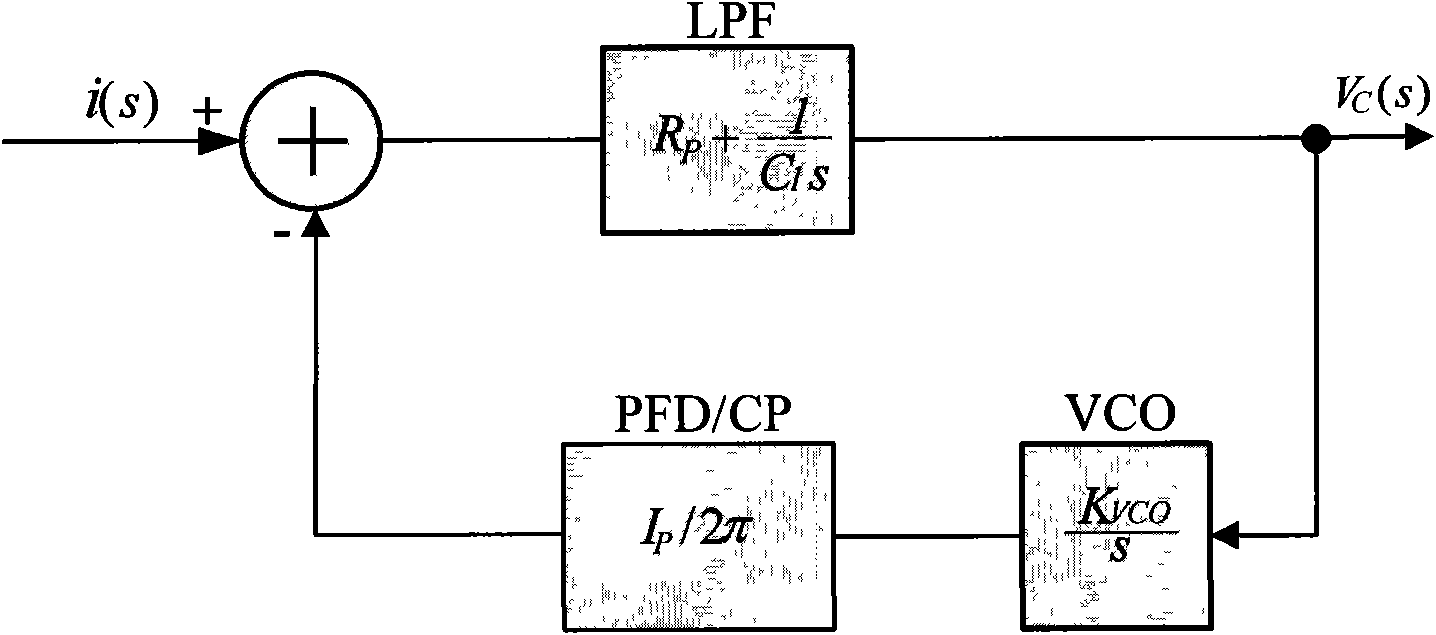

Phase-locked loop for reinforcing single-event transients (SET)

InactiveCN101572547AMitigation of Transient (SET) EffectsReduce the impactPulse automatic controlPhase locked loop circuitEngineering

The invention discloses a phase-locked loop for reinforcing single-event transients (SET), which comprises a basic phase-locked loop circuit and a symmetrical-control voltage-compensation radiation-hardening circuit. The phase-locked loop has no special requirements for the phase-locked loop circuit, and can be any phase-locked loop. The radiation-hardening circuit comprises an operational amplifier OP1, a pull-up PMOS pipe P1, an operational amplifier OP2 and a pull-down NMOS pipe N1, wherein the OP1 detects a minimum value of control voltage VC of a voltage-controlled oscillator (VCO), and controls the pull-up PMOS pipe P1 to be opened and closed so as to compensate the VC forward; and the OP2 detects a maximum value of the control voltage VC of the VCO, and controls the pull-down NMOS pipe N1 to be opened and closed so as to compensate the VC reversely. The phase-locked loop has the advantages of easing the radiation influence on each sensitive node in the phase-locked loop and speeding up locking the loop circuit, along with little cost and wide application range.

Owner:NAT UNIV OF DEFENSE TECH

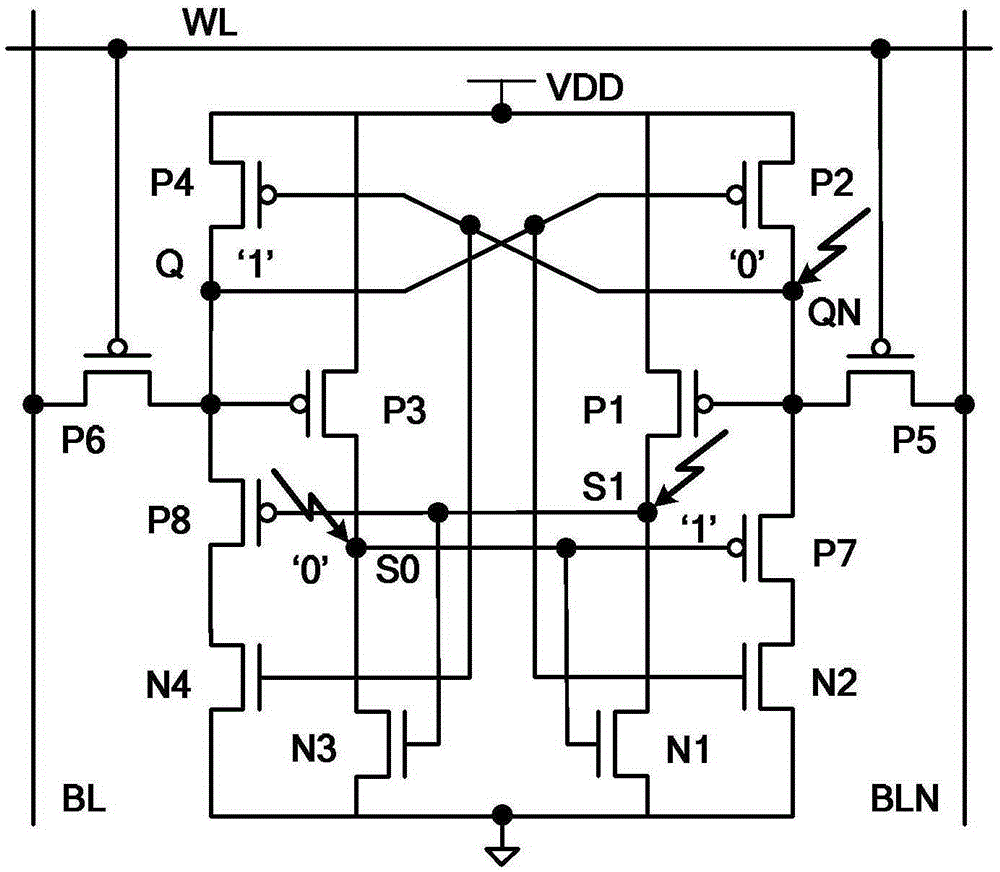

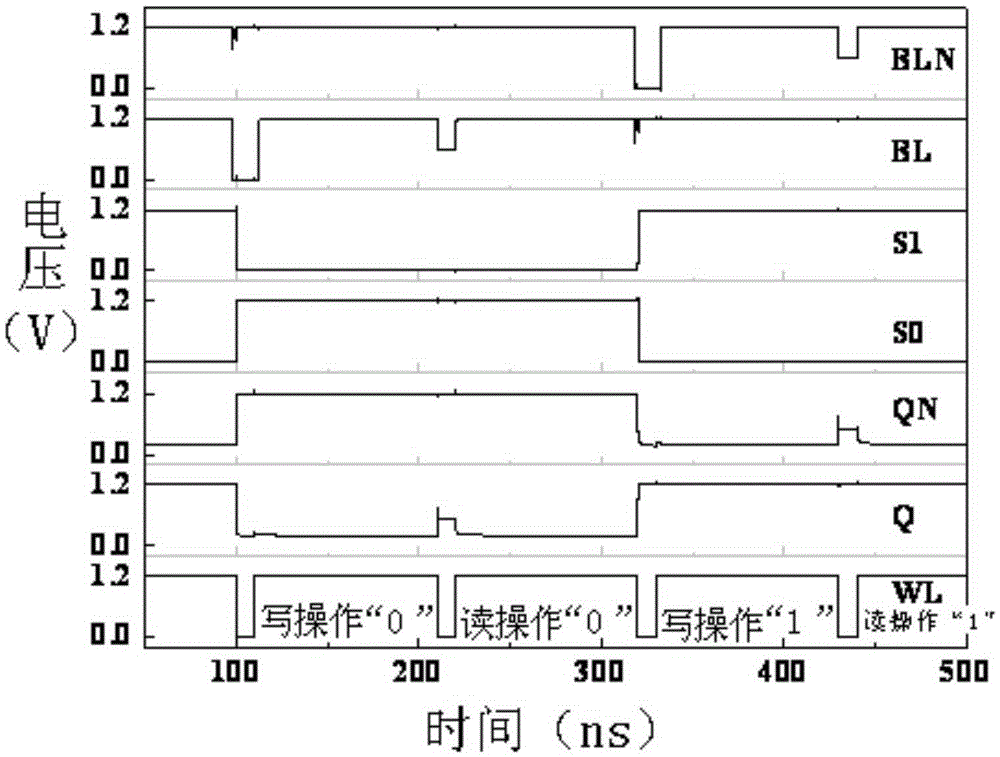

Radiation hardened static random access memory

InactiveCN105336362AReduce the impactReduce or even eliminate the impactDigital storageFault toleranceStatic random-access memory

The invention provides a radiation hardened static random access memory, and relates to the field of radiation hardening circuits. The radiation hardened static random access memory aims at solving the problem that because an existing static random access memory is sensitive to radiation articles in space and natural radiation environments, reliability is poor. The radiation hardened static random access memory is composed of 12 MOS pipes, namely, the PMOS pipe P1, the PMOS pipe P2, the PMOS pipe P3, the PMOS pipe P4, the PMOS pipe P5, the PMOS pipe P6, the PMOS pipe P7, the PMOS pipe P8, the NMOS transistor N1, the NMOS transistor N2, the NMOS transistor N3 and the NMOS transistor N4. By means of the radiation hardened static random access memory, upset of any single node in an SRAM unit can be reinforced and multi-node upset prevention fault tolerance can be conducted on two fixed nodes without depending on stored values. The radiation hardened static random access memory is used in integrated circuit design.

Owner:ZHONGBEI UNIV +1

Near-infrared shielding film

InactiveCN101616800AExcellent near-infrared shieldingExcellent visible light penetrationFilm/foil adhesivesSynthetic resin layered productsInfraredWeather resistance

A near-infrared shielding film composed of a substratum film having, superimposed on its one major surface, a hard coat layer produced from a hard coat layer forming material containing a near-infrared absorbent and an actinic energy radiation hardening compound and having, superimposed on its other major surface, a pressure sensitive adhesive layer, characterized in that the actinic energy radiation hardening compound is composed mainly of an acrylate monomer of penta- or higher functionality. This film has characteristics such that it excels in not only near-infrared shielding performance but also visible ray transmission, having high scratch resistance and weather resistance, and such that in the application to curved glass, the film exhibits reduced curling to thereby facilitate application work, being suitable for application to buildings and automobiles, especially the window glass of automobile.

Owner:LINTEC CORP

Low-pass filter for enhancing radiation resisting capability of charge pump

InactiveCN101674078ASmall structureParameters have little effectPulse automatic controlSingle electronBand-pass filter

The invention discloses a filter aiming at the radiation hardening of a charge pump (CP), which comprises a basic filter and a circuit carrying out dynamic compensation on VC, wherein the basic filtercan be a filter in any charge pump type phase locked loops. The circuit carrying out the dynamic compensation on the VC comprises operation amplifiers OP1 and OP2, compensation pipes P1 and N1 and aninduction resistor RS. The RS is used for converting single electron transition (SET) current into the input voltage of the operation amplifiers, and the operation amplifier OP1 is used for detectingsingle electron transition (SET) in an NMOS pipe and controlling the opening of the compensation pipe P1 to carry out compensation. The operation amplifier OP2 is used for detecting the single electron transition (SET) in a PMOS pipe and controlling the opening of the compensation pipe N1 to carry out compensation. The invention has small expense and wide application range, effectively relieves the radiation influence of the charge pump in the phase locked loop, decreases the required time for recovering the locking of a loop circuit after radiation and has small influence on the parameter and the performance of the loop circuit of the original phase locked loop (PLL).

Owner:NAT UNIV OF DEFENSE TECH