High performance, low power vertical integrated CMOS devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

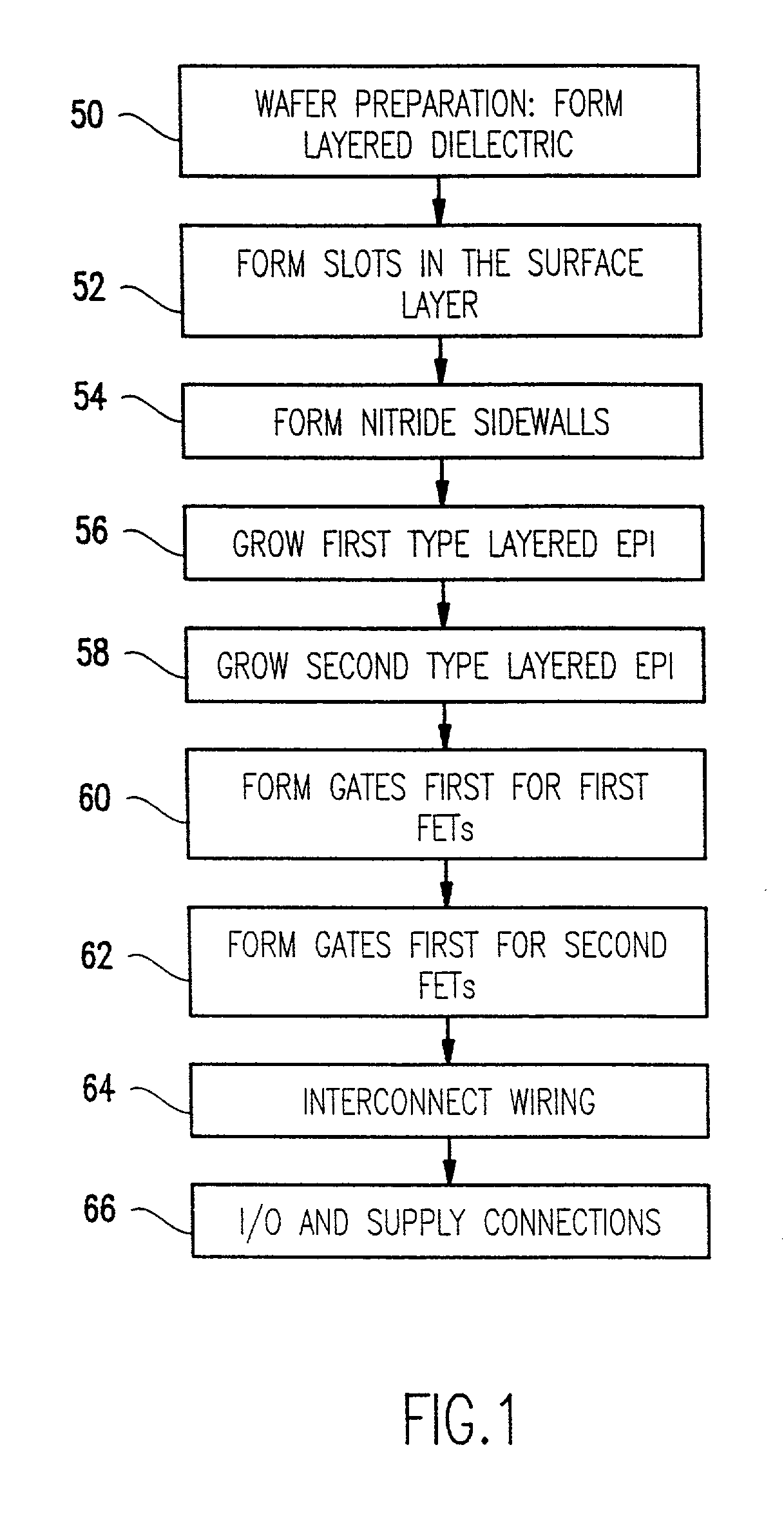

[0036] FIG. 1 is a flow diagram for forming FETs according to a preferred embodiment of the present invention.

[0037] In its simplest form, the preferred embodiment of the present invention is a self-aligned vertical FET having both device characteristics and reduced device parasitic capacitance such as would normally be found in a self-aligned Silicon on Insulator (SOI) device. The preferred embodiment FET may be a short channel (0.1 micrometer (um)) N-type FET (NFET) or P-type FET (PFET). Complementary pairs of preferred self-aligned vertical devices (NFET:PFET) may be combined to provide CMOS equivalent circuits, e.g., a complementary pair of self-aligned preferred vertical devices (an NFET and a PFET) may be used as an invertor. Typical V.sub.h for a preferred embodiment circuit of preferred embodiment devices is <1.5V.

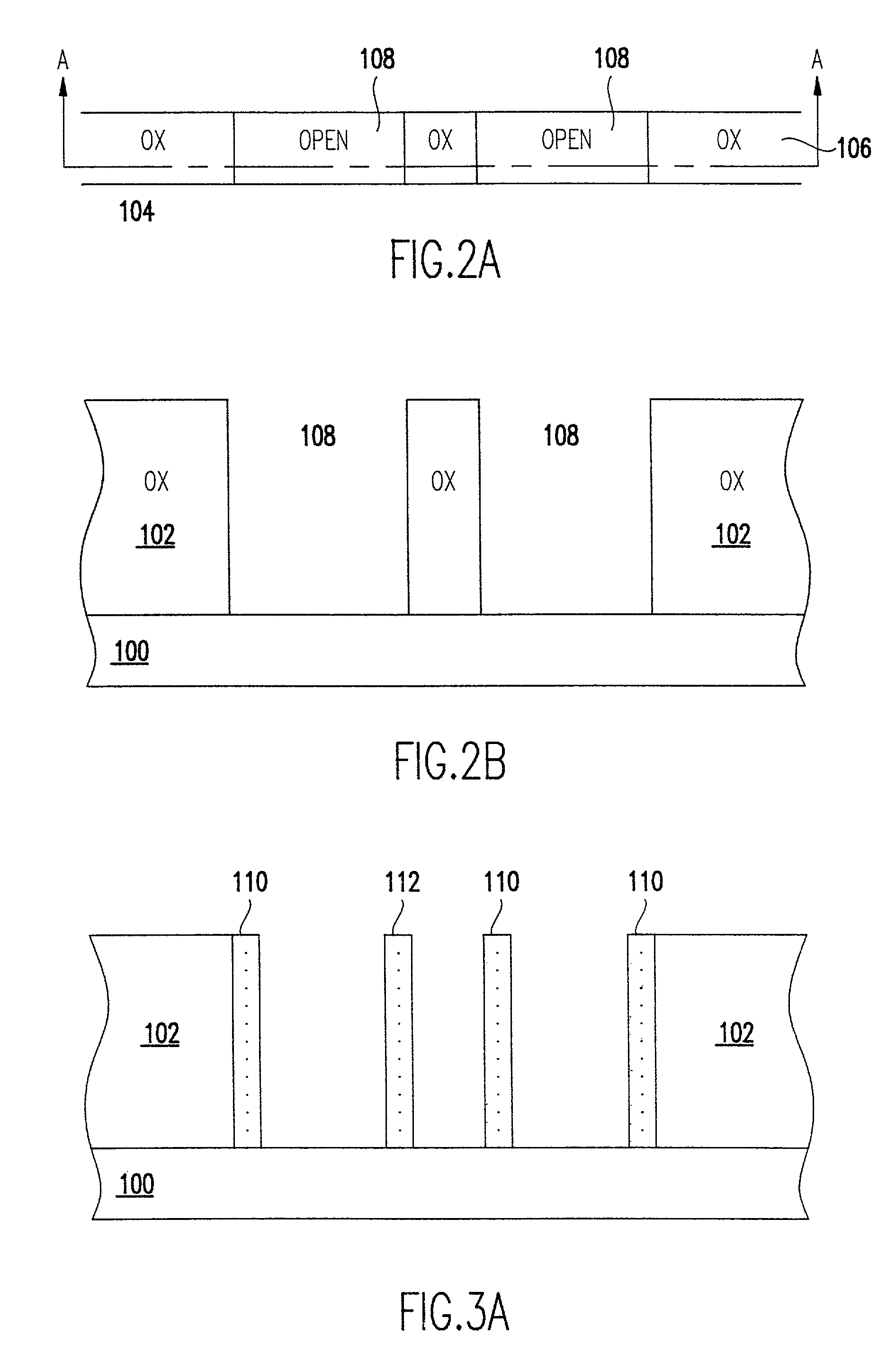

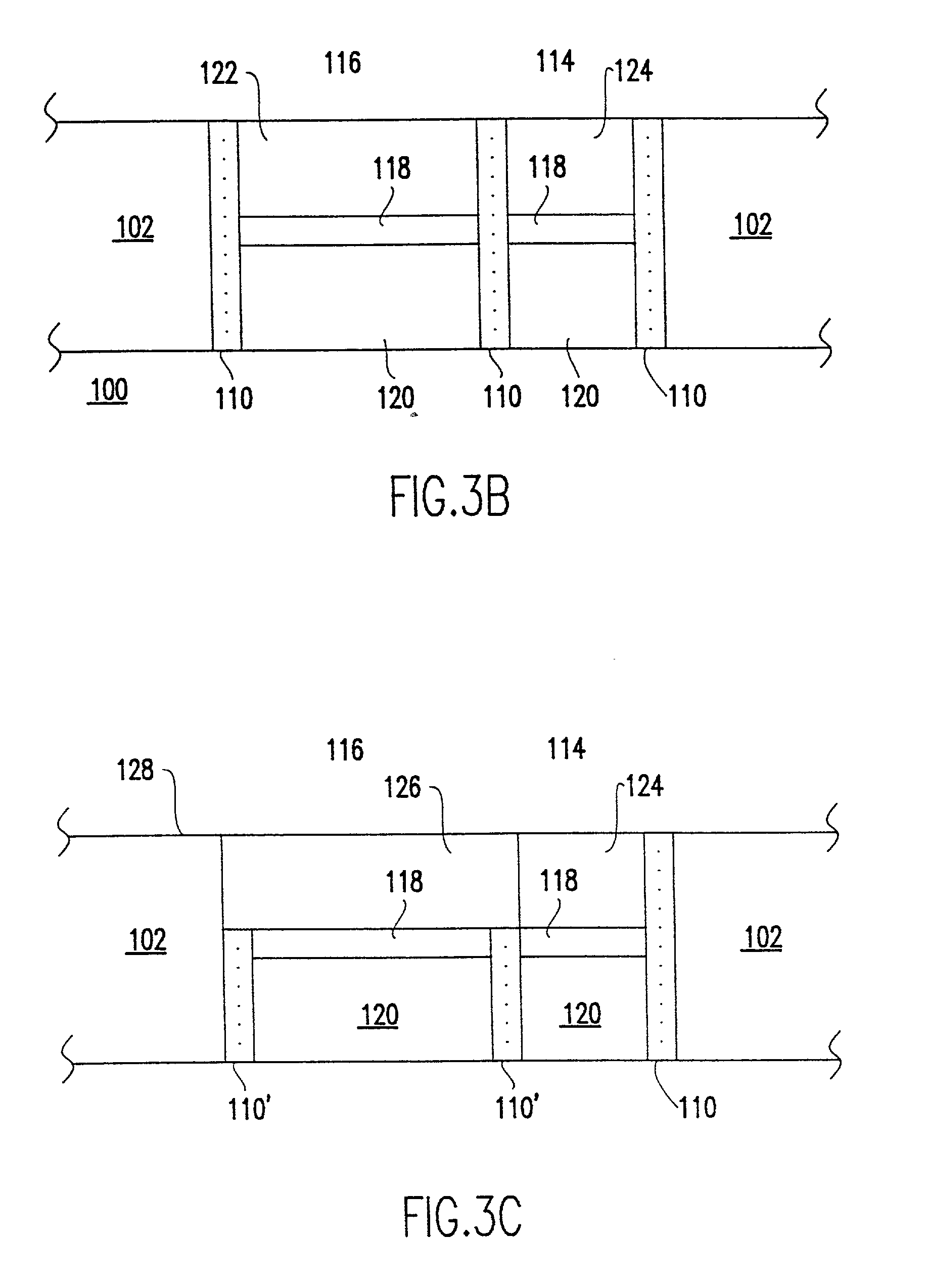

[0038] Preferred embodiment FETs are formed on the surface of a semiconductor wafer, preferably a silicon wafer. A layered dielectric is formed on a surface of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More