Anti-radiation hardening latch based on TMR and DICE

A radiation hardening, three-mode redundancy technology, applied in electrical components, logic circuits, pulse technology, etc., can solve the problems of SET can not be eliminated, large area and power consumption overhead, etc., to reduce power consumption, area and power consumption reduced effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

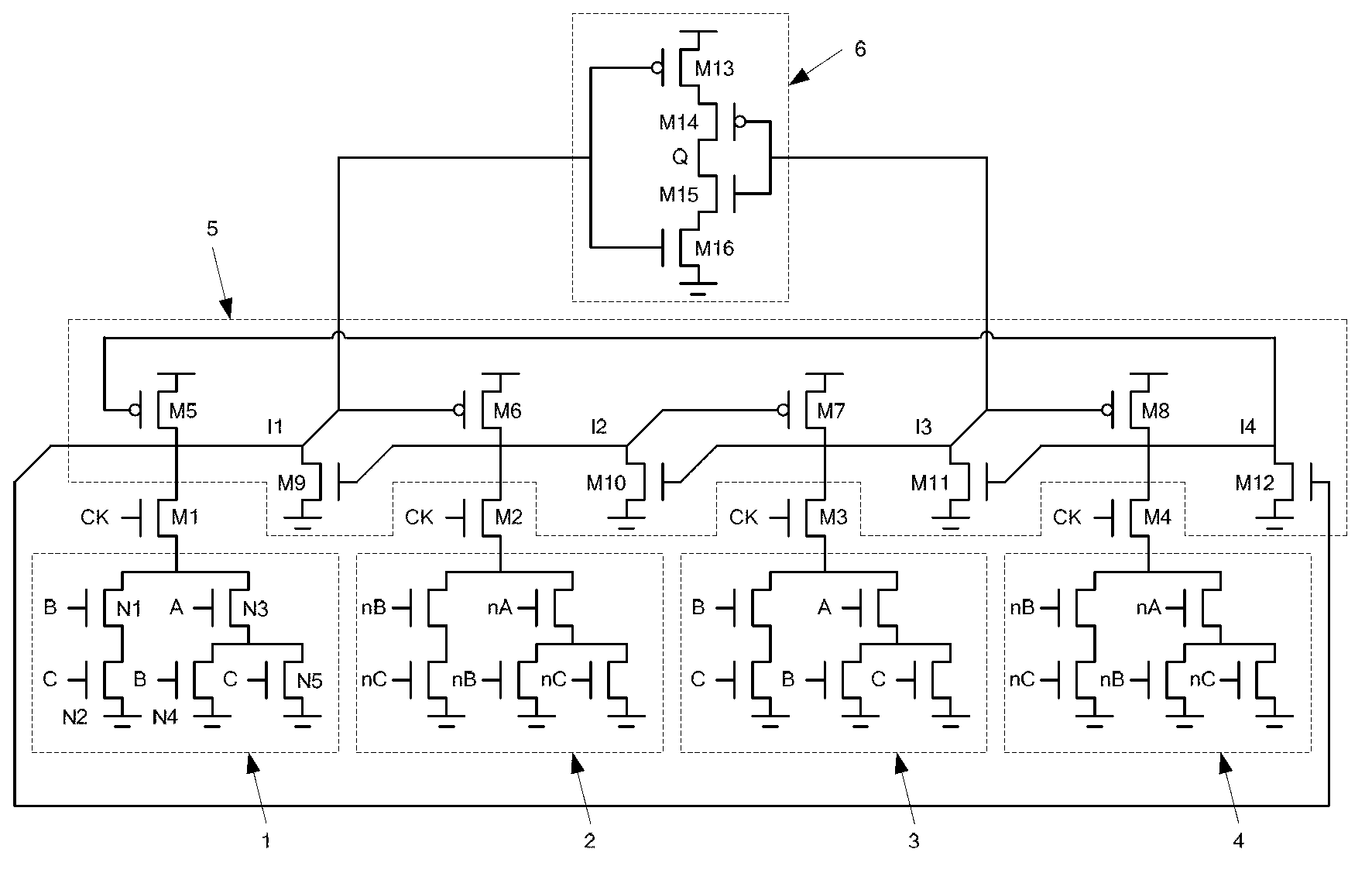

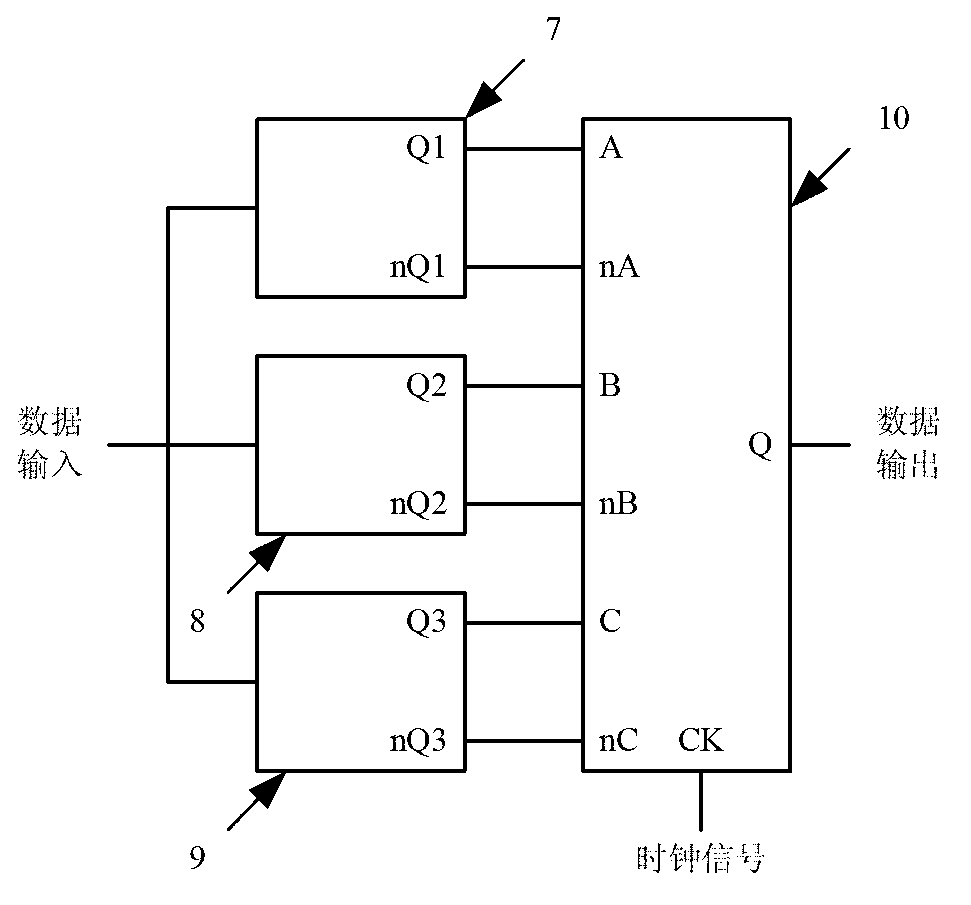

[0013] The technical scheme adopted by the present invention is: the input stage is composed of four voting modules 1, 2, 3, and 4. The source terminal of the N-type transistor N1 is connected to the drain terminal of the N-type transistor N2, and the source terminal of the N2 is grounded. The drain terminal of the N-type transistor N3 is connected with the drain terminal of N1, the source terminal of N3 is connected with the drain terminals of the N-type transistors N4 and N5, and the source terminals of N4 and N5 are grounded. The input signal A controls the gate terminal of N3, the input signal B controls the gate terminal of N1 and N4, and the input signal C controls the gate terminal of N2 and N5. N1, N2, N3, N4, and N5 constitute voting module 1, and the drain terminal of N1 is the output node of voting module 1. The structure of voting modules 2, 3, 4 is the same as that of voting module 1. The gate of each transistor in voting module 3 is connected to the gate of the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More