An anti-SEU storage cell circuit in an anti-radiation hardening FPGA chip

A storage unit circuit, anti-radiation hardening technology, applied in information storage, static memory, digital memory information and other directions, can solve the problems of inability to meet the needs of anti-radiation FPGA chips, high resistance noise and power consumption, and less use of circuits. Enhance the ability to resist single-event flipping, improve anti-single-event flipping ability, and increase the effect of current pulse time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

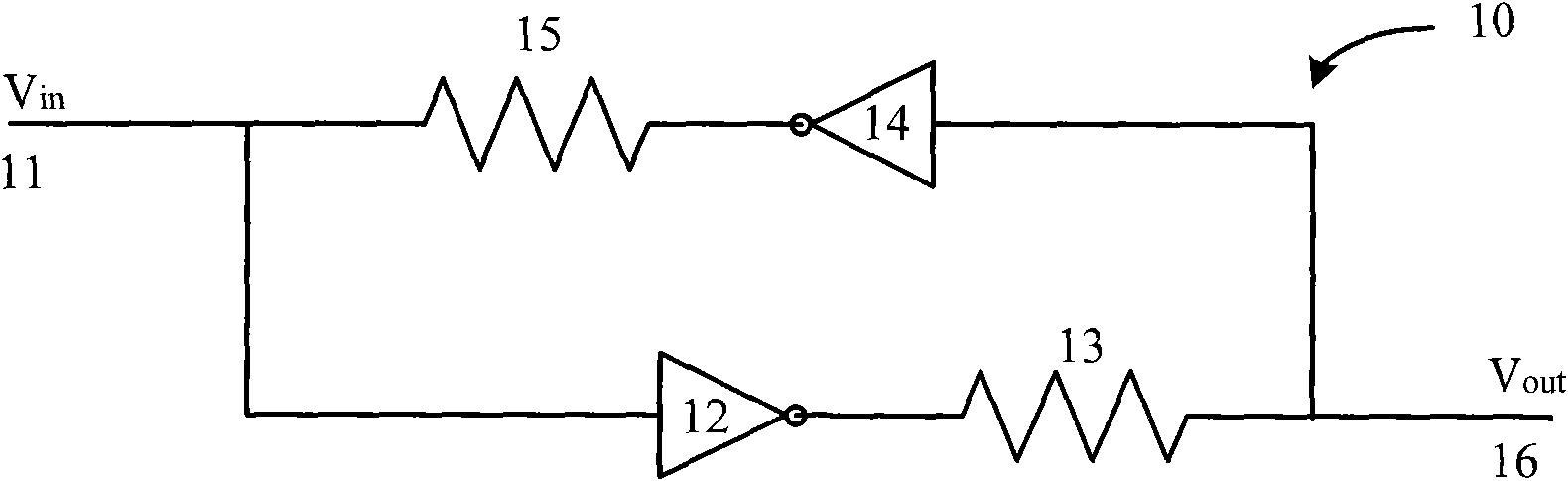

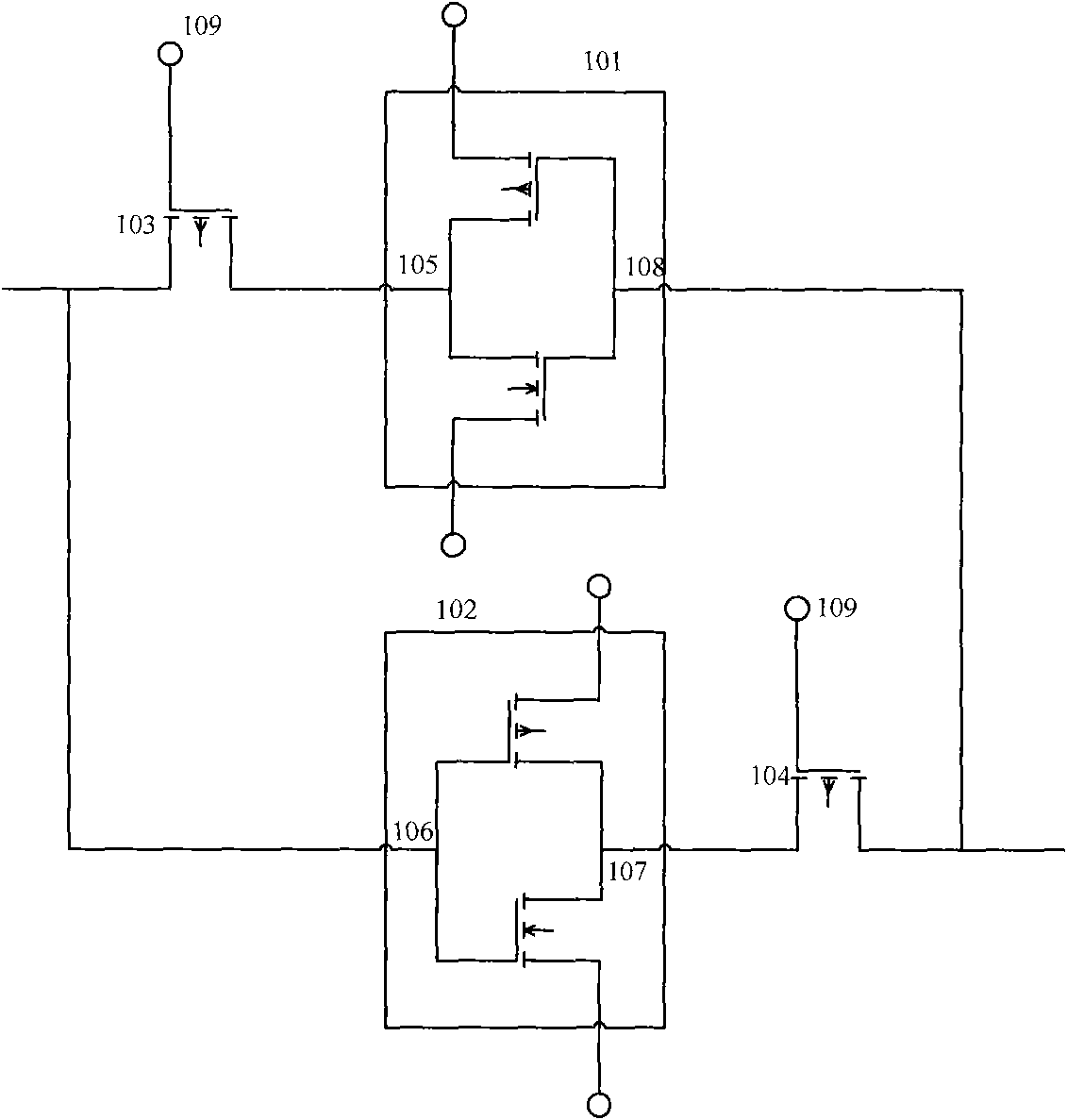

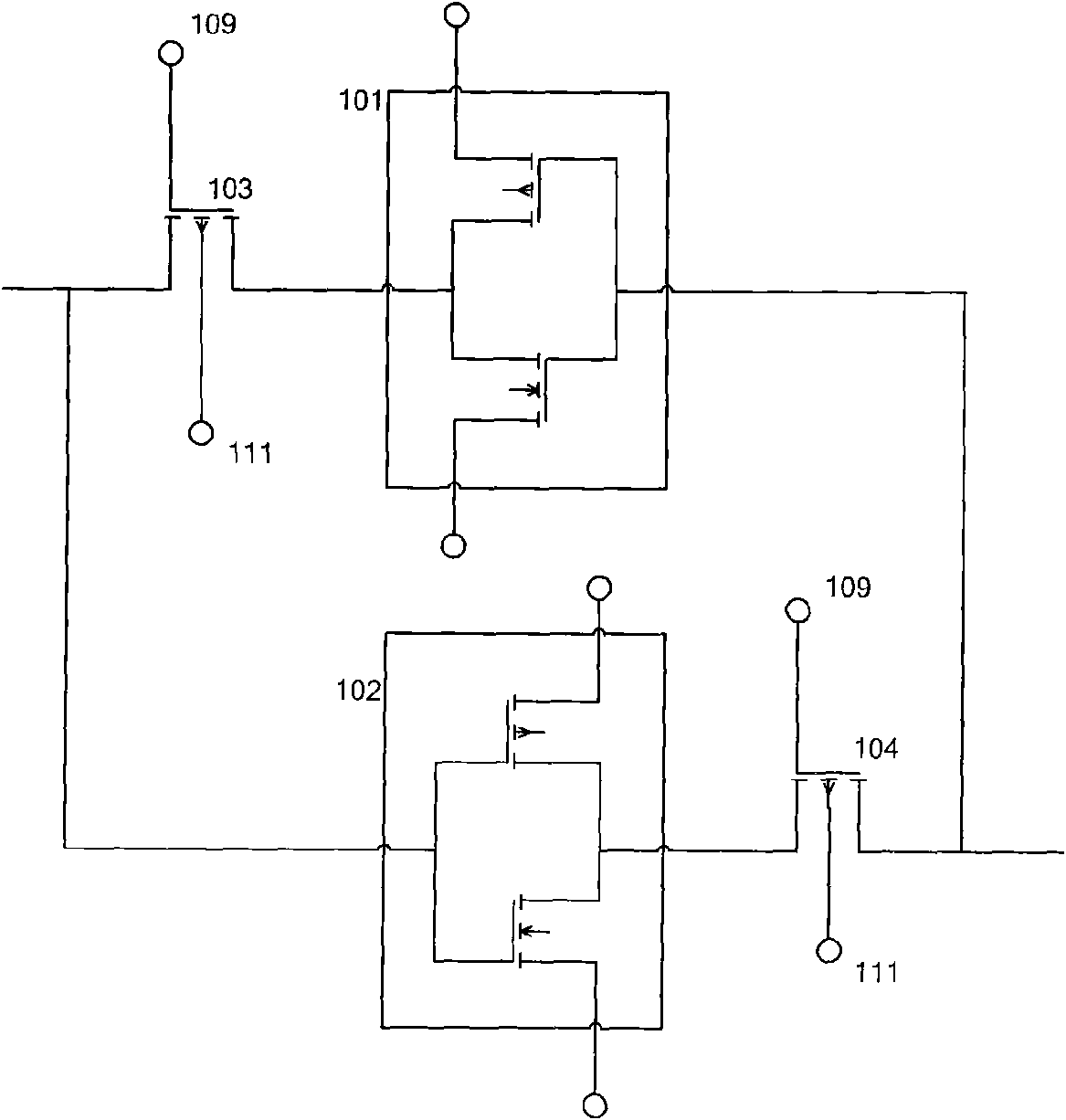

[0026] Such as Figure 5 As shown, it is a design schematic diagram of the storage circuit against single event upset in the FPGA chip of the present invention. Figure 5 The circuit diagram shown is an improved radiation-hardened CMOS SRAM memory cell, including a first inverter 501, a second inverter 502, a first transistor 503, and a second transistor 504, and the source terminal and drain terminal of the first transistor 503 are One end of the transistor is connected to the output terminal 505 of the first inverter 501, and the other end is connected to the input terminal 506 of the second inverter 502; one end of the source terminal and the drain terminal of the second transistor 504 is connected to the first inverter The input terminal 508 of 501, the other end is connected to the output terminal 507 of the second inverter 502; The input terminal 508 of the first inverter 501 and the input terminal 506 of the second inverter 502 are used as the data input and output of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More