Patents

Literature

35results about How to "Improved resistance to single event upset" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

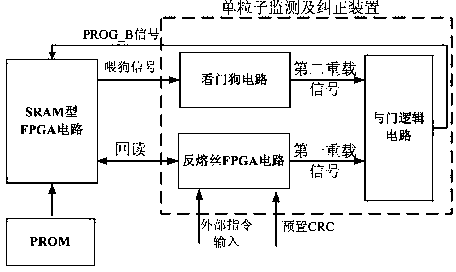

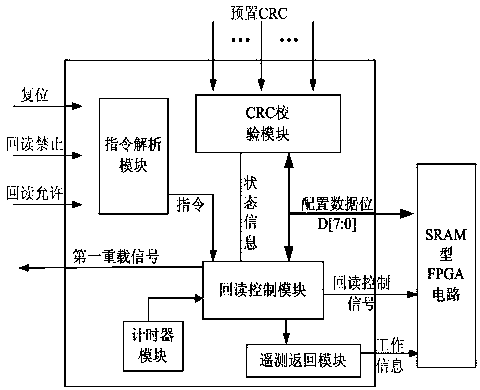

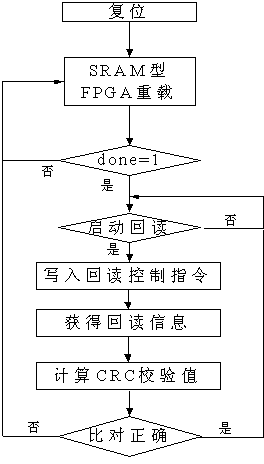

Monitoring and correcting device for single event upset fault of satellite borne spread spectrum responder

InactiveCN104021051AAvoid Performance Metrics DegradationAvoid functioFault responseComputer moduleSingle event upset

The invention discloses a monitoring and correcting device for a single event upset fault of a satellite borne spread spectrum responder. The monitoring and correcting device is used for monitoring and correcting a communication processing module of the satellite borne spread spectrum responder. The monitoring and correcting device is characterized by comprising an anti-fuse FPGA circuit, a watchdog circuit and an AND gate logic circuit, the anti-fuse FPGA circuit is used for conducting backward reading, backward reading information comparing and heavy load judging on the configuration information of the communication processing module and used for sending first heavy load signals to the AND gate logic circuit, the watchdog circuit is used for sending second heavy load signals to the AND gate logic circuit according to feed dog signals sent by the communication processing module, and the AND gate logic circuit is used for conducting AND logic operation on the received first heavy load signals and the received second heavy load signals and sending heavy load enabling signals to the communication processing module according to AND results.

Owner:SHANGHAI SPACEFLIGHT ELECTRONICS & COMM EQUIP RES INST

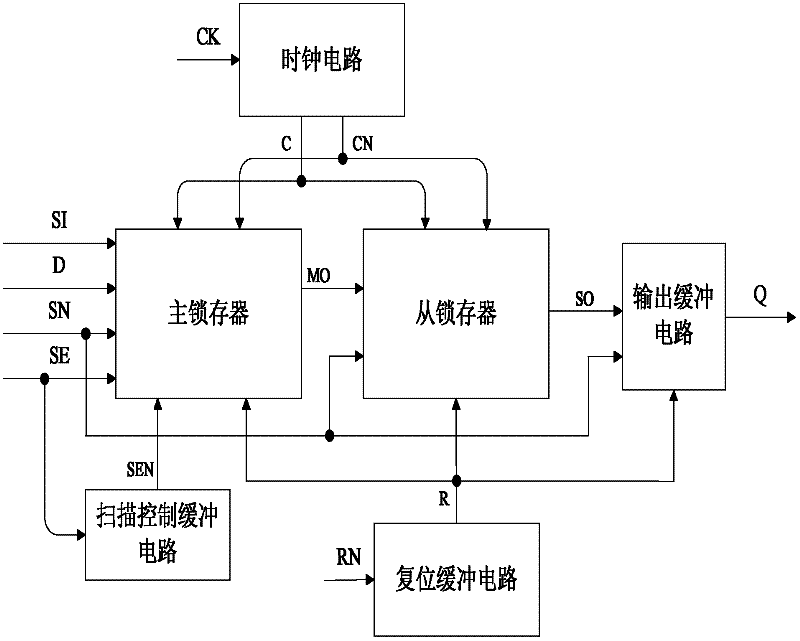

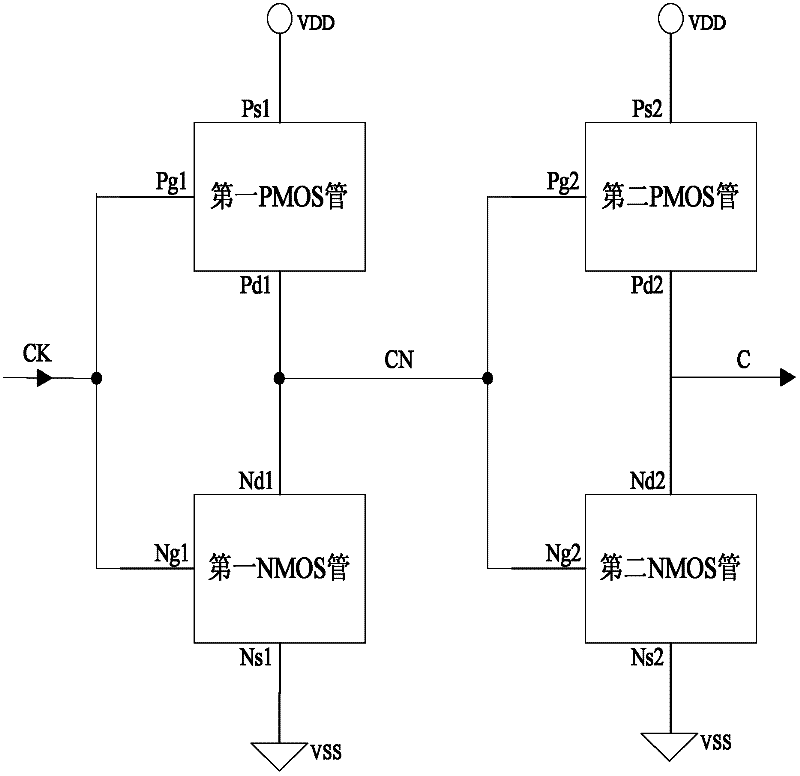

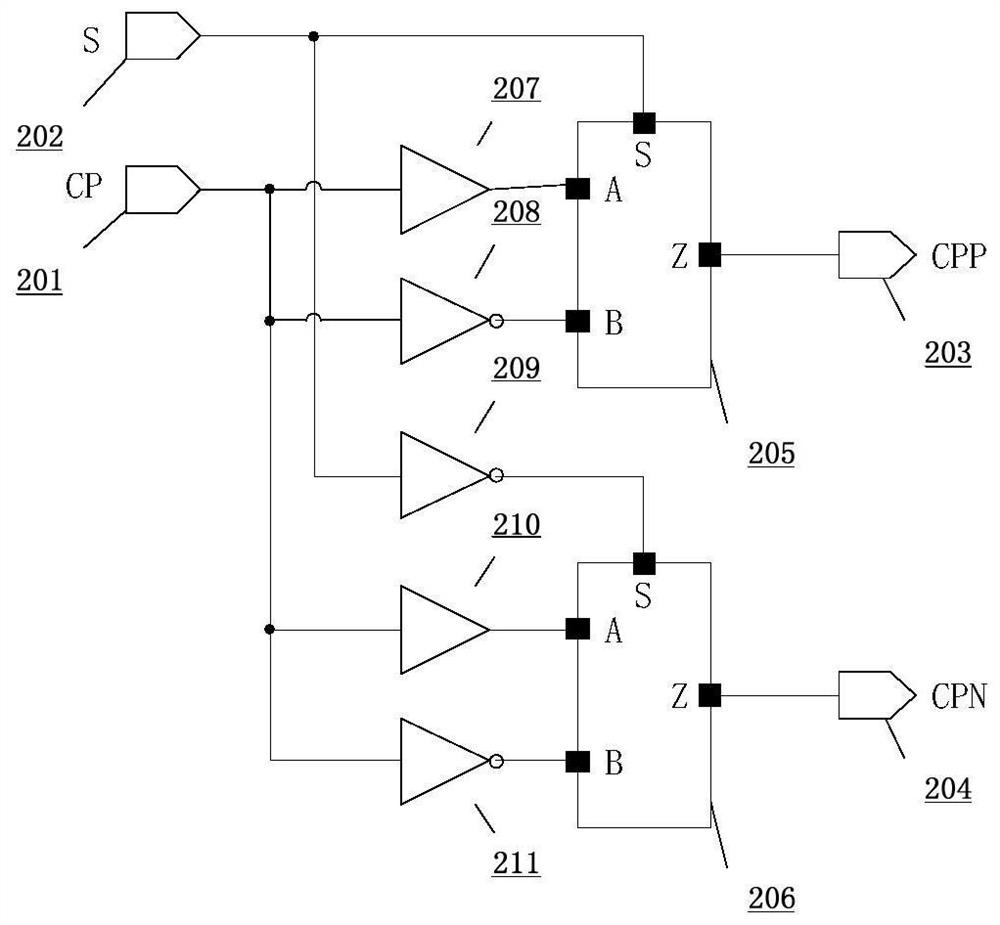

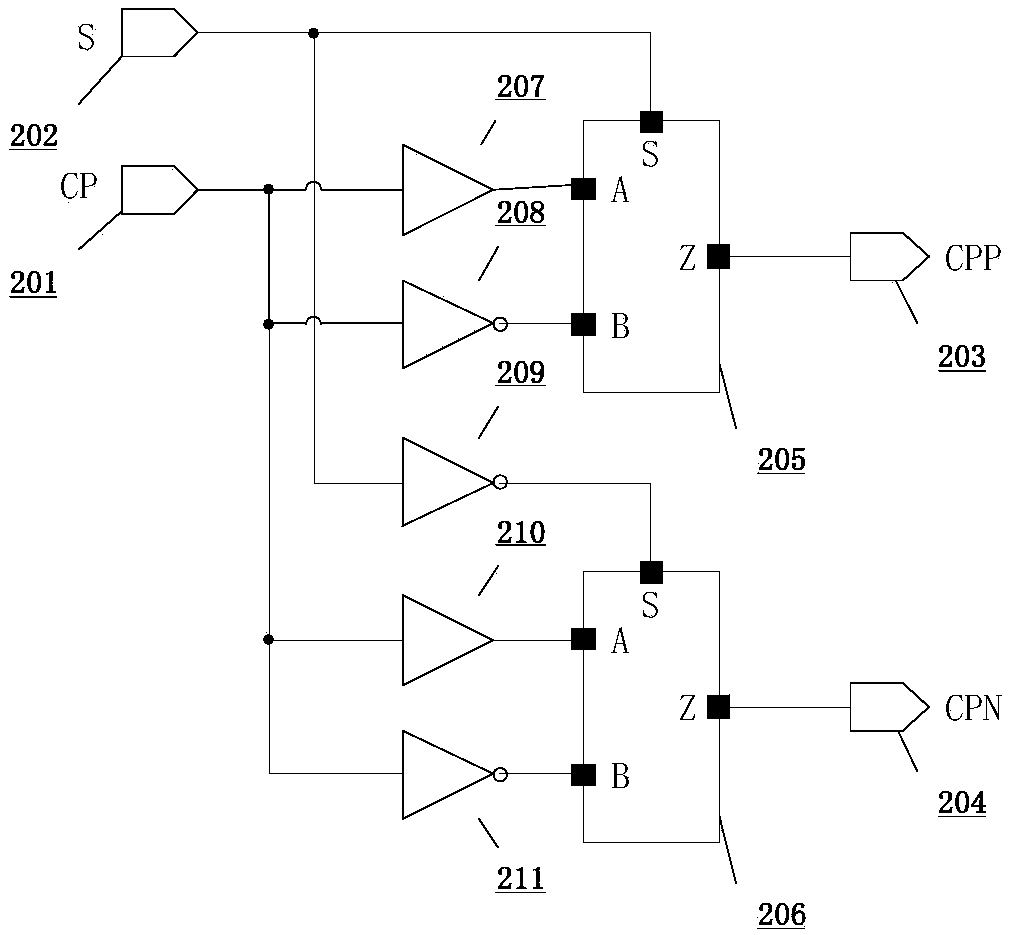

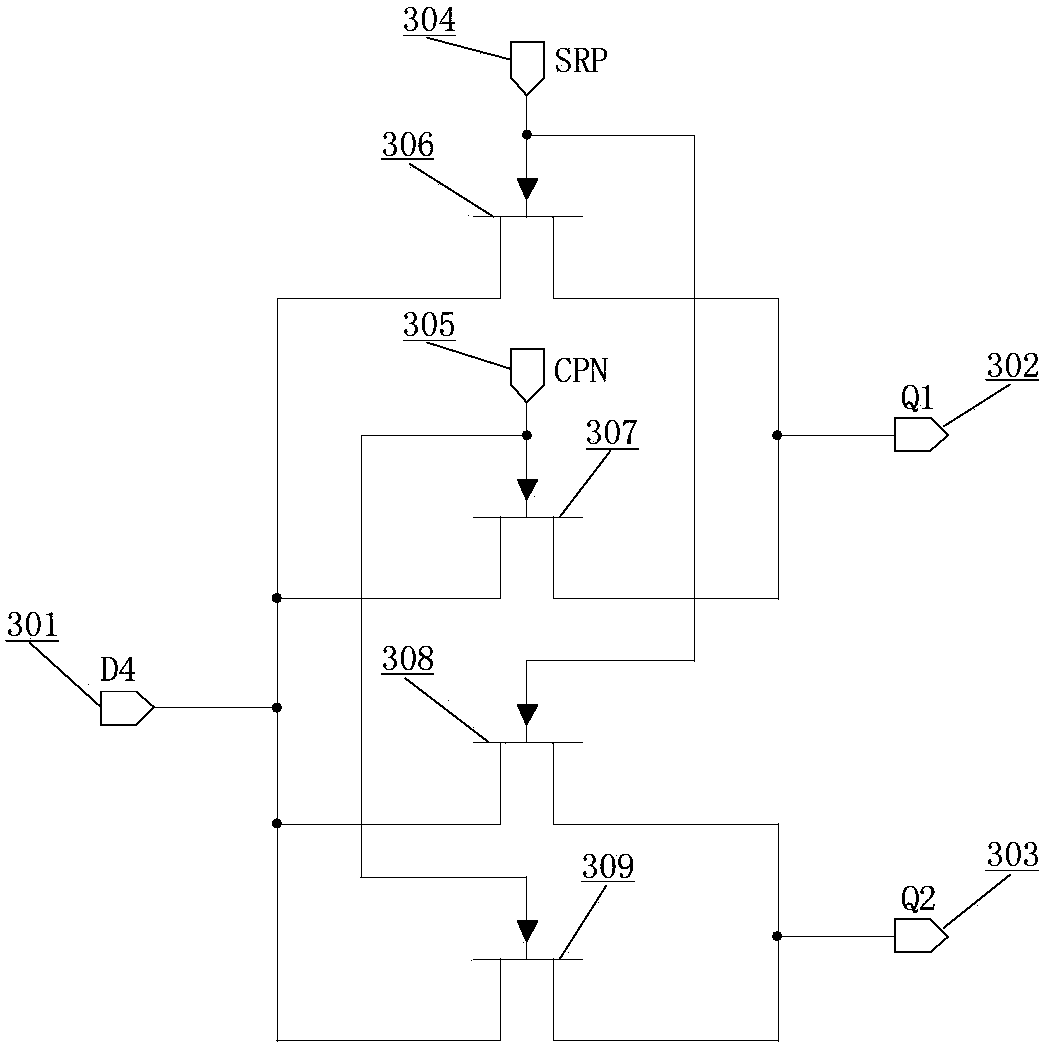

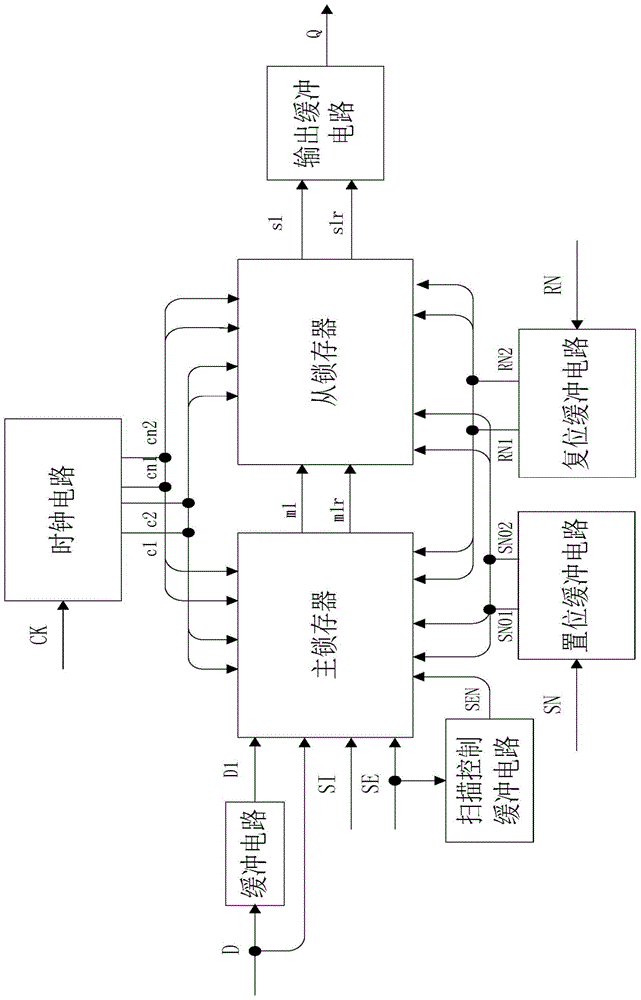

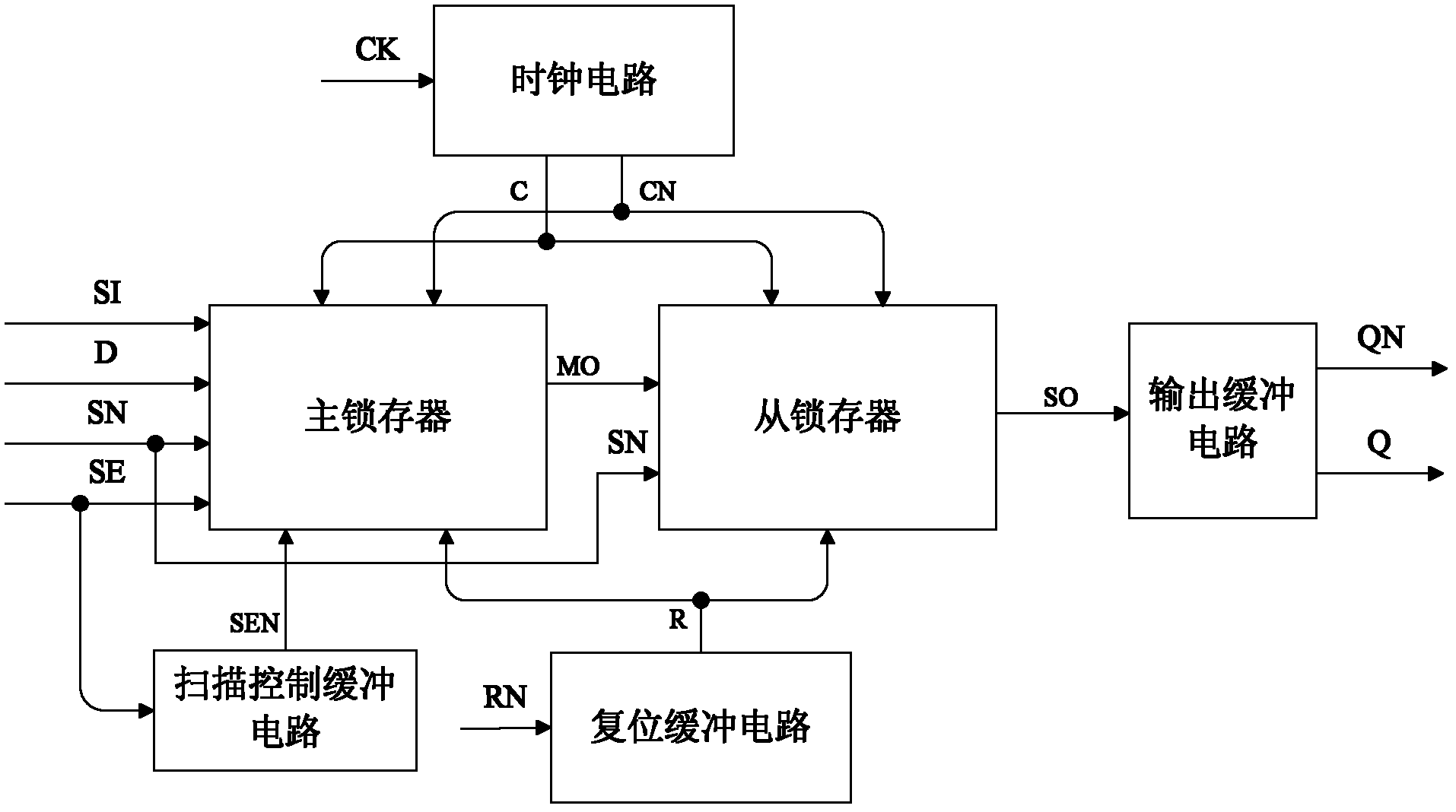

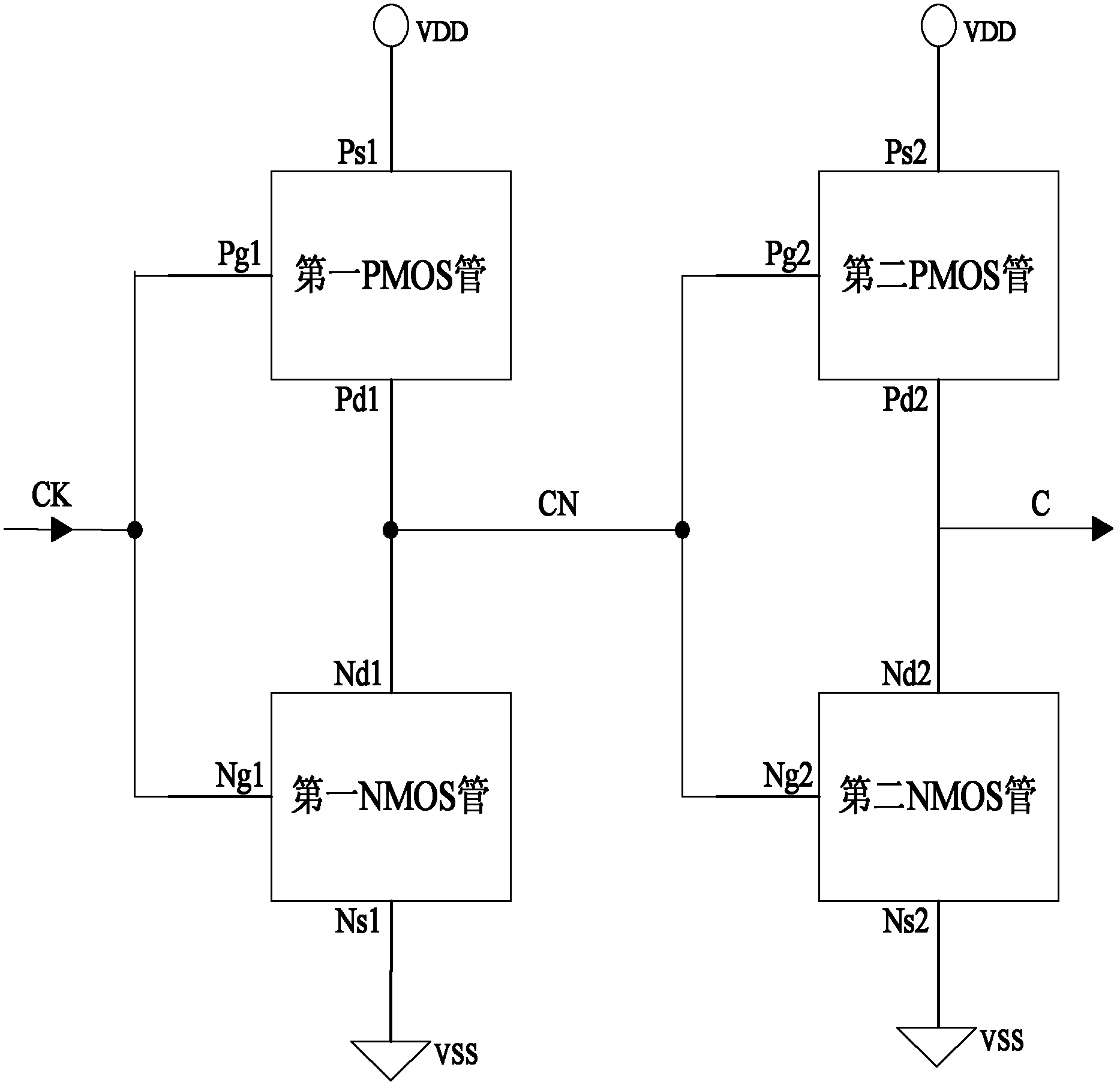

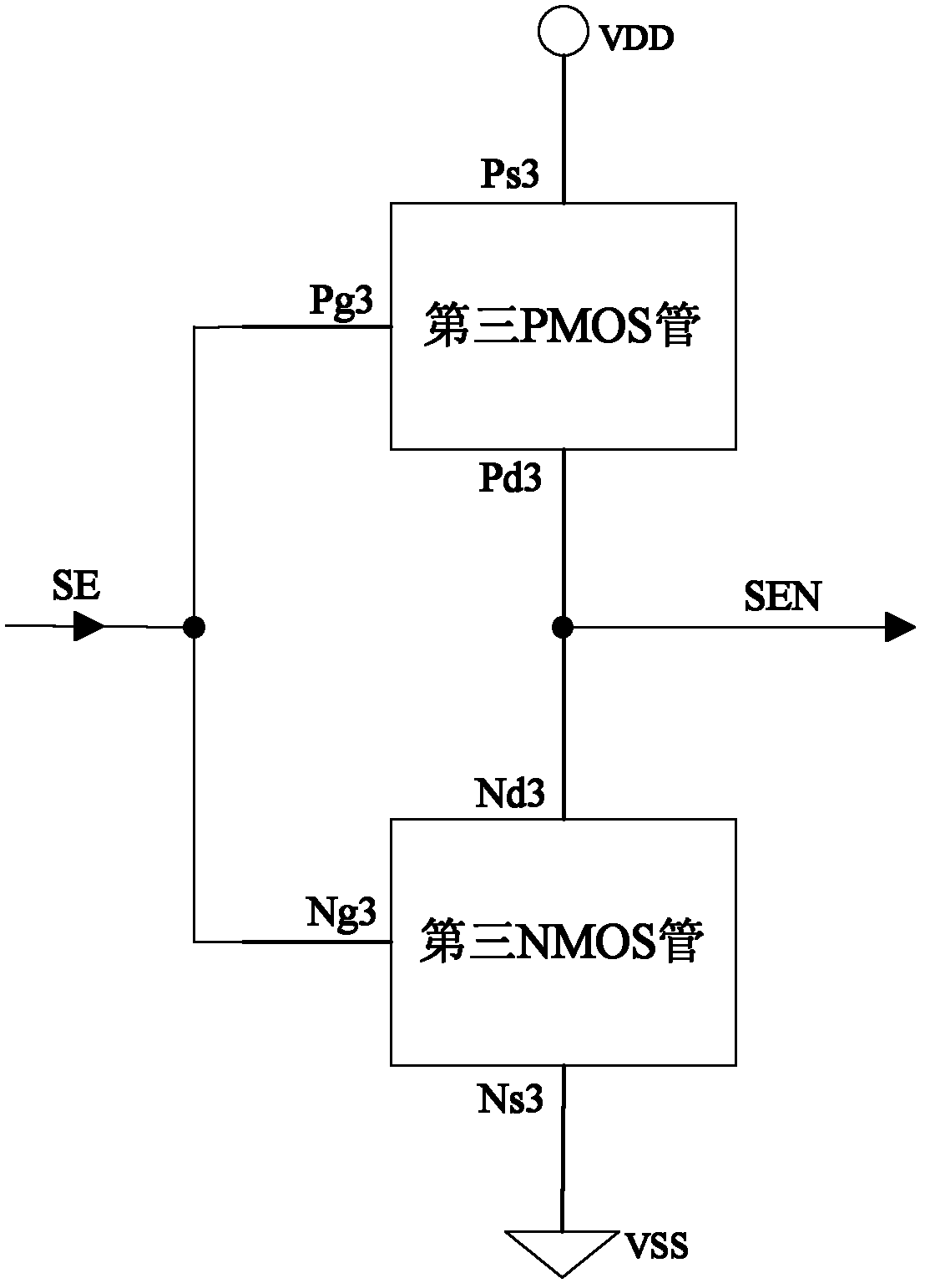

Single event upset-resisting scanning structure D trigger capable of setting and resetting

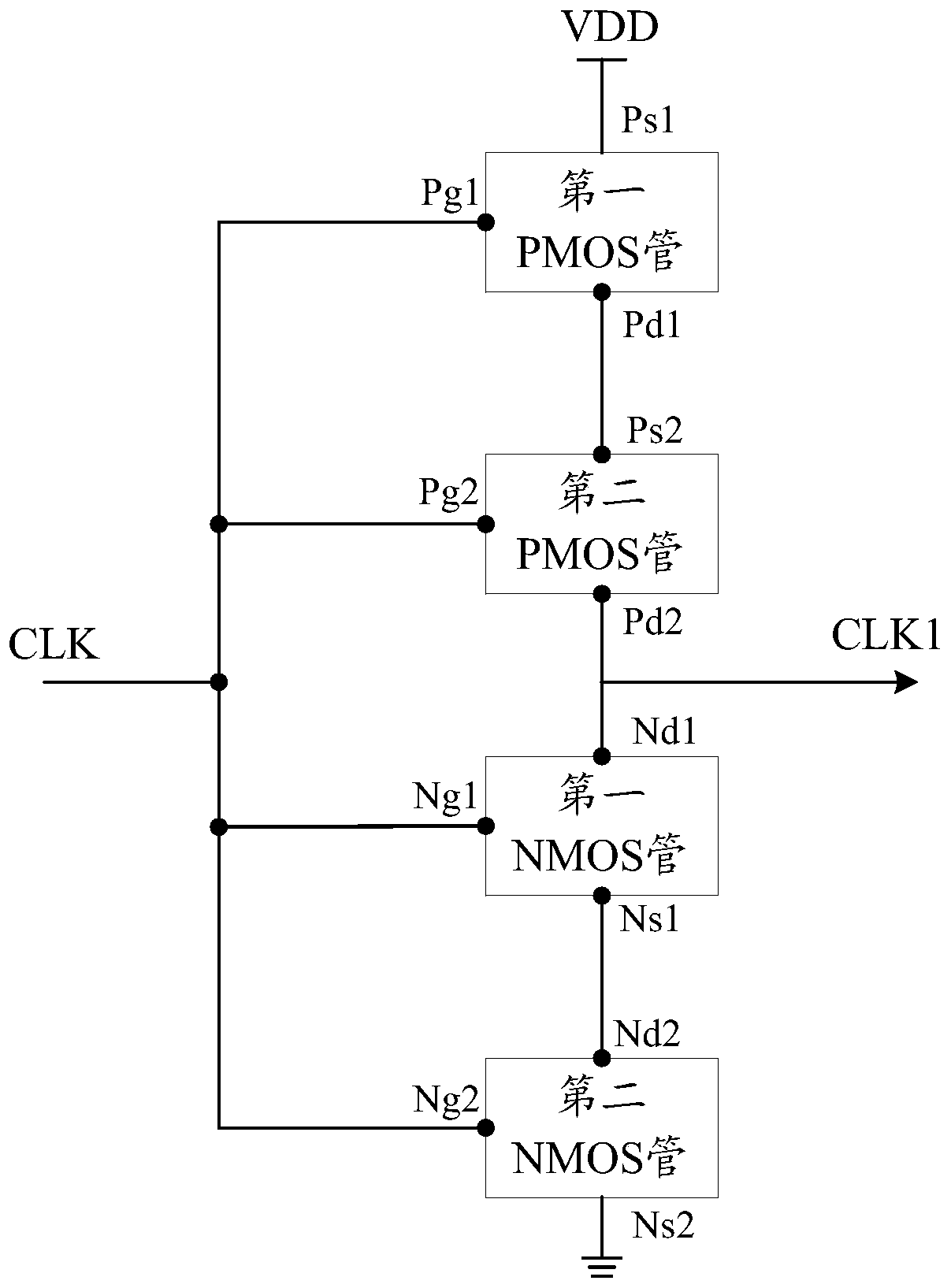

ActiveCN102394602AExcellent anti-single event upset abilityImproved resistance to single event upsetElectric pulse generator circuitsAviationSingle event upset

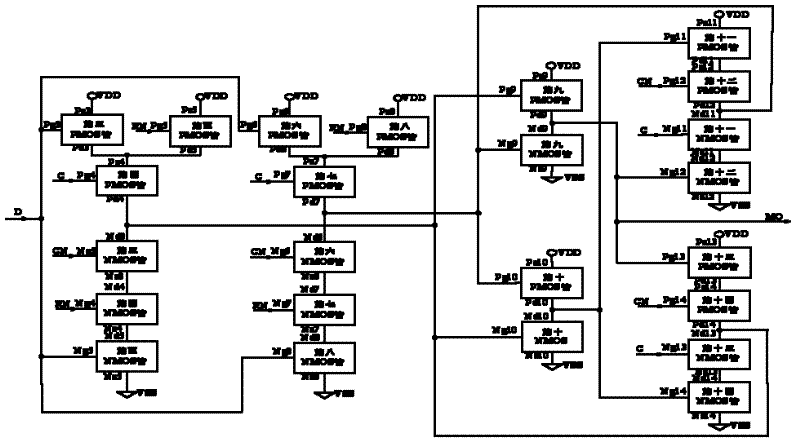

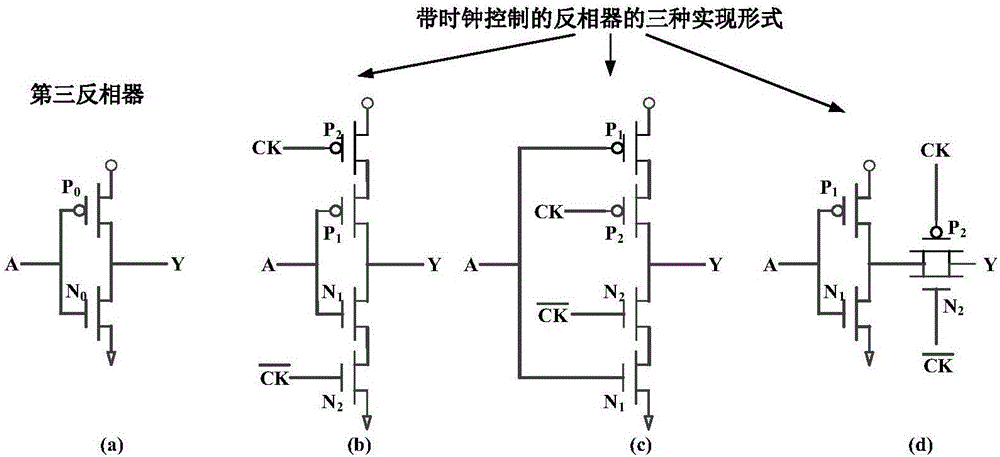

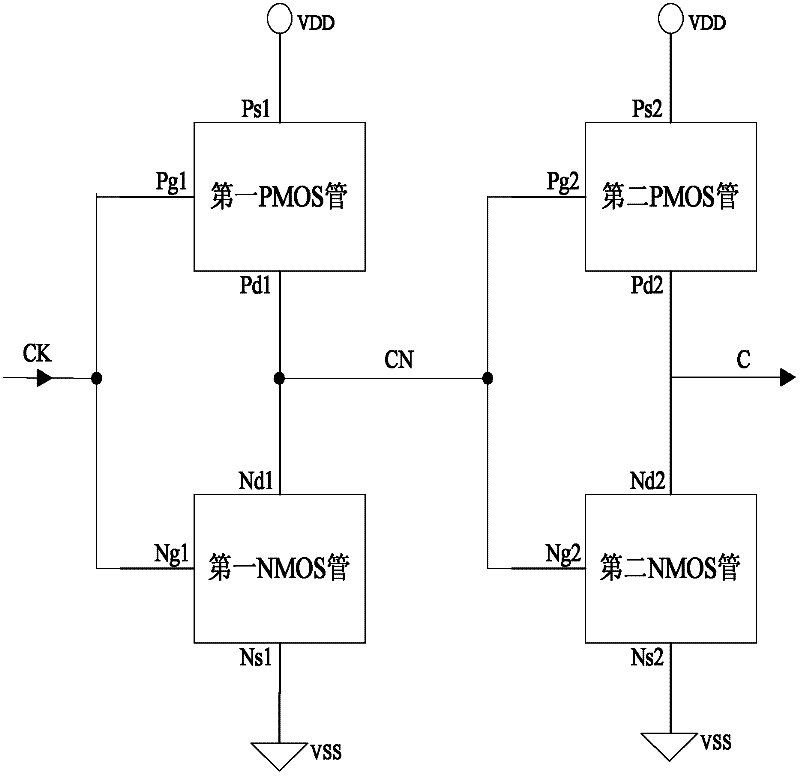

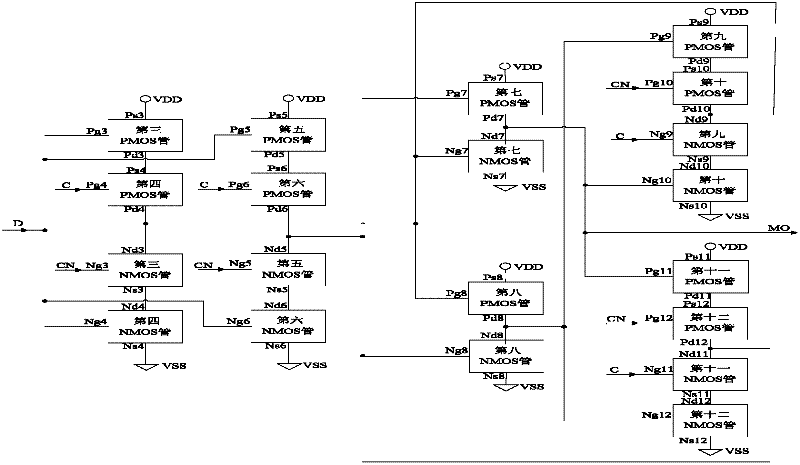

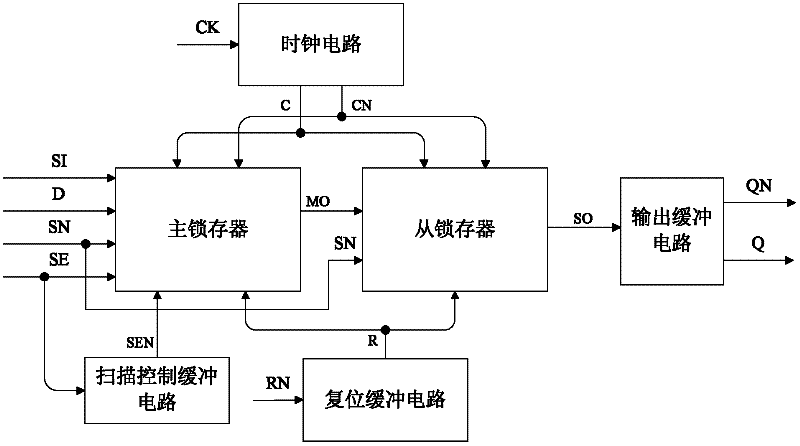

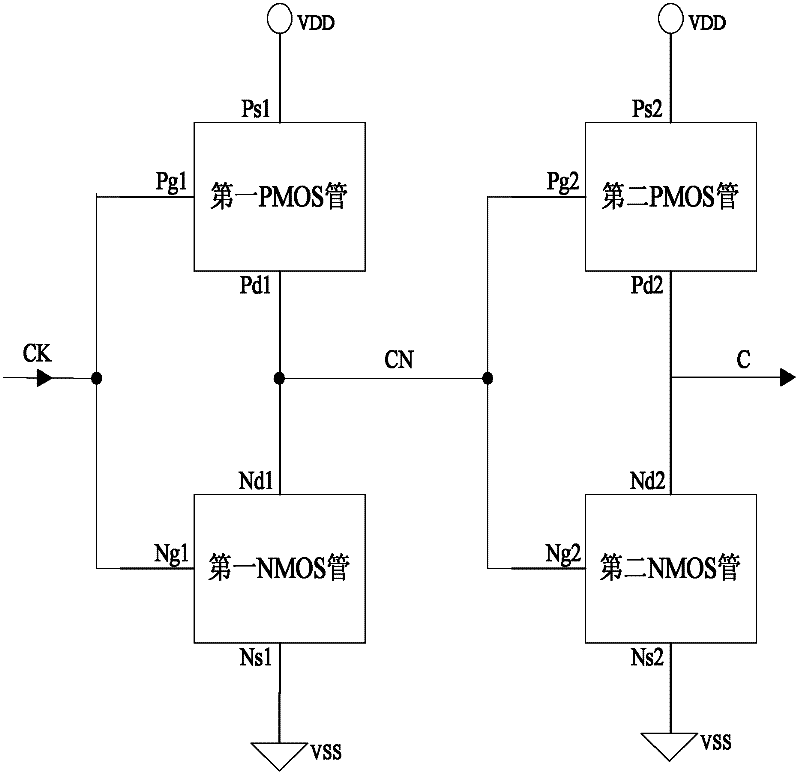

The invention discloses a single event upset-resisting scanning structure D trigger capable of setting and resetting, which aims at improving the single event upset-resisting capability of the single event upset-resisting scanning structure D trigger. The trigger comprises a clock circuit, a scanning control buffer circuit, a resetting buffer circuit, a main latch, a slave latch and an output buffer circuit, wherein the main latch comprises twenty PMOS (P-channel metal oxide semiconductor) tubes and twenty NMOS (N-channel metal oxide semiconductor) tubes, the slave latch comprises ten PMOS tubes and ten NMOS tubes, double-die redundant strengthening is carried out on the main latch and the slave latch respectively, and a C2MOS circuit structure in the main latch is improved, namely upper pulling circuits and lower pulling circuits in the C2MOS circuits which are mutually redundant. The single event upset-resisting scanning structure D trigger has strong single event upset-resisting capability, suitable for a standard unit library of a single event upset-resisting strengthening integrated circuit, and applied to the fields of aviation, spaceflight and the like.

Owner:NAT UNIV OF DEFENSE TECH

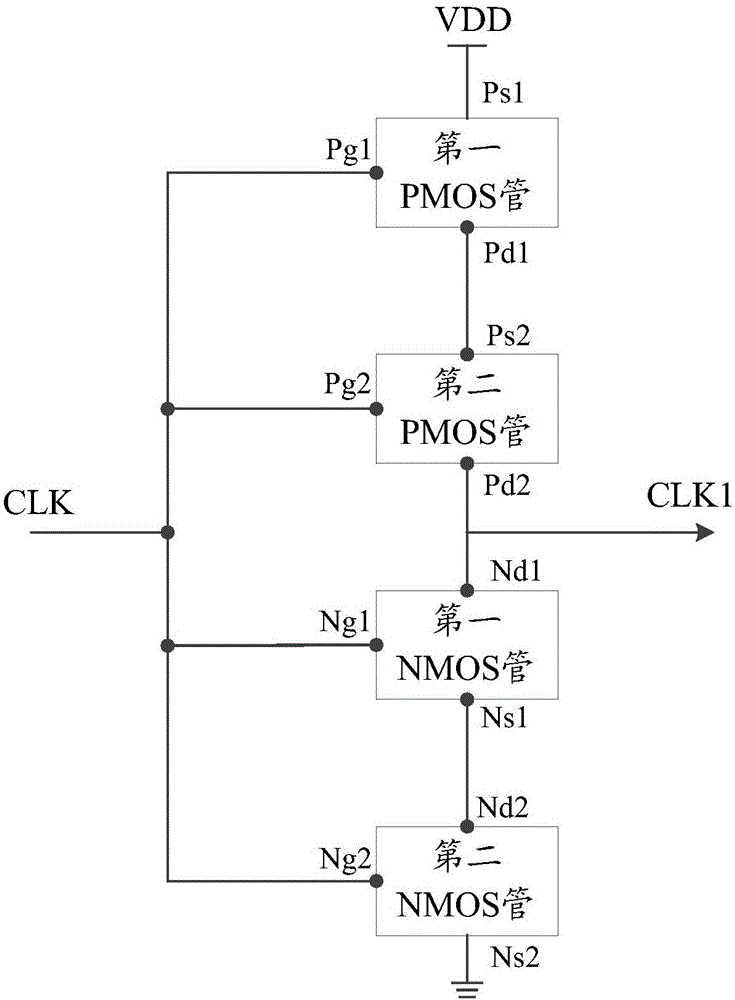

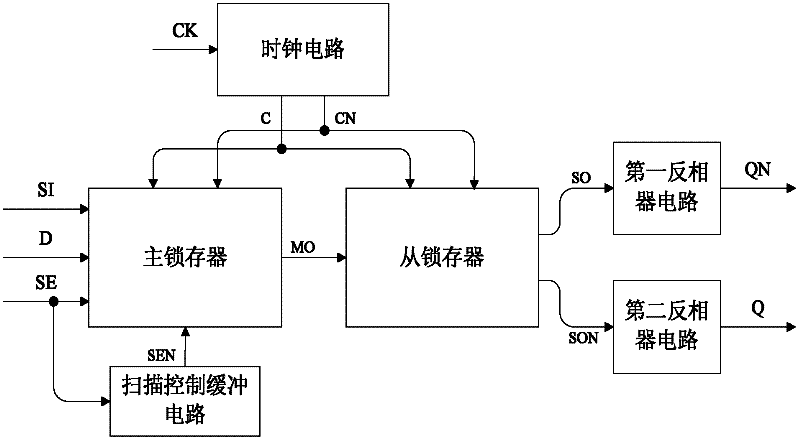

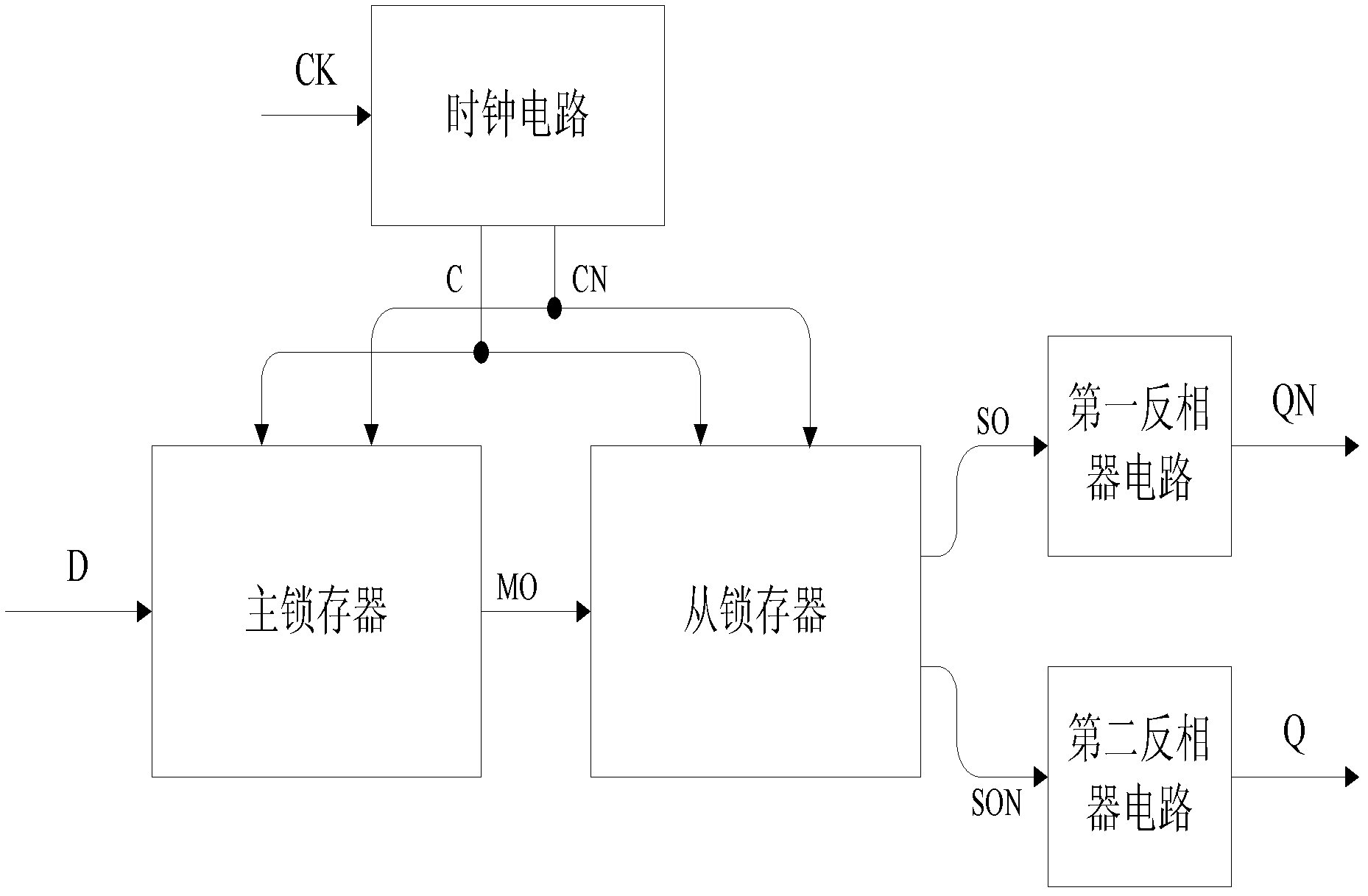

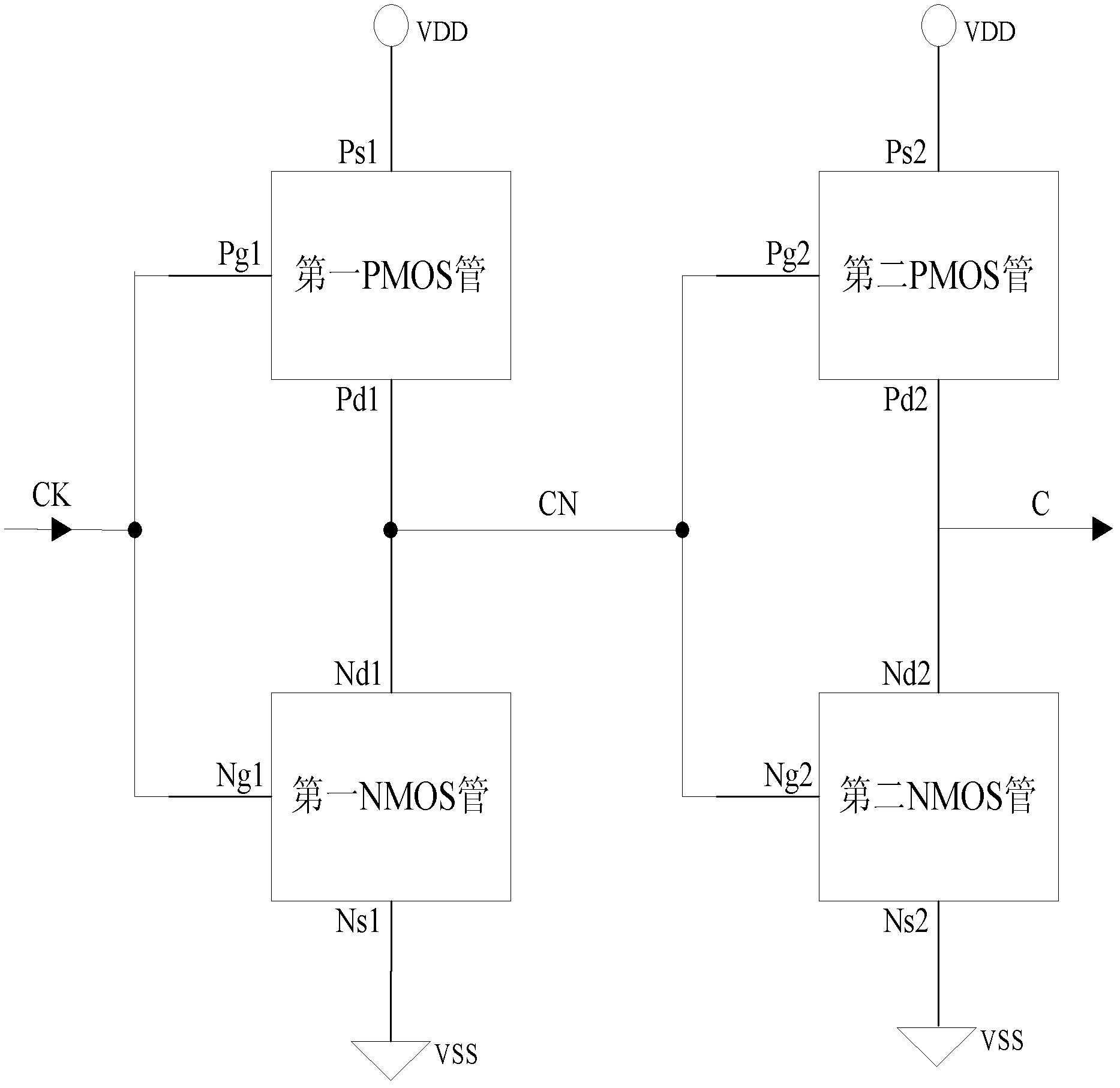

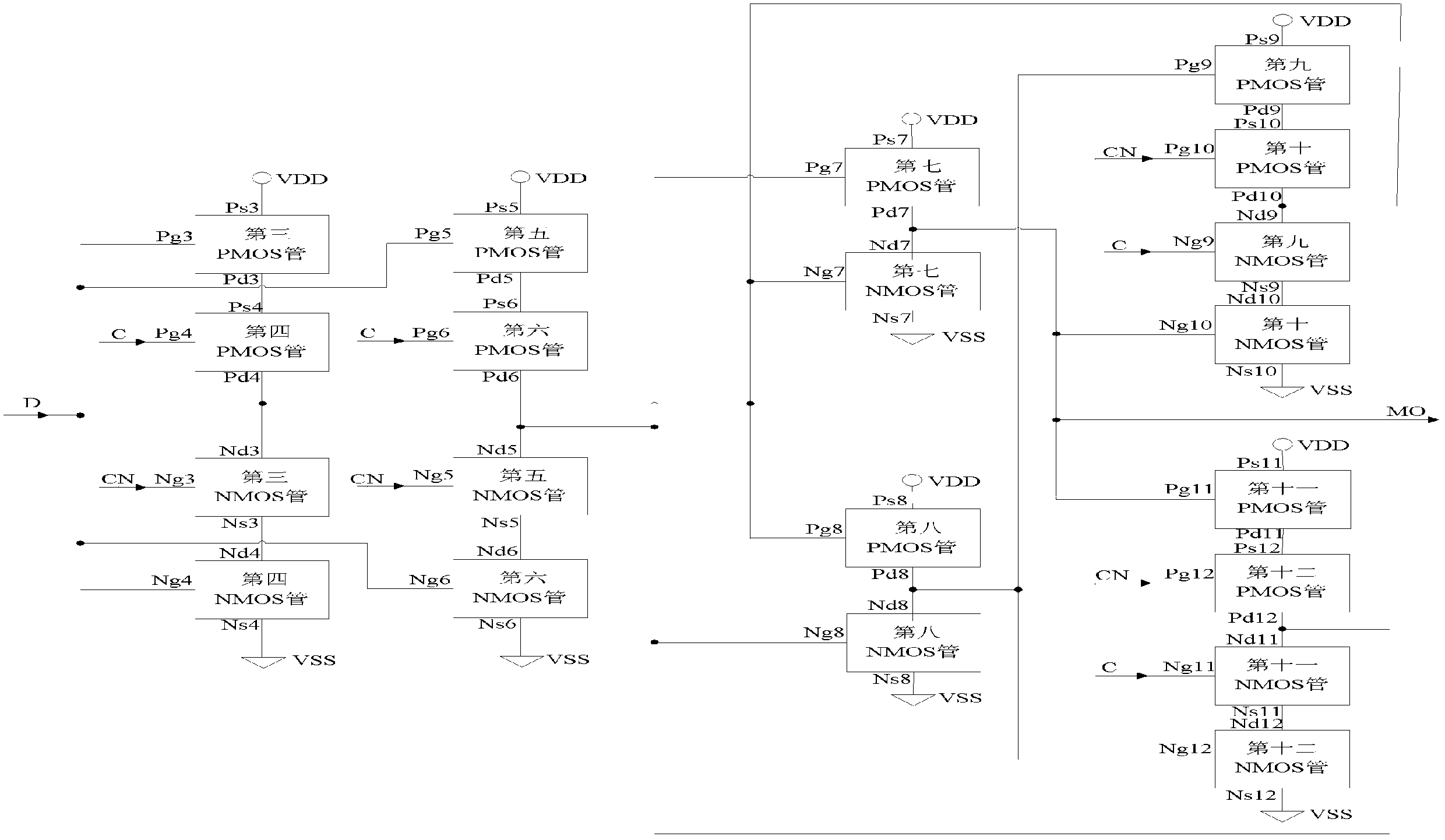

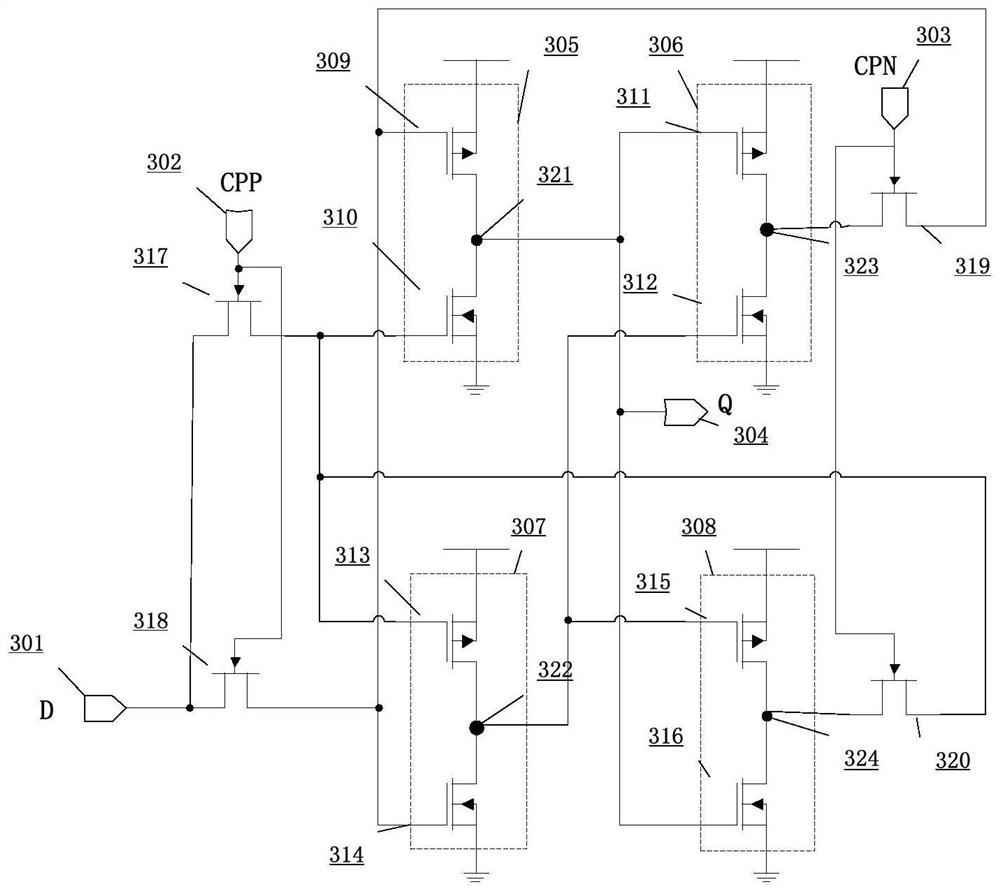

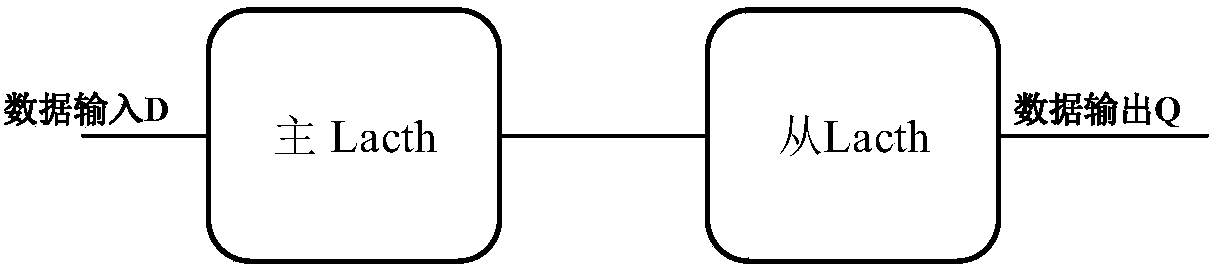

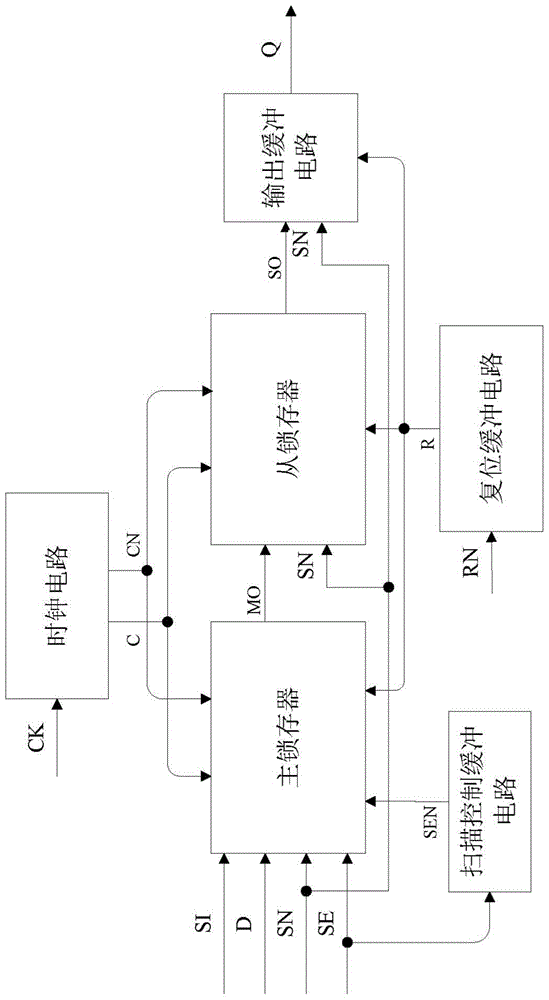

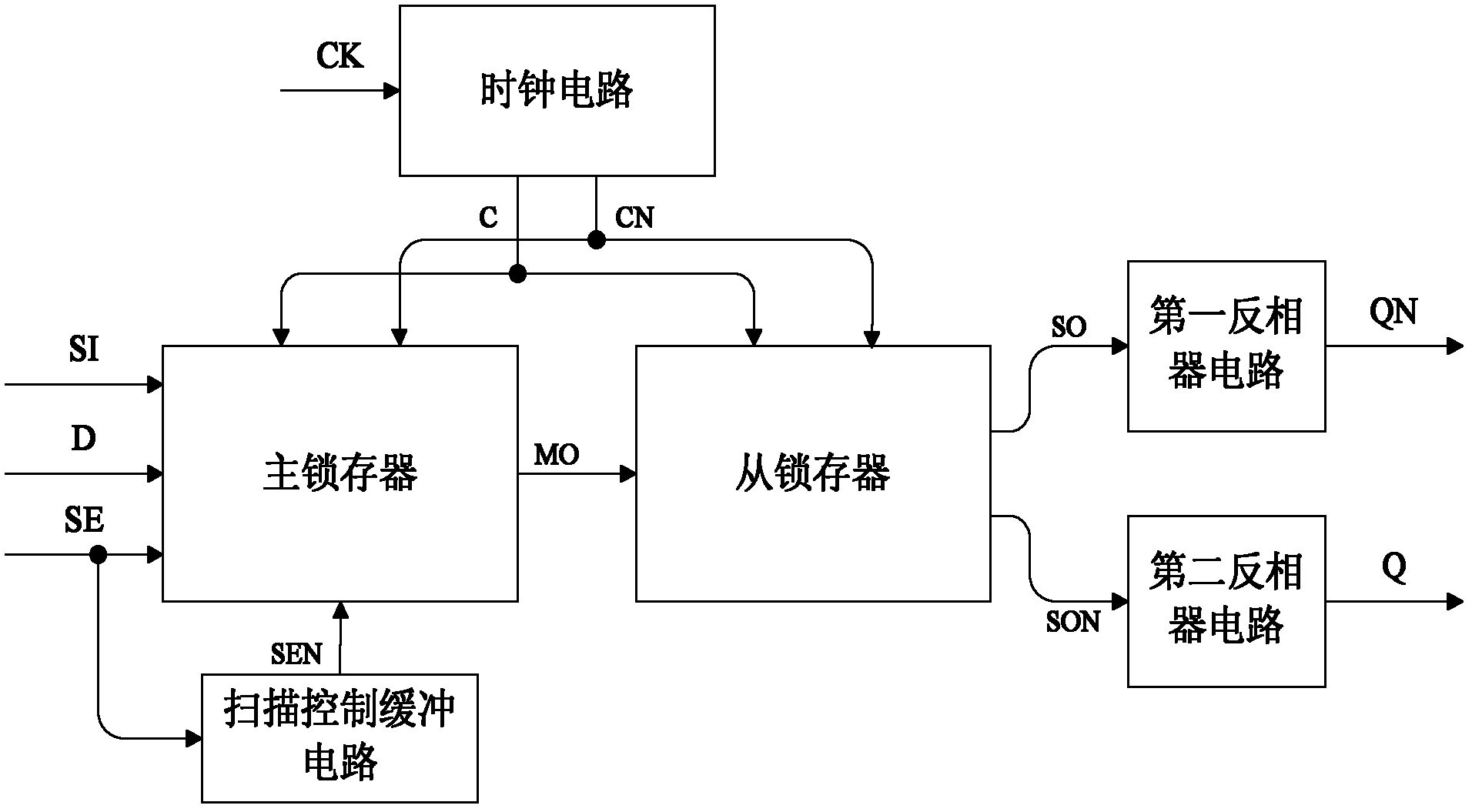

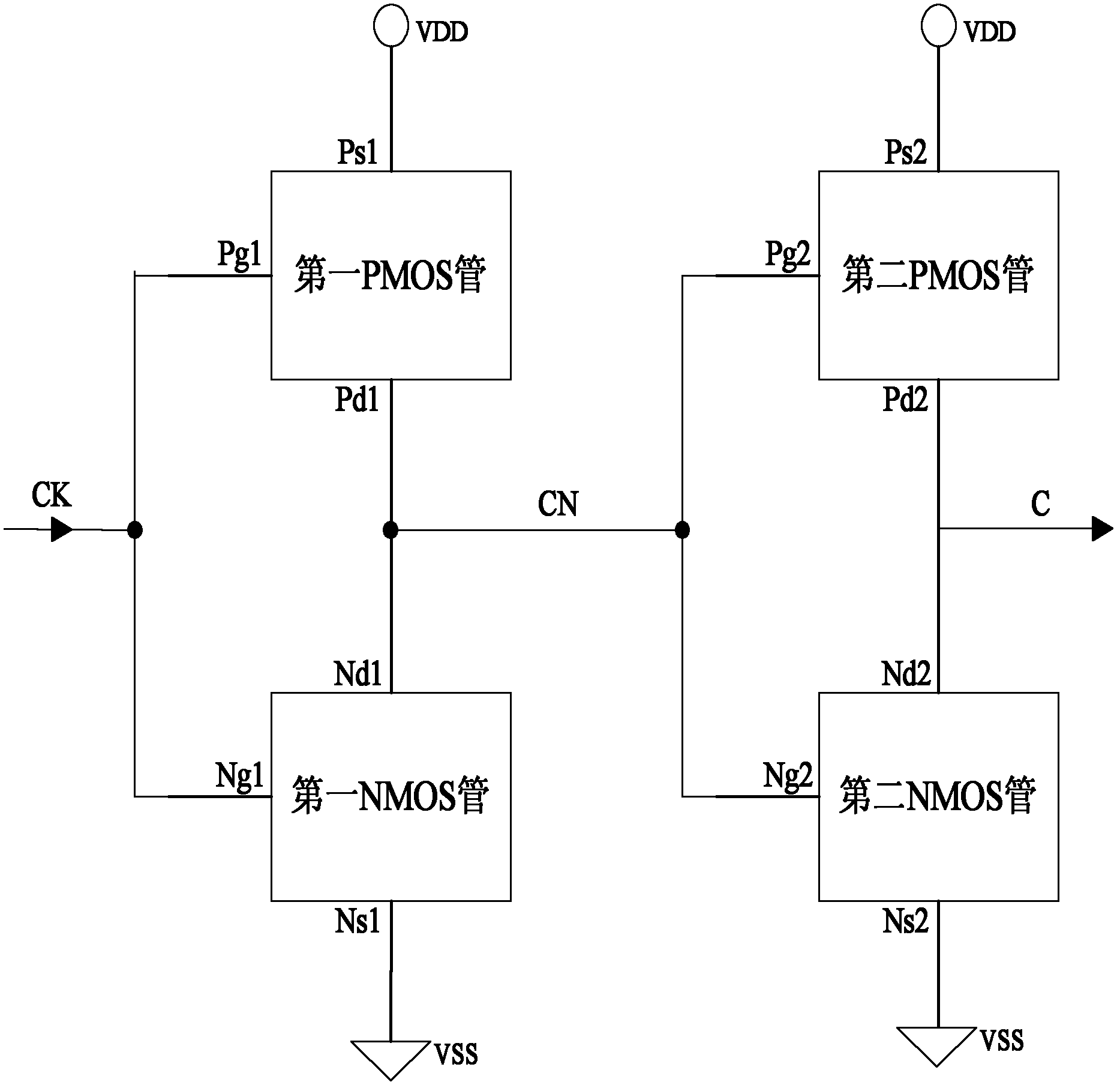

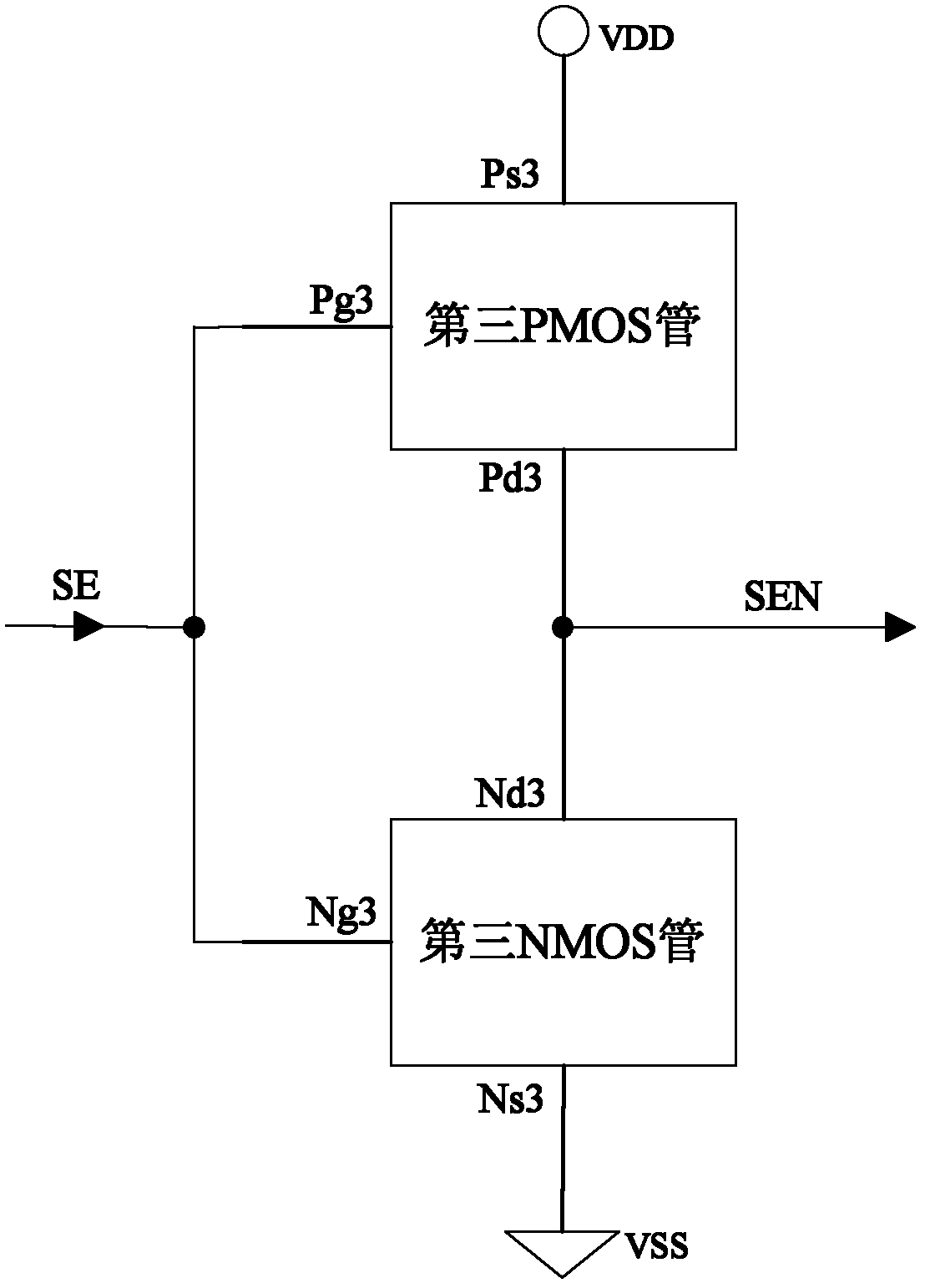

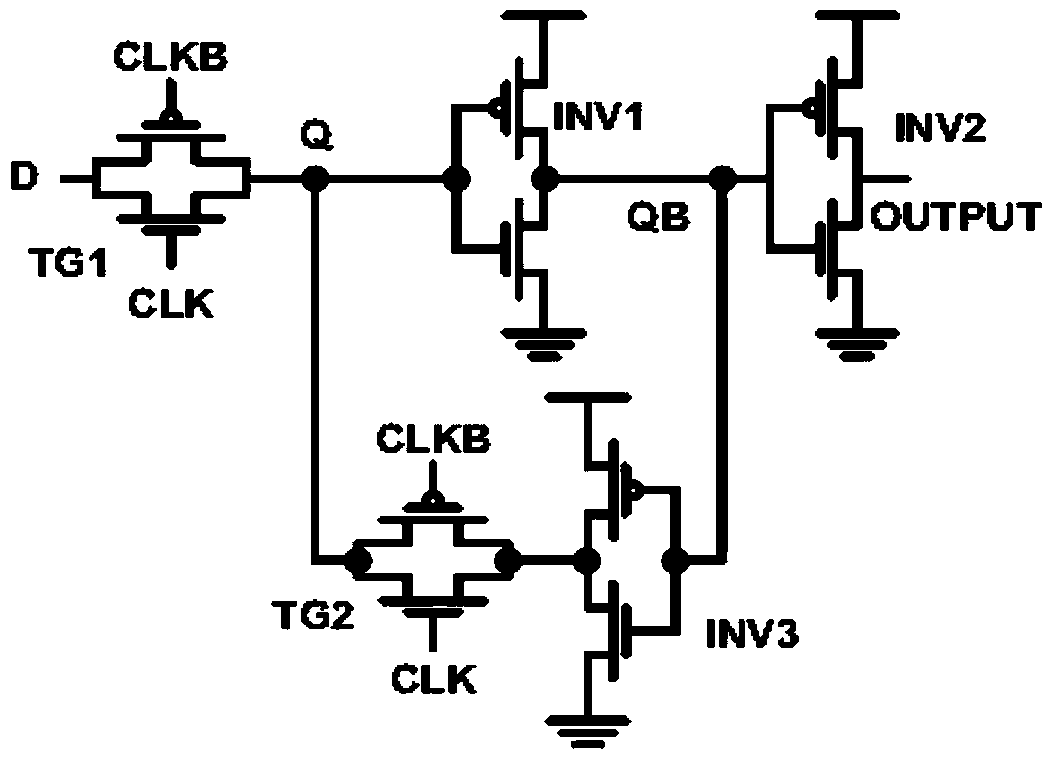

Single event upset resistant synchronously resettable D flip-flop

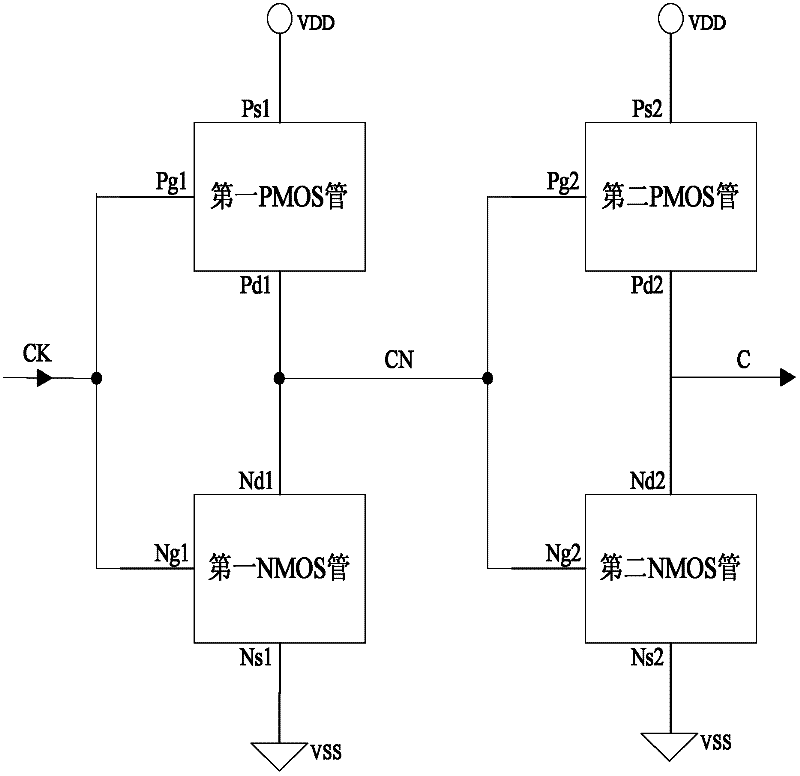

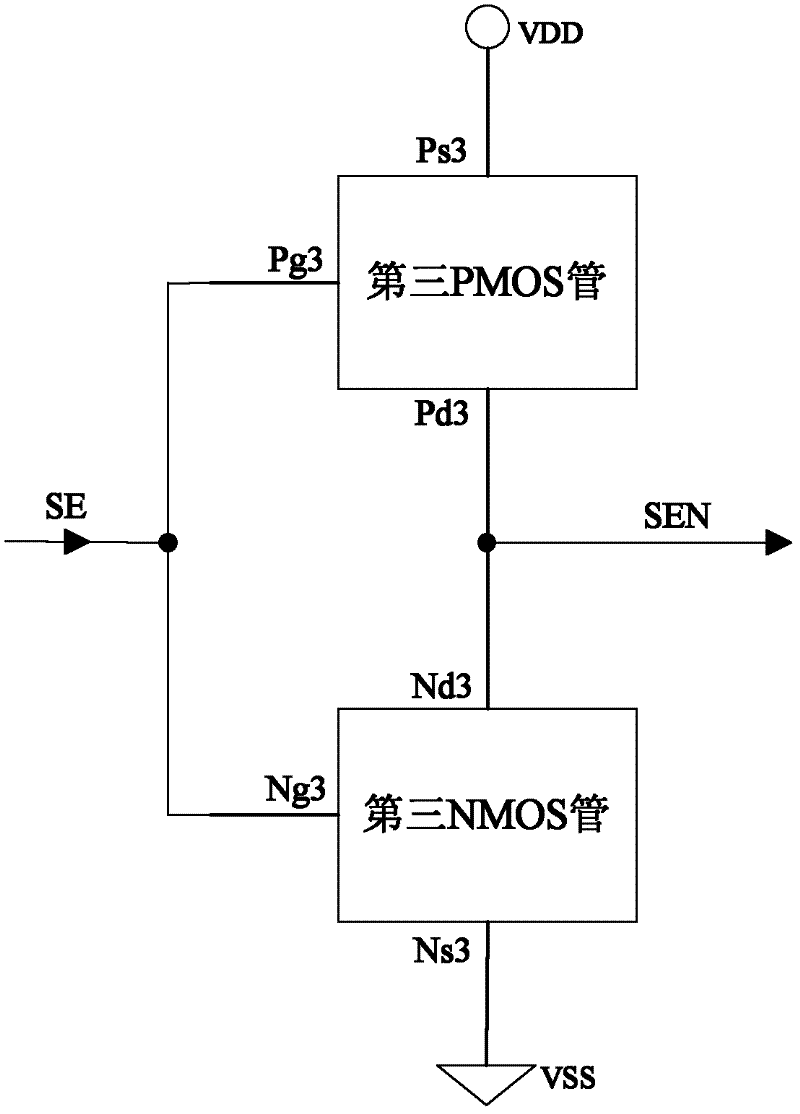

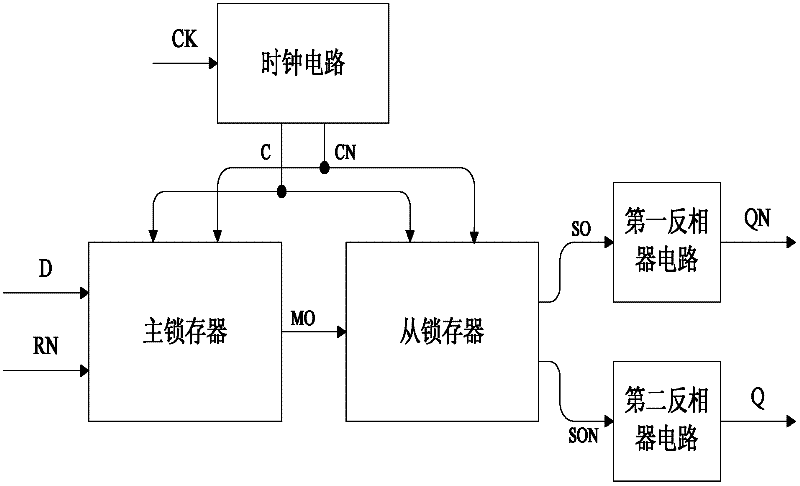

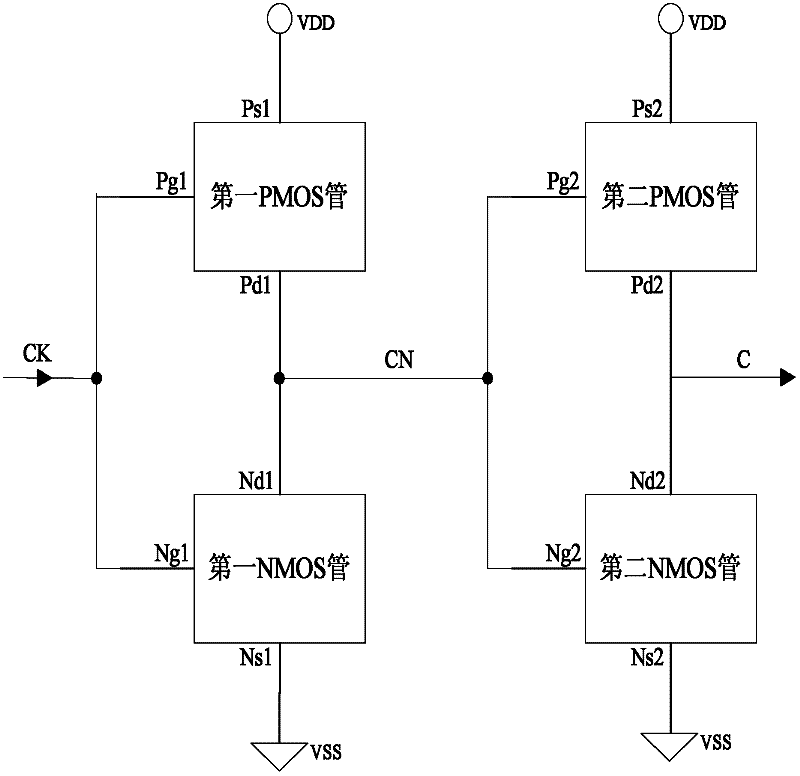

ActiveCN102394598AImproved resistance to single event upsetExcellent turning abilityElectric pulse generator circuitsOxide semiconductorStandard cell

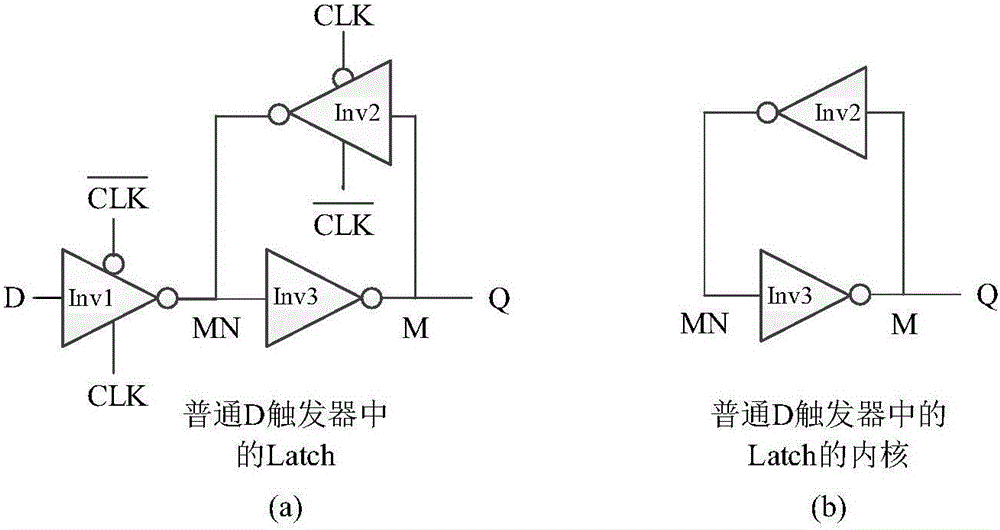

The invention discloses a single event upset resistant synchronously resettable D flip-flop, aiming at improving the single event upset resistance of a resettable D flip-flop. The D flip-flop is composed of a clock circuit, a master latch, a slave latch, a first inverter circuit and a second inverter circuit, wherein the master latch is composed of 12 PMOS (P-channel Metal Oxide Semiconductor) FETs (Field Effect Transistors) and 12 NMOS (N-channel Metal Oxide Semiconductor) FETs, the slave latch is composed of 10 PMOS FETs and 10 NMOS FETs, duplication redundant reinforcement is performed on the master latch and the slave latch, and the C2MOS (Clocked Complementary Metal Oxide Semiconductor) circuit structures of the master latch and the slave latch are improved, i.e. a pull-up circuit and a pull-down circuit in the mutually redundant C2MOS circuits are separated from the master latch, and a pull-up PMOS FET and a pull-down NMOS FET in the mutually redundant C2MOS circuits are separated from the slave latch. The single event upset resistant resettable D flip-flop disclosed by the invention has strong single event upset resistance, is suitable for a standard cell library of a single event upset resistance reinforced integrated circuit, and is applied to the fields of aviation, aerospace and the like.

Owner:NAT UNIV OF DEFENSE TECH

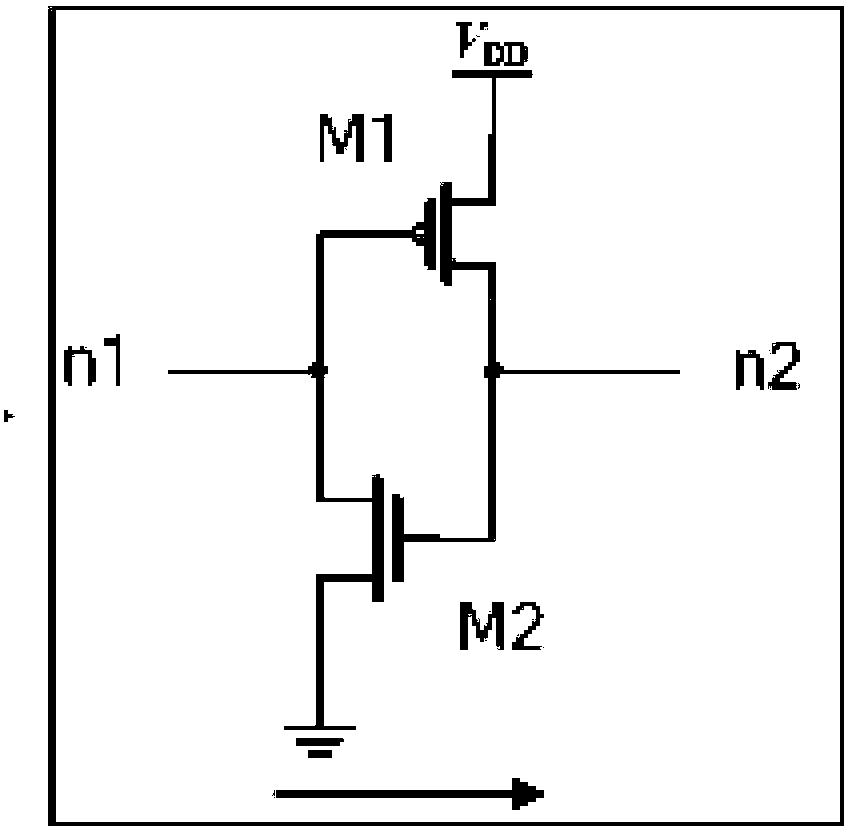

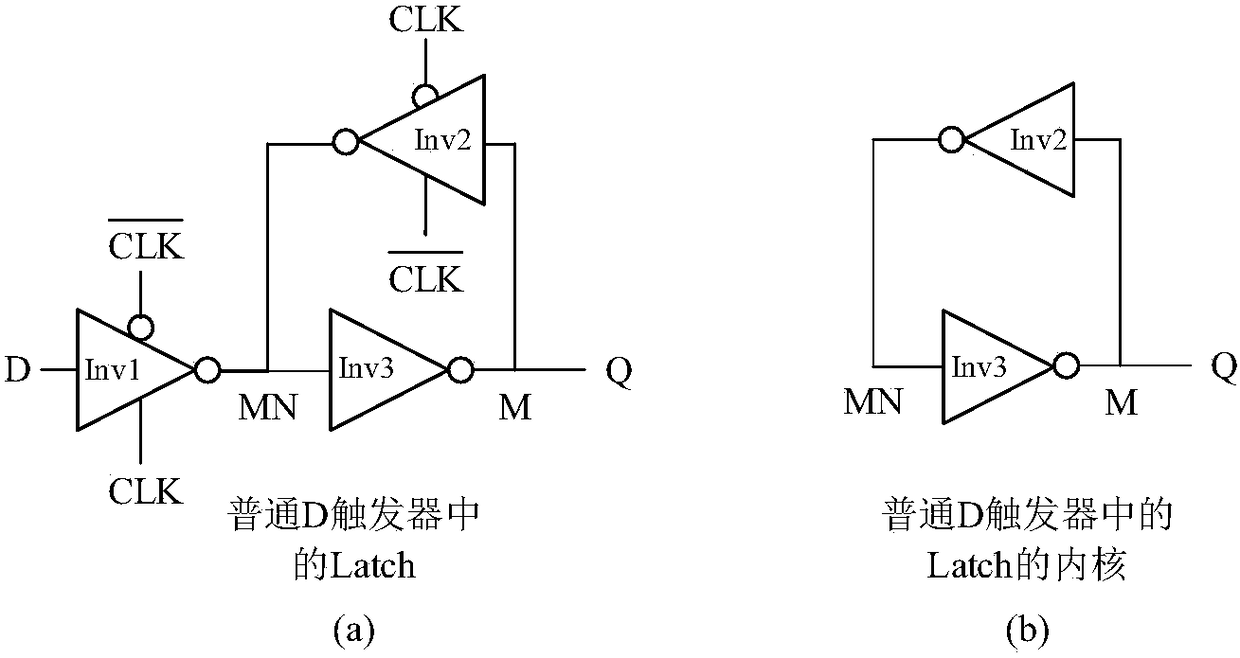

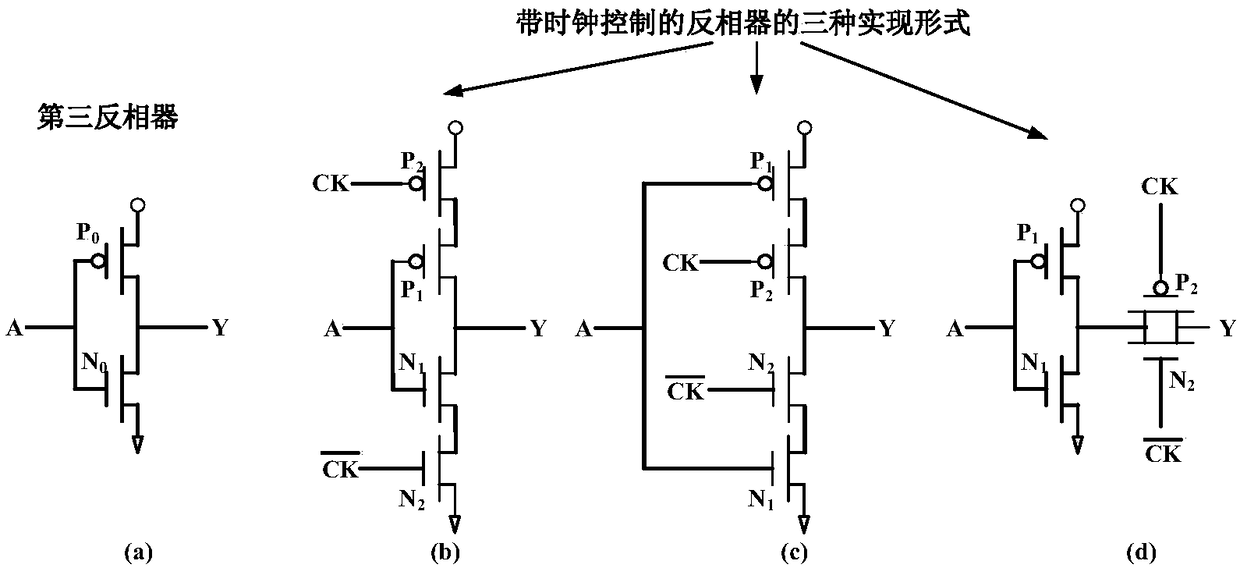

D trigger resistant to single event upset

ActiveCN105897223ASmall area overheadDesensitizationElectric pulse generatorEngineeringSingle event upset

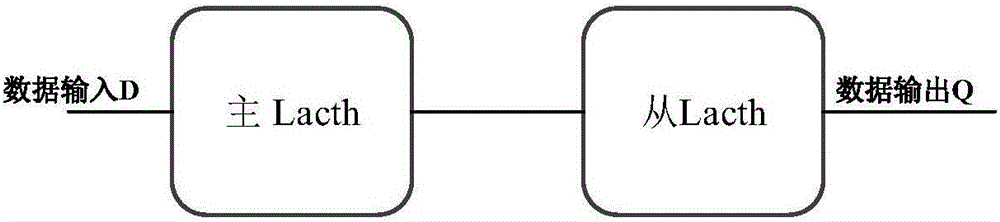

The invention discloses a D trigger resistant to single event upset. The D trigger is formed by master and slave latches connected in series. The master latch and the slave latch have completely same structure. The core of a latch is no longer composed of two end-to-end inverters, but six PMOS transistors P1 to P6 and six NMOS transistors N1 to N6. The master latch or the slave latch of the invention can be formed by adding a clock-controlled transistor to the core of the latch. Compared with triplication redundancy in the prior art, the D trigger not only save the area of an election circuit, but also eliminate single event sensitivity due to the election circuit. Further, the D trigger is lower in single event sensitivity and better in single event upset resistance when storing a numerical value 0. Since many triggers are required to hold the same numerical value for a long time in practical application, the invention is significant to enhance the single event upset resistance of the kind of the triggers.

Owner:NAT UNIV OF DEFENSE TECH

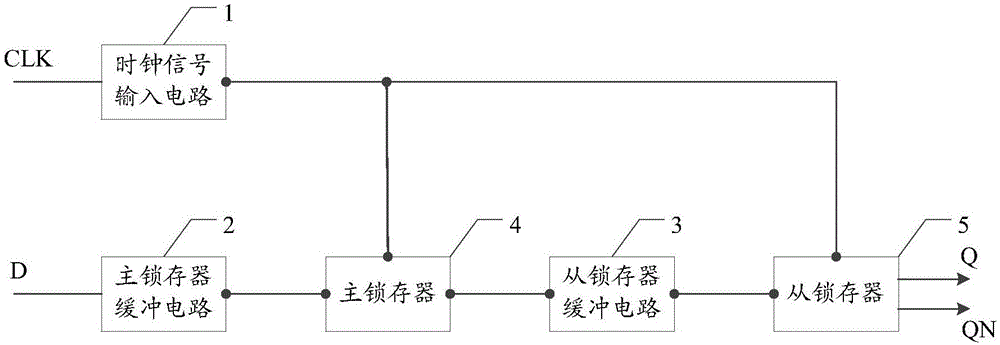

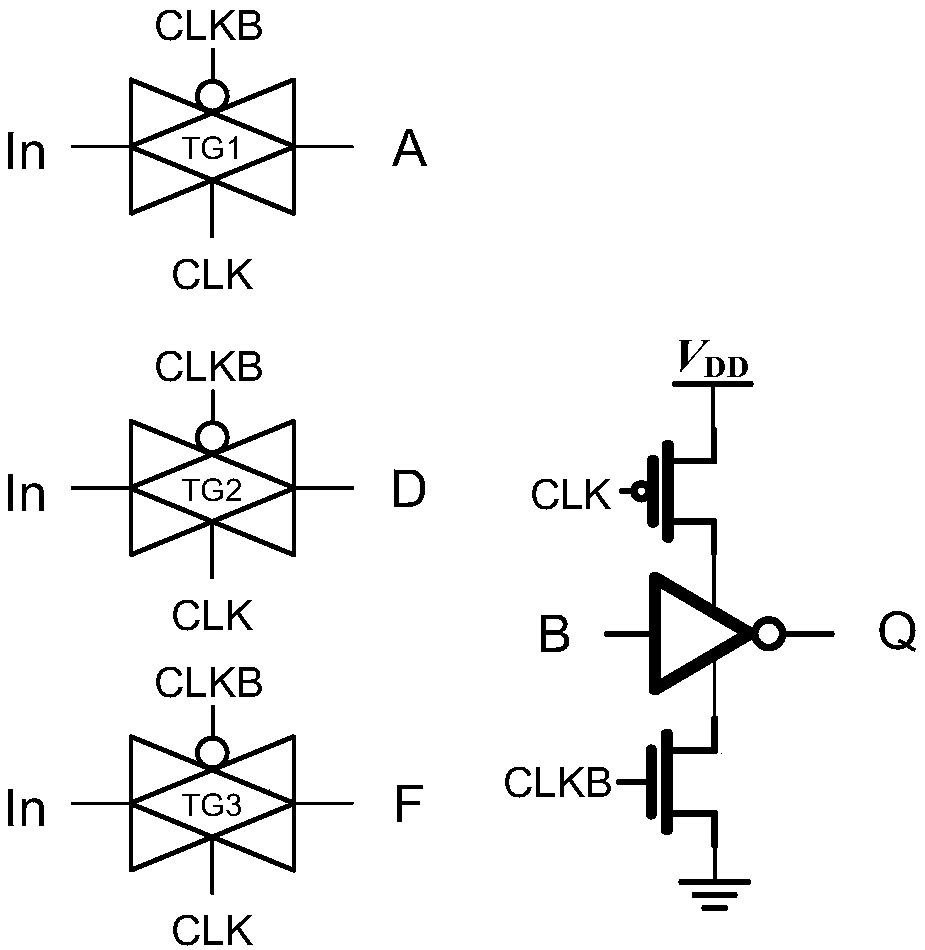

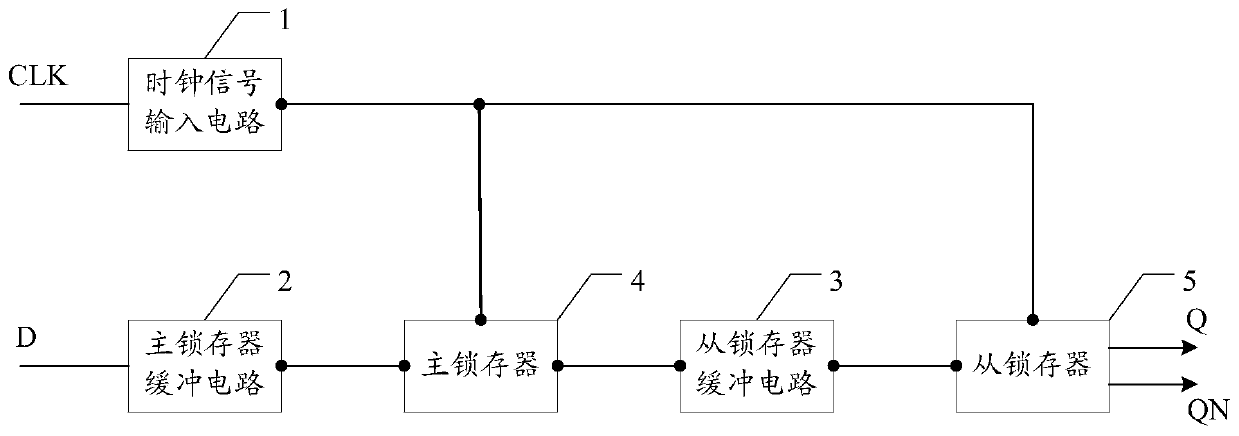

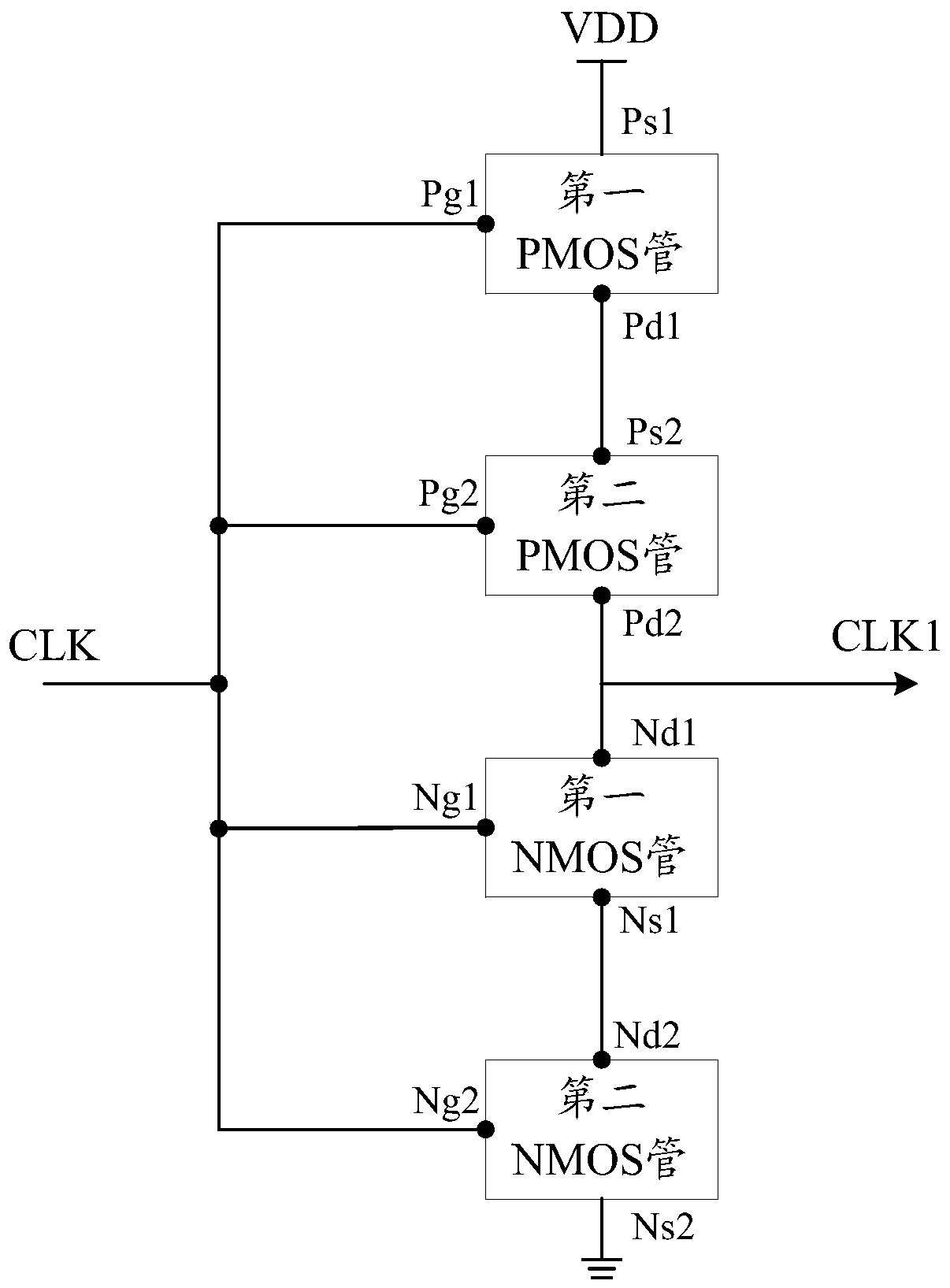

Anti-single-event upset D trigger

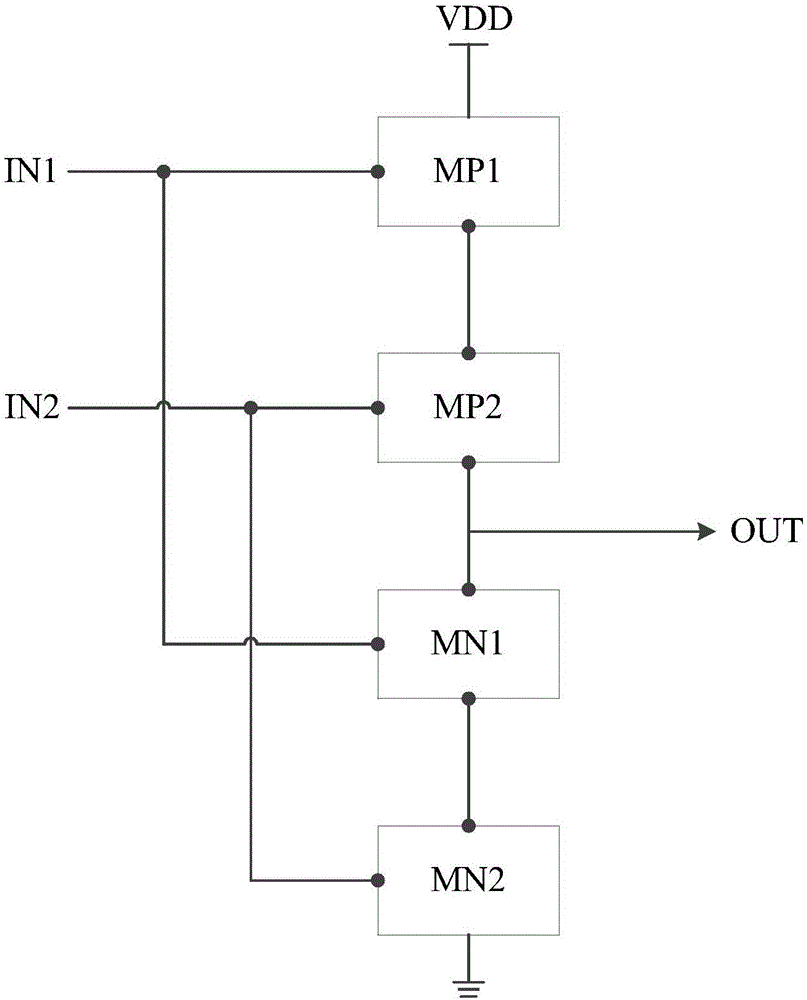

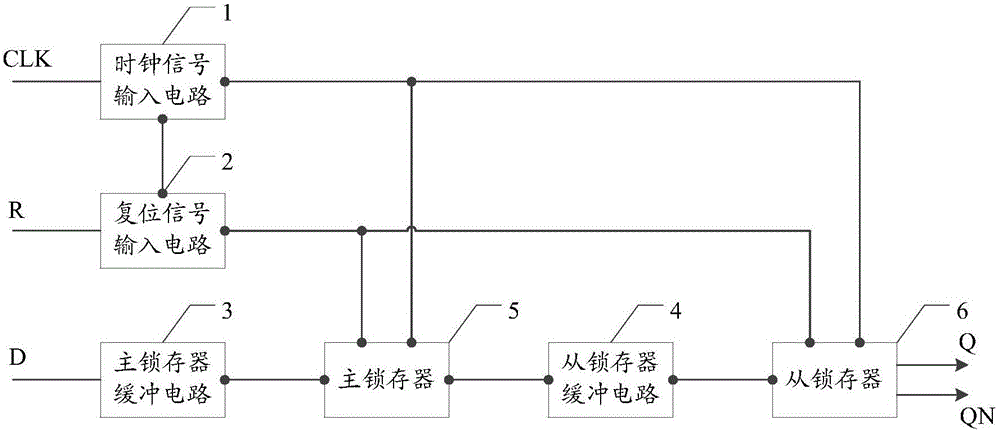

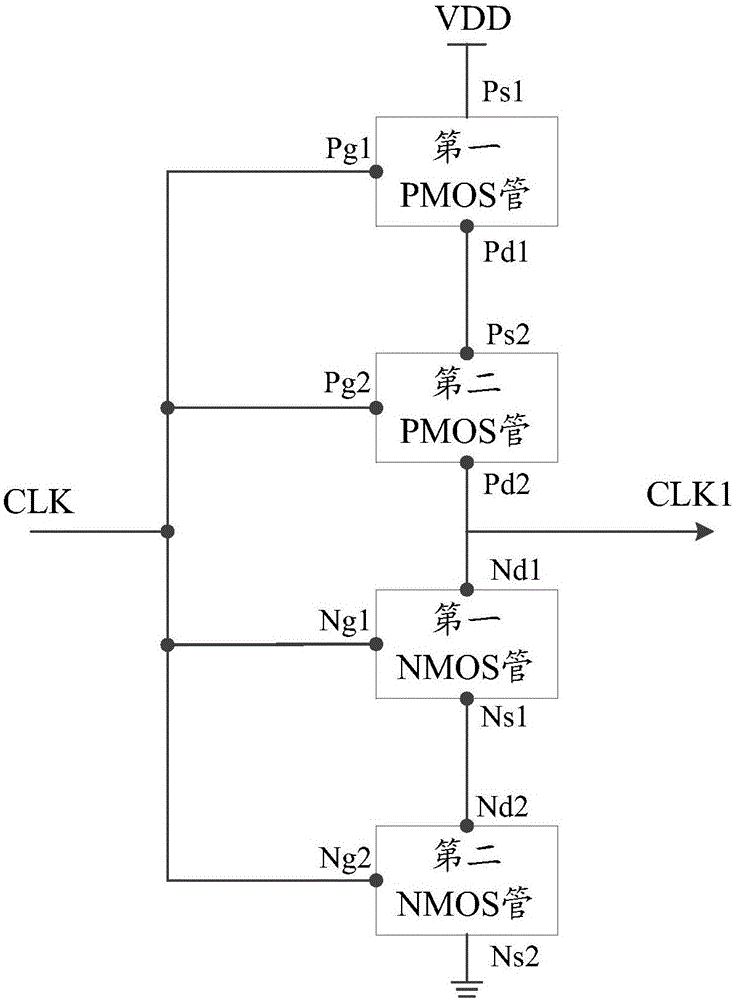

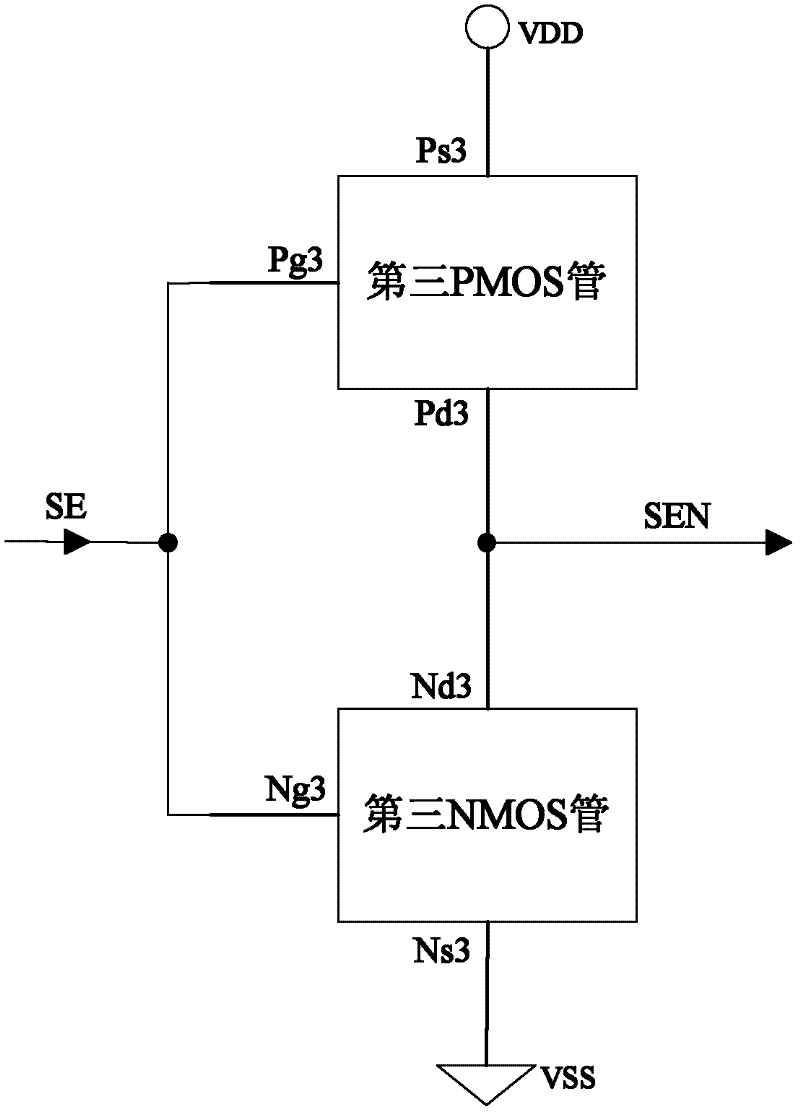

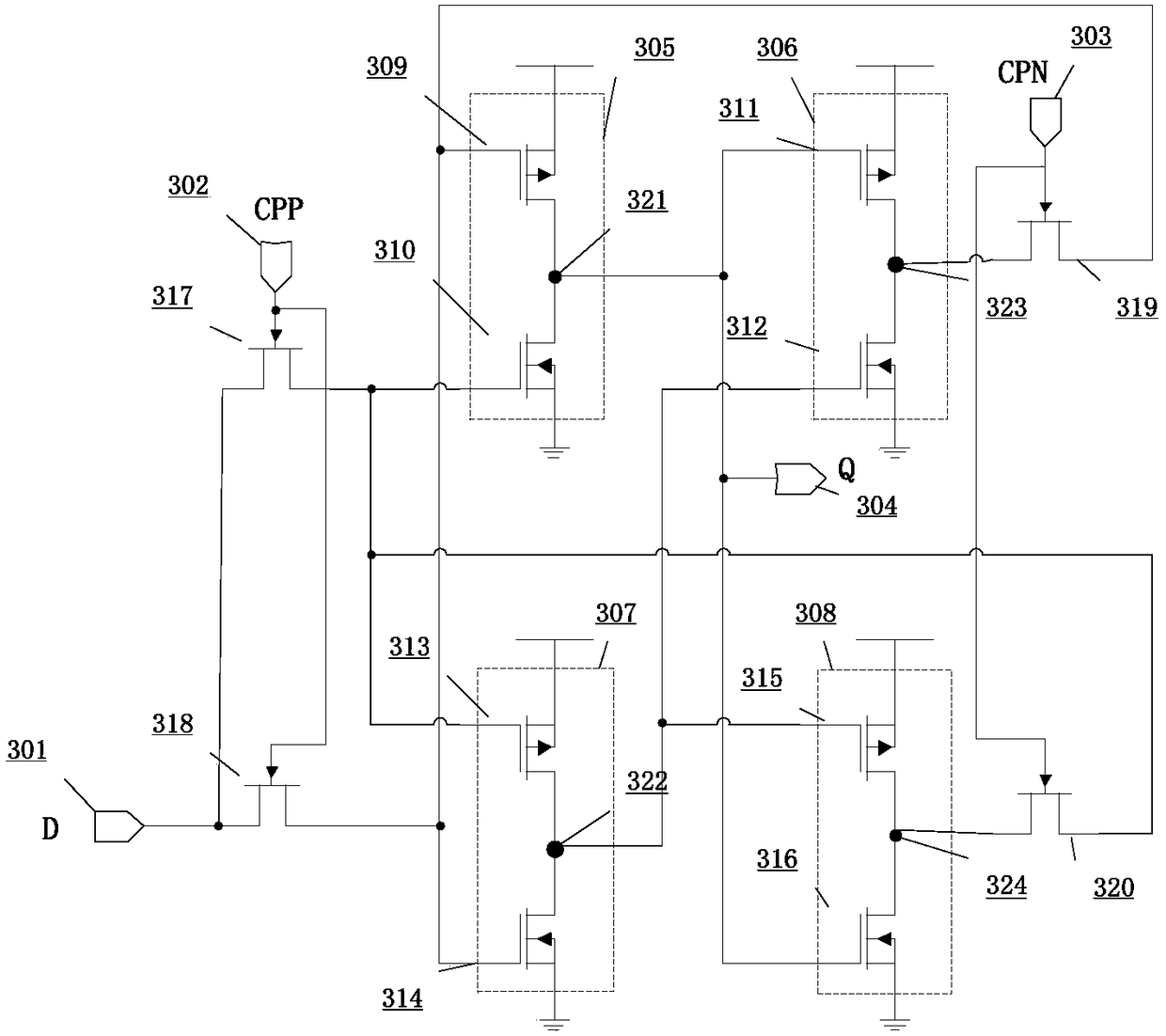

ActiveCN106505976AImproved resistance to single event upsetImprove Flip EffectElectric pulse generatorCMOSTransmission gate

The present invention is applied to the D trigger technology field, and provides an anti-single-event upset D trigger. The D trigger comprises a clock signal input circuit, a main latch buffer circuit, a slave latch buffer circuit, a main latch and a slave latch. The main latch and the slave latch are both dual-mode redundant reinforcing latches. Compared to the prior art, buffer circuits are added at the fronts of the main latch and the slave latch to improve the anti-single-event upset capacity of the D trigger, the main latch and the slave latch are subjected to dual-mode redundant reinforcing to separate into pull-up PMOS tubes and pull-down NMOS tubes, which are mutually redundant, in C2MOS circuits so as to avoid the feedback loop caused by the single-particle transient pulse in the slave latch, the C2MOS circuits in the main latch and the slave latch circuits are improved, and the control of the circuits through clock signals is realized through the CMOS transmission gate so as to further improve the anti-single-event upset capacity of the D trigger.

Owner:SHENZHEN UNIV

D trigger resisting single event upset

ActiveCN102394597AExcellent anti-single event upset abilityImproved resistance to single event upsetReliability increasing modificationsElectric pulse generator circuitsAviationIntegrated circuit layout

The invention discloses a D trigger resisting single event upset, and aims to improve the single event upset resistance of the D trigger. The D trigger comprises a clock circuit, a main latch, a slave latch, a first phase inverter circuit and a second phase inverter circuit. the main latch comprises 10 PMOS (P-channel Metal Oxide Semiconductor) tubes and 10 NMOS (N-Mental-Oxide-Semiconductor) tubes; the slave latch comprises 10 PMOS tubes and 10 NMOS tubes; both the main latch and the slave latch adopt bimodule redundant reinforcement; and in the main latch and the slave latch, C2MOS circuits are also improved, that is, pull-up PMOS tubes and pull-down NMOS tubes in redundant relation in each C2MOS circuit are separated. The D trigger has strong single event upset resistance, is suitable for standard cell library for a reinforced integrated circuit resisting single event upset, and is used in the fields of aviation, aerospace, and the like.

Owner:NAT UNIV OF DEFENSE TECH

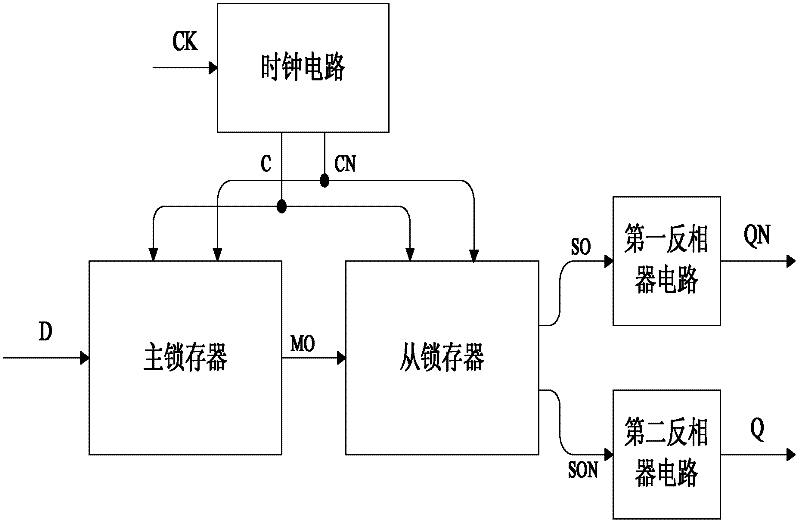

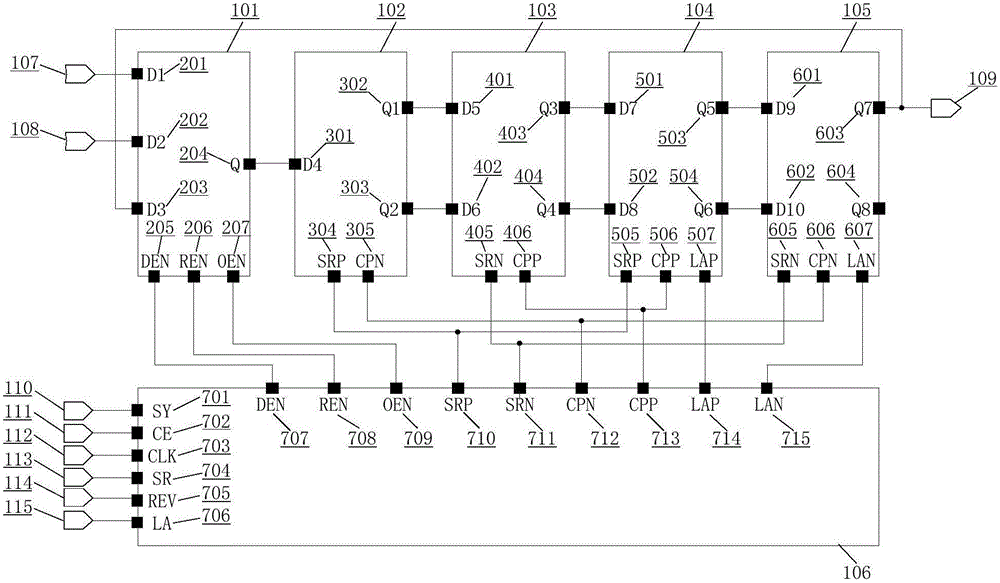

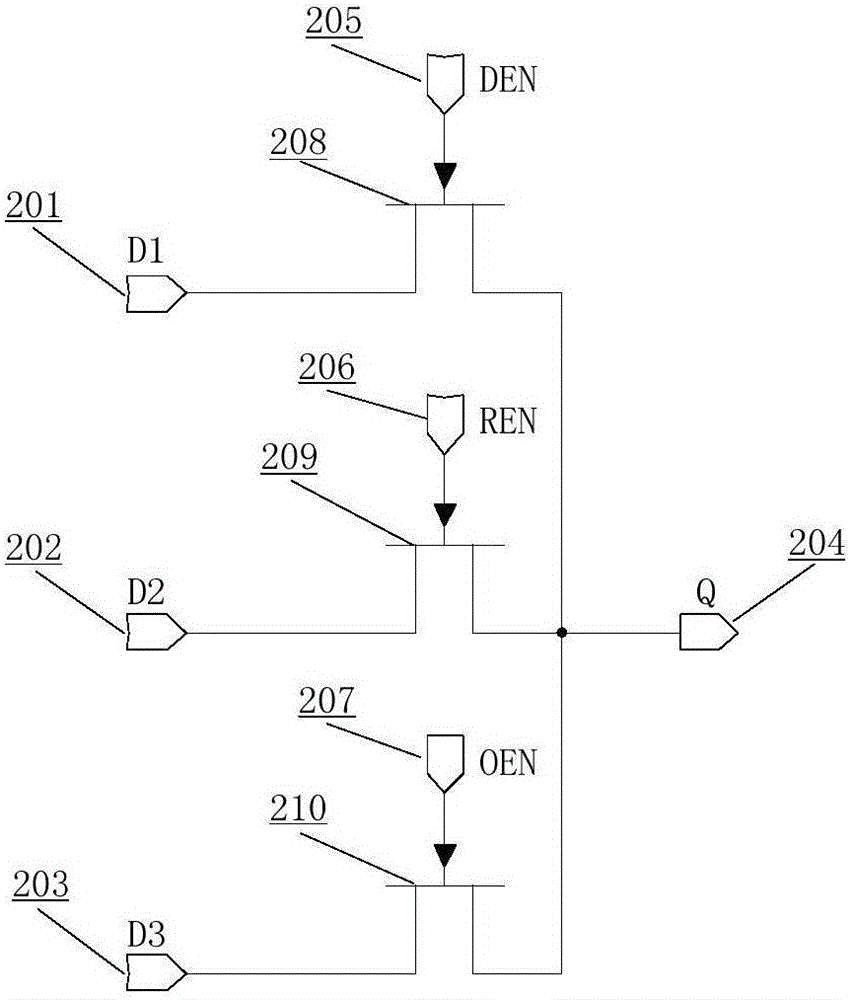

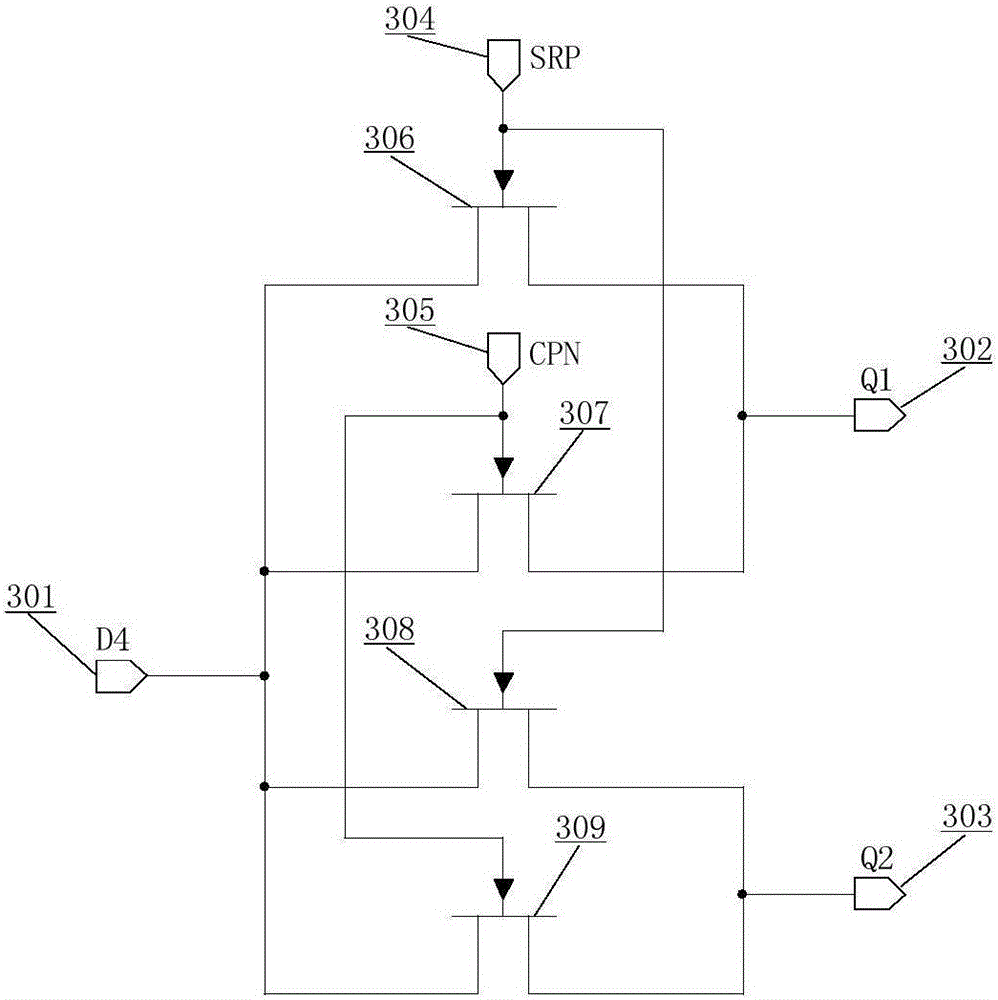

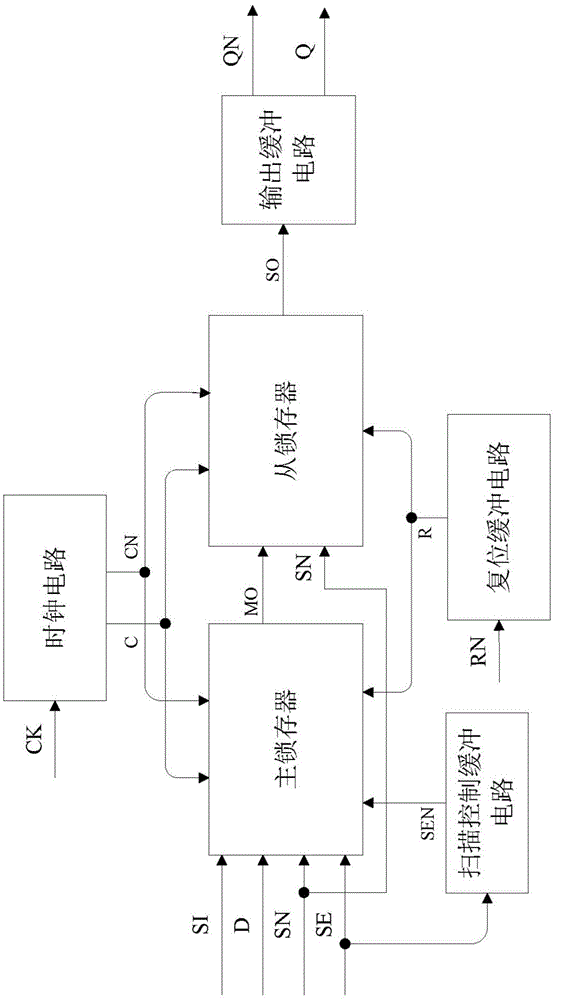

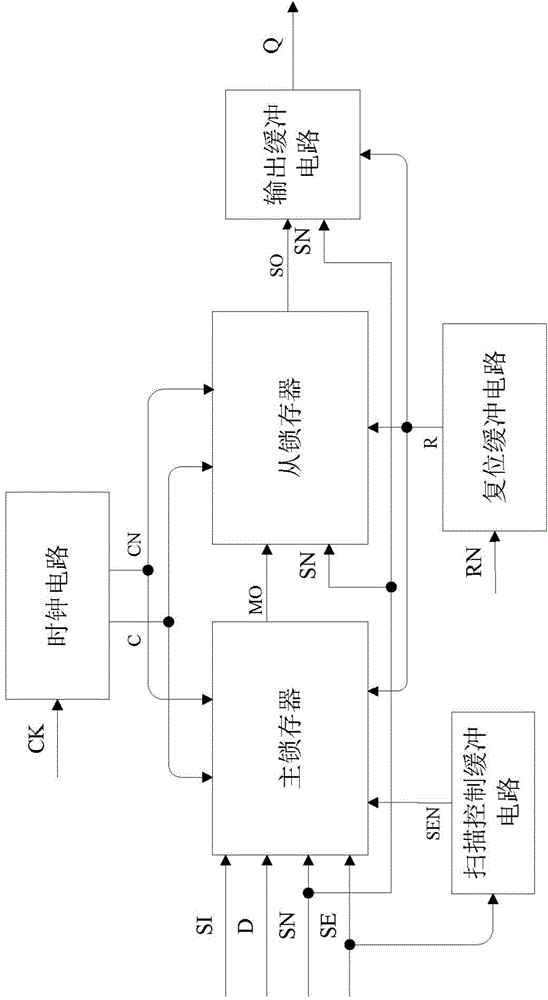

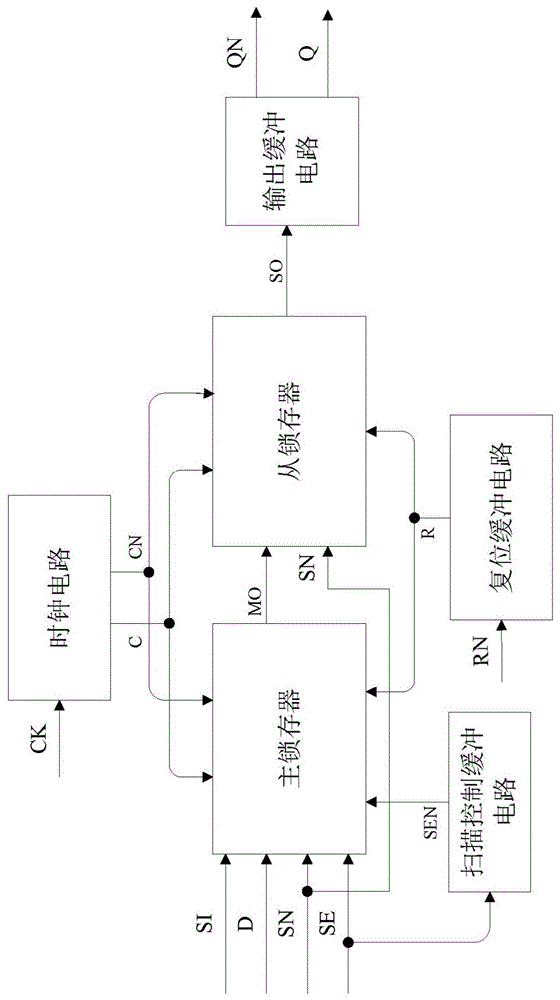

Single event upset resistant settable and resettable scan structure D flip-flop

ActiveCN102394599AExcellent anti-single event upset abilityImproved resistance to single event upsetReliability increasing modificationsElectric pulse generator circuitsAviationField-effect transistor

The invention discloses a single event upset resistant settable and resettable scan structure D flip-flop, aiming at improving the single event upset resistance of the single event upset resistant settable and resettable scan structure D flip-flop. The scan structure D flip-flop is composed of a clock circuit, a scanning control buffer circuit, a resetting buffer circuit, a master latch, a slave latch and an output buffer circuit, wherein the master latch is composed of 20 PMOS (P-channel Metal Oxide Semiconductor) FETs (Field Effect Transistors) and 20 NMOS (N-channel Metal Oxide Semiconductor) FETs, the slave latch is composed of 10 PMOS FETs and 10 NMOS FETs, duplication redundant reinforcement is performed on both the master latch and the slave latch, and the C2MOS (Clocked Complementary Metal Oxide Semiconductor) circuit structures in the master latch and the slave latch are improved, i.e. a pull-up circuit and a pull-down circuit in the mutually redundant C2MOS circuits are separated. The scan structure D flip-flop disclosed by the invention has strong single event upset resistance, is suitable for a standard cell library of a single event upset resistance reinforced integrated circuit, and is applied to the fields of aviation, aerospace and the like.

Owner:NAT UNIV OF DEFENSE TECH

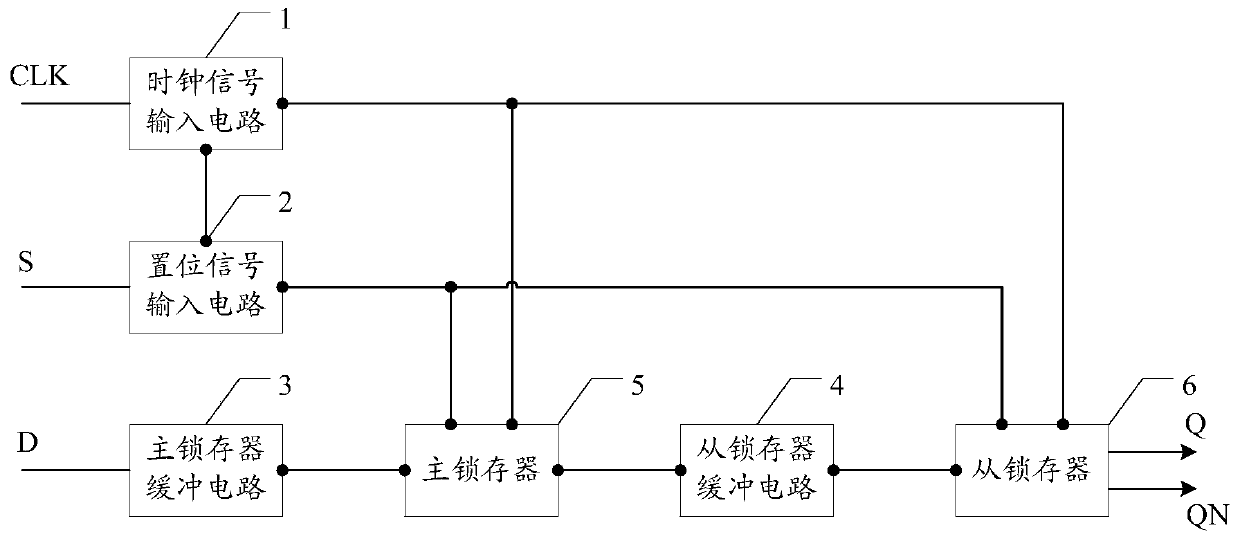

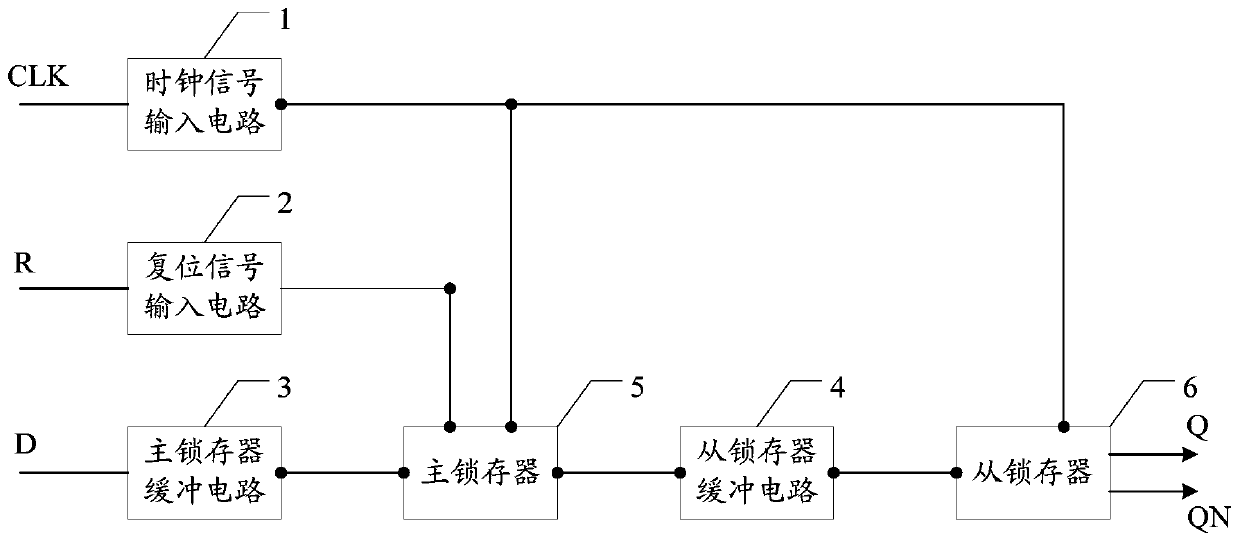

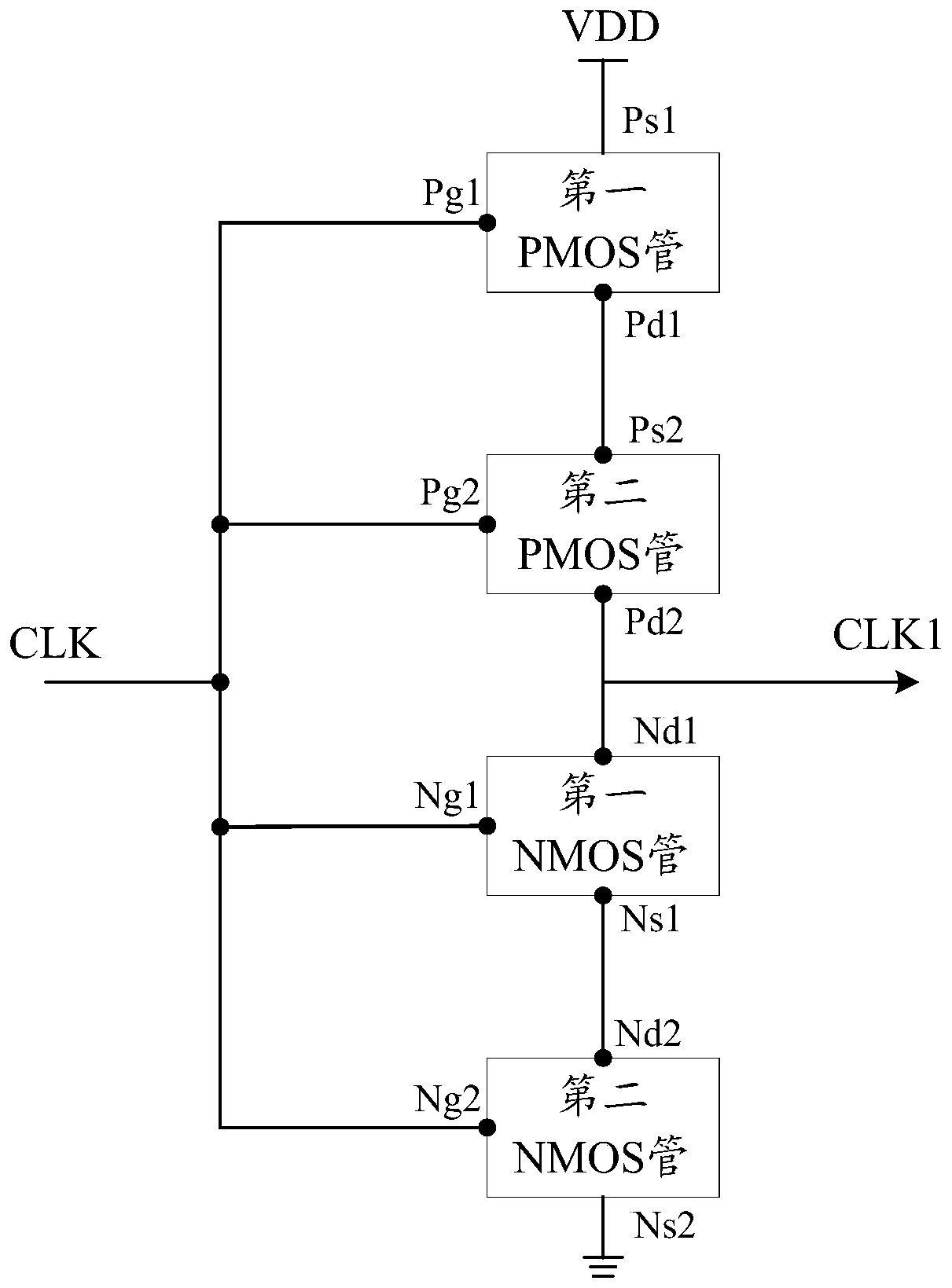

Synchronous reset D trigger for preventing single event upset

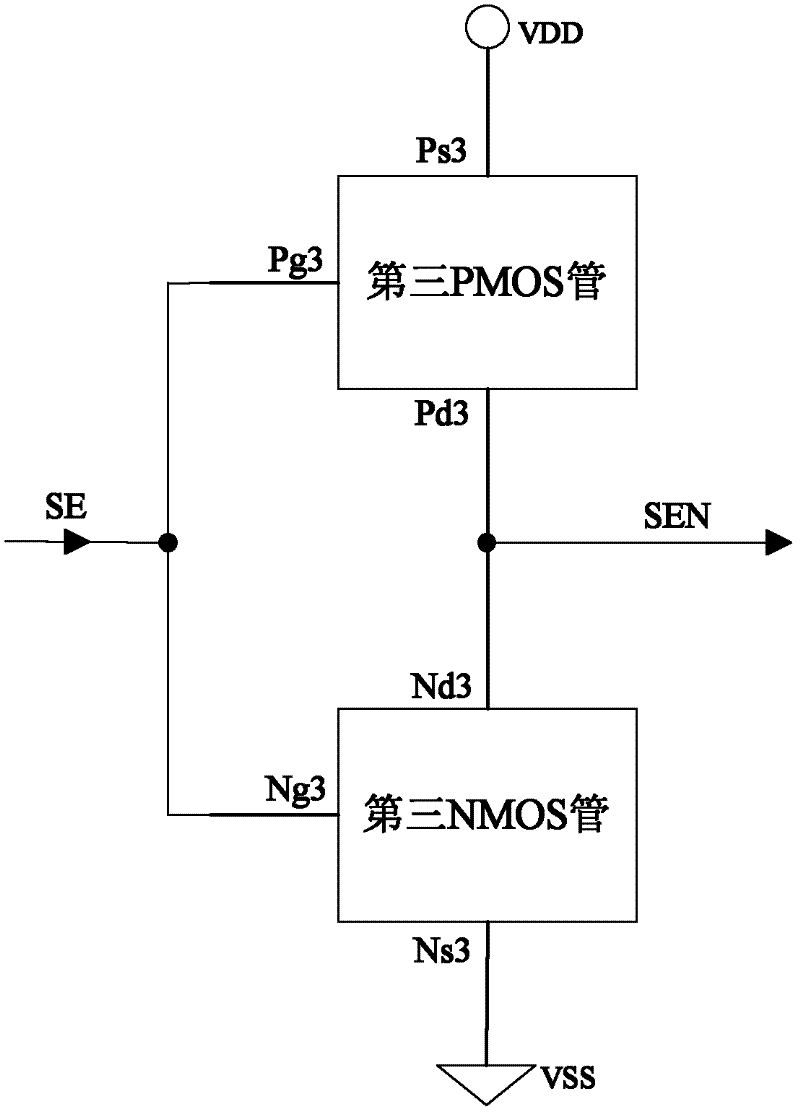

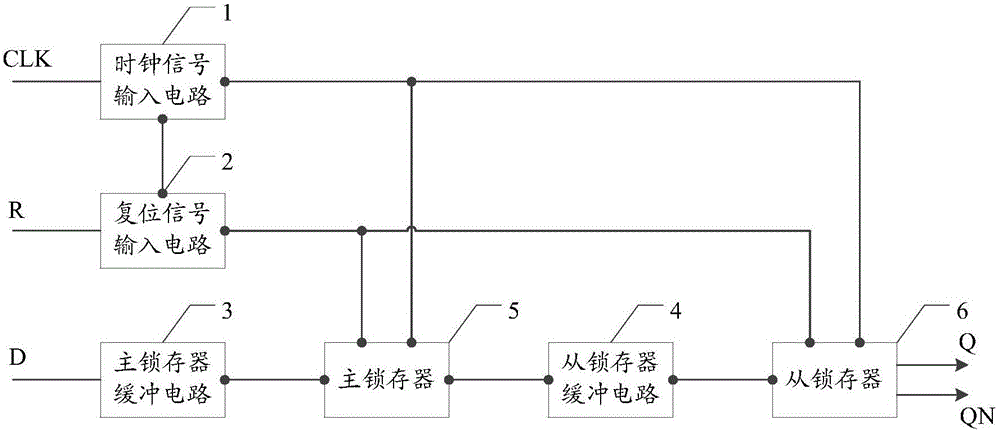

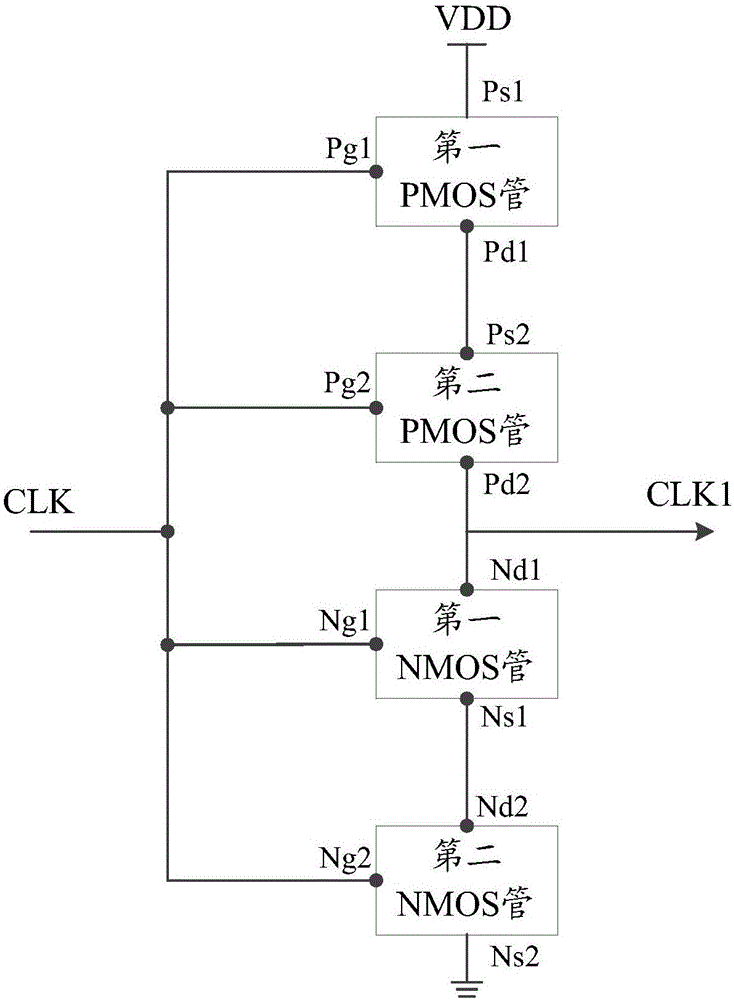

ActiveCN106712743AImproved resistance to single event upsetAvoid feedback loopsElectric pulse generatorDual modeFeedback circuits

The invention is suitable for the technical field of D triggers, and provides a synchronous reset D trigger for preventing single event upset. The D trigger comprises: a clock signal input circuit, a reset signal input circuit, a master latch buffer circuit, a slave latch buffer circuit, a master latch and a slave latch, and both of the master latch and slave latch are dual mode redundancy reinforcement latches. Compared with the prior art, in the synchronous reset D trigger provided by the invention, the buffer circuits are added in front of the master latch and slave latch, so the single event upset ability of the synchronous reset D trigger is improved, dual mode redundancy reinforcement is carried out on the master latch and slave latch, namely the master latch and slave latch are separated to a pull up PMOS tube and a pull down PMOS tube in a C2MOS circuit, which are redundant to each other, therefore a possible feedback circuit caused by single event transient pulses is avoided, the C2MOS circuits in the circuits of the master latch and slave latch are improved, clock signals control the circuits through SMOS transmission rates, and the single event upset ability of the synchronous reset D trigger is further improved.

Owner:SHENZHEN UNIV

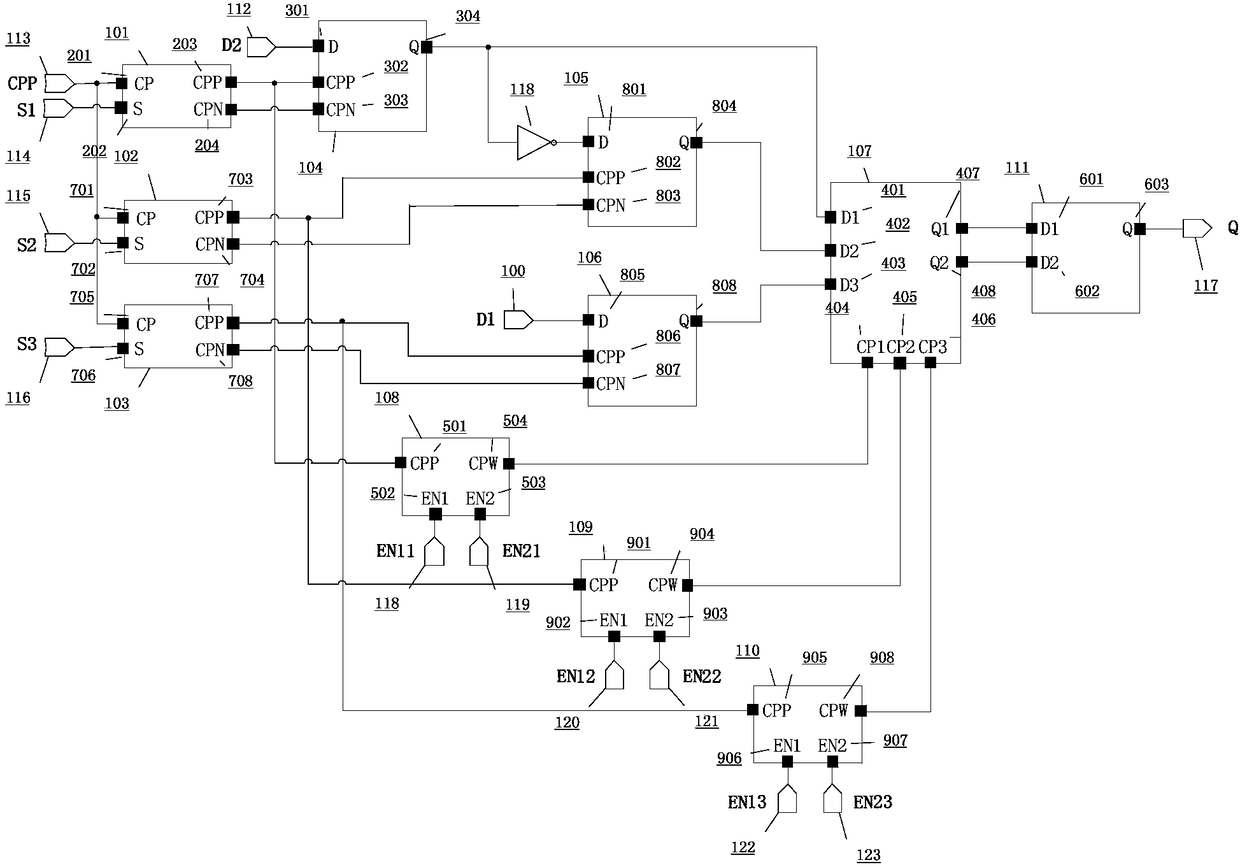

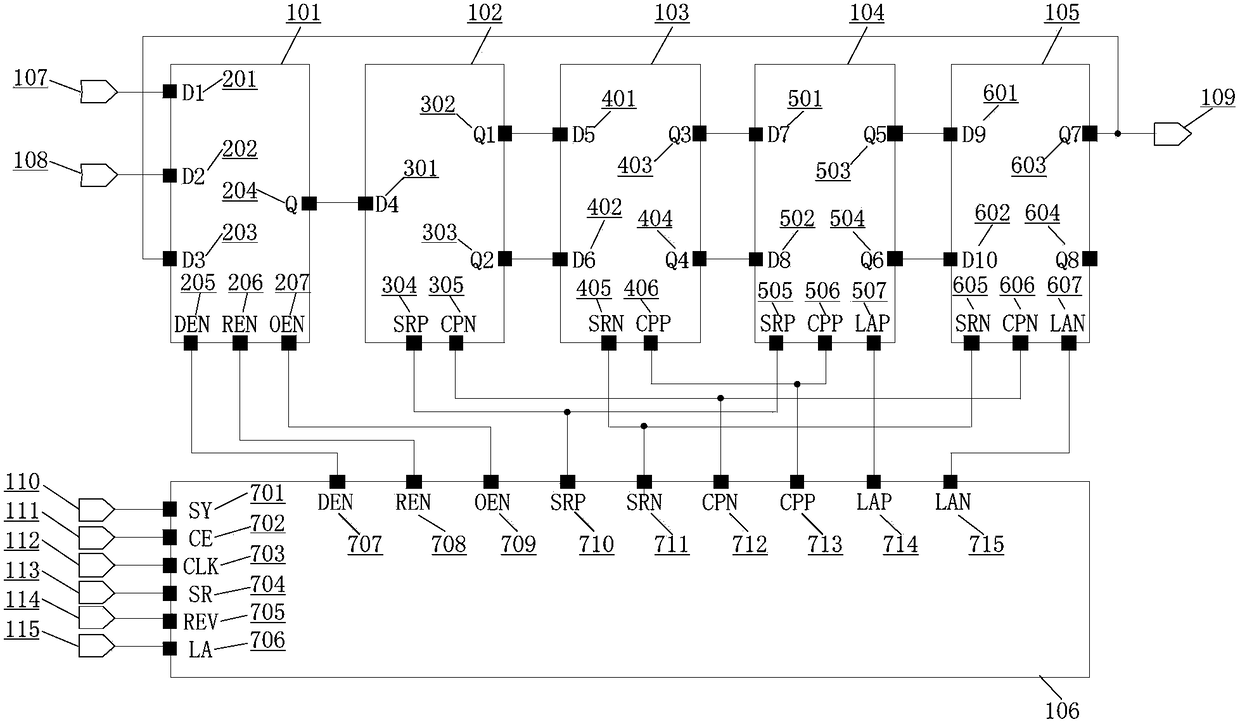

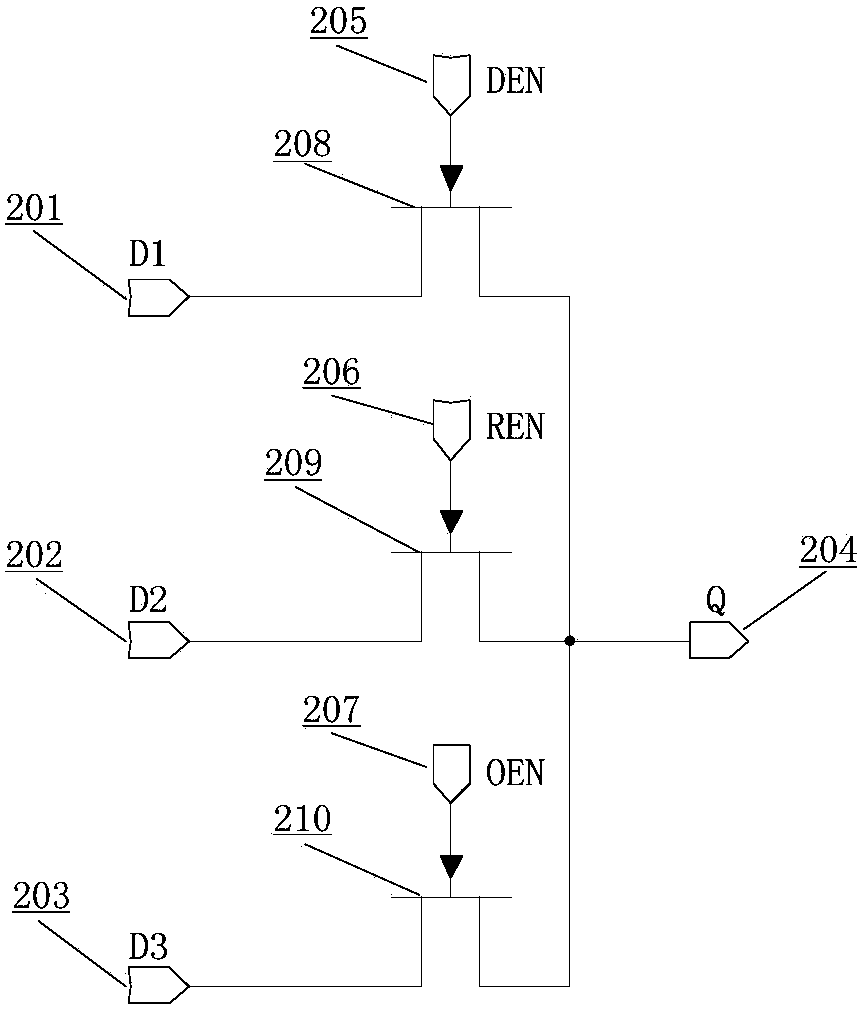

Single-particle reinforced programmable user register circuit

ActiveCN105790755AImprove Flip EffectImproved resistance to single event upsetLogic circuits using elementary logic circuit componentsControl powerProcessor register

The invention relates to a single-particle reinforced programmable user register circuit. Single-particle reinforcement design of a user register is realized by adopting a circuit having a dual-redundant interlocking structure in the traditional latch; on the basis, a multi-mode programmable control switch is additionally provided, such that the user register can be switched among multiple working modes; a multi-power and multi-mode controller circuit is adopted; a user logic power supply is used in a data path; and a multi-mode switching control power supply is used on a programmable switch, such that time sequence influence generated by the single-particle reinforcement design of the dual-redundant interlocking structure and the programmable switch can be completely eliminated. Compared with the traditional register, the single-particle reinforcement index in the invention is increased by three orders of magnitude; furthermore, programmable functions, such as an edge trigger, a level latch, synchronous / asynchronous setting / resetting and data retention, can be realized; and thus, users have relatively high flexibility, better time sequence performance and ultra-high single-particle reinforcement resistant index while using the programmable user register.

Owner:BEIJING MXTRONICS CORP +1

Anti-single event upset and anti-single event transient settable reset scanning structure D trigger

ActiveCN103825586AExcellent anti-single event upset abilityImproved resistance to single event upsetElectric pulse generatorDual modeSingle event upset

The invention discloses an anti-single event upset and anti-single event transient settable reset scanning structure D trigger, for the purpose of solving the problems of not high anti-single event upset capability and not high anti-single event transient capability. The settable reset scanning structure D trigger provided by the invention is composed of a buffer circuit, a scanning control buffer circuit, a setting buffer circuit, a reset buffer circuit, a clock circuit, a master latch register, a slave latch register and an output buffer circuit. The master latch register and the slave latch register are latch registers with redundancy reinforcement. The master latch register and the slave latch register are connected in series and are both connected with the clock circuit, the setting buffer circuit and the rest buffer circuit. The master latch register is also connected with the buffer circuit and the scanning control buffer circuit. The slave latch register is also connected with the output buffer circuit. According to the invention, mutually redundant C<2>MOS circuits are separated from the master latch register and the slave latch register so that the anti-single event upset capability is improved. The buffer circuit enables no errors to be generated under a single event transient pulse which lasts for quite a long time. A dual-mode redundancy pathway further enhances the anti-single event upset capability.

Owner:NAT UNIV OF DEFENSE TECH

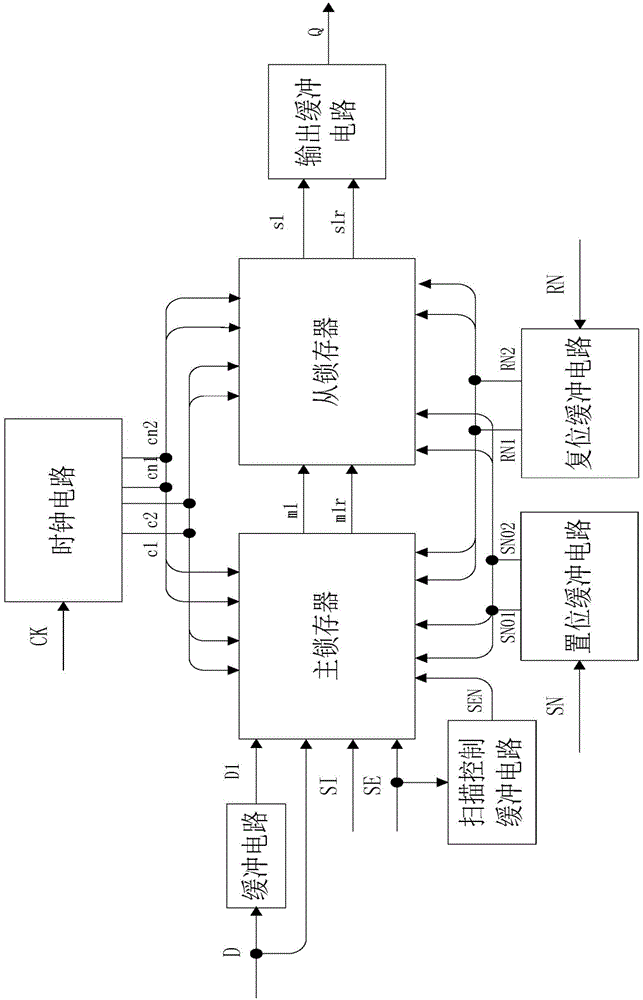

D trigger provided with scanning structure and resisting single event upset

ActiveCN102394601AExcellent anti-single event upset abilityImproved resistance to single event upsetReliability increasing modificationsElectric pulse generator circuitsAviationSingle event upset

The invention discloses a D trigger provided with a scanning structure and resisting single event upset, and aims to improve the single event upset resistance of the D trigger provided with the scanning structure. The D trigger comprises a clock circuit, a scanning control buffer circuit, a main latch, a slave latch, a first phase inverter circuit and a second phase inverter circuit, wherein the main latch comprises 16 PMOS (P-channel Metal Oxide Semiconductor) tubes and 16 NMOS (N-Mental-Oxide-Semiconductor) tubes; the slave latch comprises 10 PMOS tubes and 10 NMOS tubes; both the main latch and the slave latch adopt bimodule redundant reinforcement; and in the main latch and the slave latch, C2MOS circuits are improved, that is, a pull-up circuit and a pull-down circuit in redundant relation in each C2MOS circuit are separated. The D trigger has strong single event upset resistance, is suitable for standard cell library for a reinforced integrated circuit resisting single event upset, and is used in the fields of aviation, aerospace, and the like.

Owner:NAT UNIV OF DEFENSE TECH

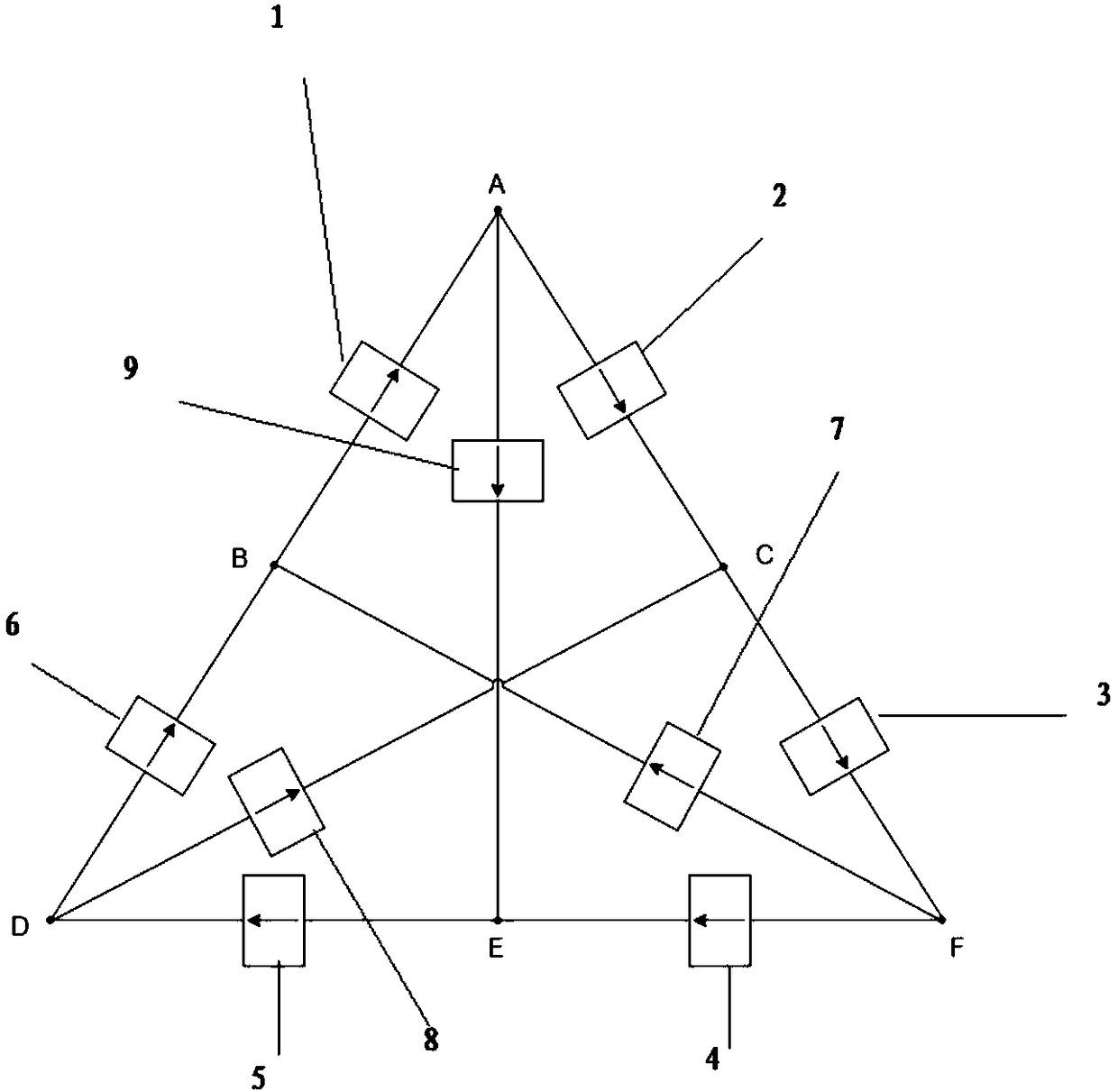

Double-node upset prevention latch

ActiveCN108270429AImproved resistance to single event upsetImprove reliabilityReliability increasing modificationsLogic circuits coupling/interface using field-effect transistorsCouplingSingle event upset

The embodiment of the invention provides a double-node upset prevention latch and relates to the technical field of an integrated circuit. The latch comprises a storage node A, a storage node B, a storage node C, a storage node D, a storage node E and a storage node F. The latch also comprises a first cross coupling structure, a second cross coupling structure, a third cross coupling structure, afourth cross coupling structure, a fifth cross coupling structure, a sixth cross coupling structure, a seventh cross coupling structure, an eighth cross coupling structure and a ninth cross coupling structure. According to the latch, the technical problem that in the prior art, the double-node upset cannot be prevented by the latch in a small area circuit structure is solved. According to the latch provided by the invention, the technical effects that the single event upset prevention capability of the digital integrated circuit in a bad condition is improved, the double-node upset is prevented, the reliability is high and the area cost is low are achieved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

D trigger resisting single event upset

ActiveCN102394597BExcellent anti-single event upset abilityImproved resistance to single event upsetReliability increasing modificationsElectric pulse generator circuitsAviationIntegrated circuit layout

The invention discloses a D trigger resisting single event upset, and aims to improve the single event upset resistance of the D trigger. The D trigger comprises a clock circuit, a main latch, a slave latch, a first phase inverter circuit and a second phase inverter circuit. the main latch comprises 10 PMOS (P-channel Metal Oxide Semiconductor) tubes and 10 NMOS (N-Mental-Oxide-Semiconductor) tubes; the slave latch comprises 10 PMOS tubes and 10 NMOS tubes; both the main latch and the slave latch adopt bimodule redundant reinforcement; and in the main latch and the slave latch, C2MOS circuits are also improved, that is, pull-up PMOS tubes and pull-down NMOS tubes in redundant relation in each C2MOS circuit are separated. The D trigger has strong single event upset resistance, is suitable for standard cell library for a reinforced integrated circuit resisting single event upset, and is used in the fields of aviation, aerospace, and the like.

Owner:NAT UNIV OF DEFENSE TECH

Asynchronous reset D flip-flop with capacity for resisting single event upset

ActiveCN106788341AImproved resistance to single event upsetAvoid feedback loopsElectric pulse generatorCMOSTransmission gate

The invention belongs to the technical field of D flip-flops, and provides an asynchronous reset D flip-flop with the capacity for resisting single event upset. The D flip-flop comprises a clock signal input circuit, a reset signal input circuit, a main latch buffering circuit, an auxiliary latch buffering circuit, a main latch and an auxiliary latch, and the main latch and the auxiliary latch are latches with bimodule redundancy reinforcing. Compared with the prior art, the buffering circuits are additionally arranged before the main latch and the auxiliary latch, the capacity for resisting single event upset of the asynchronous reset D flip-flop is improved, bimodule redundancy reinforcing is carried out on the main latch and the auxiliary latch, namely the main latch and the auxiliary latch are separated into a pull-up PMOS tube and a pull-down NMOS tube redundant to each other in the C2MOS circuits, a feedback loop possibly caused by single particle transient pulse in the auxiliary latch is avoided, the C2MOS circuits in the main latch and the auxiliary latch are improved, control over the circuits by clock signals is achieved through a CMOS transmission gate, and the capacity for resisting single event upset of the asynchronous reset D flip-flop is improved further.

Owner:SHENZHEN UNIV

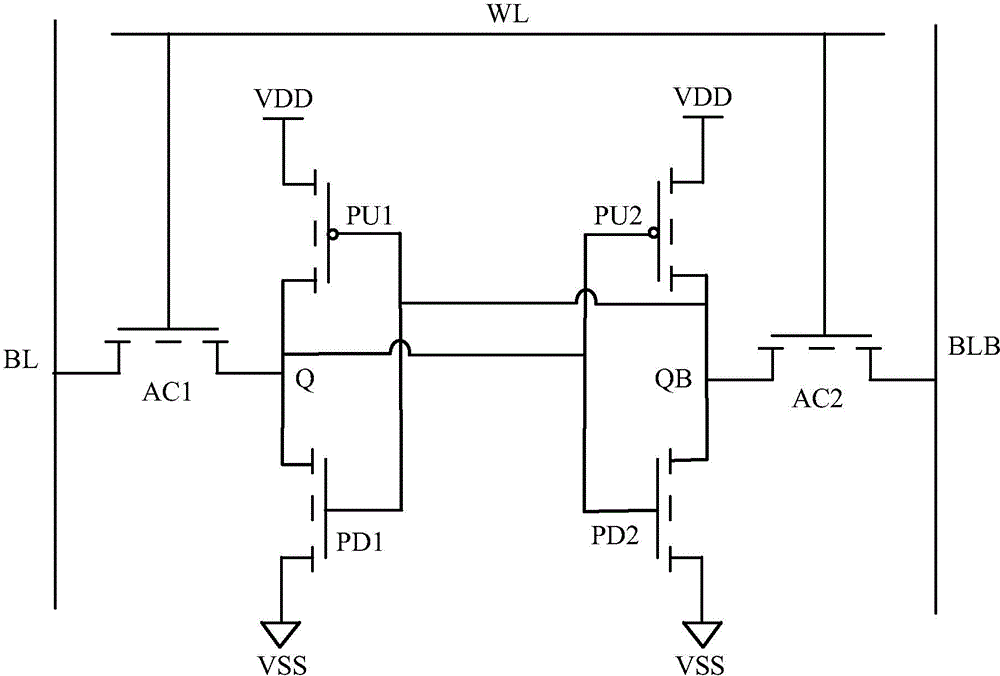

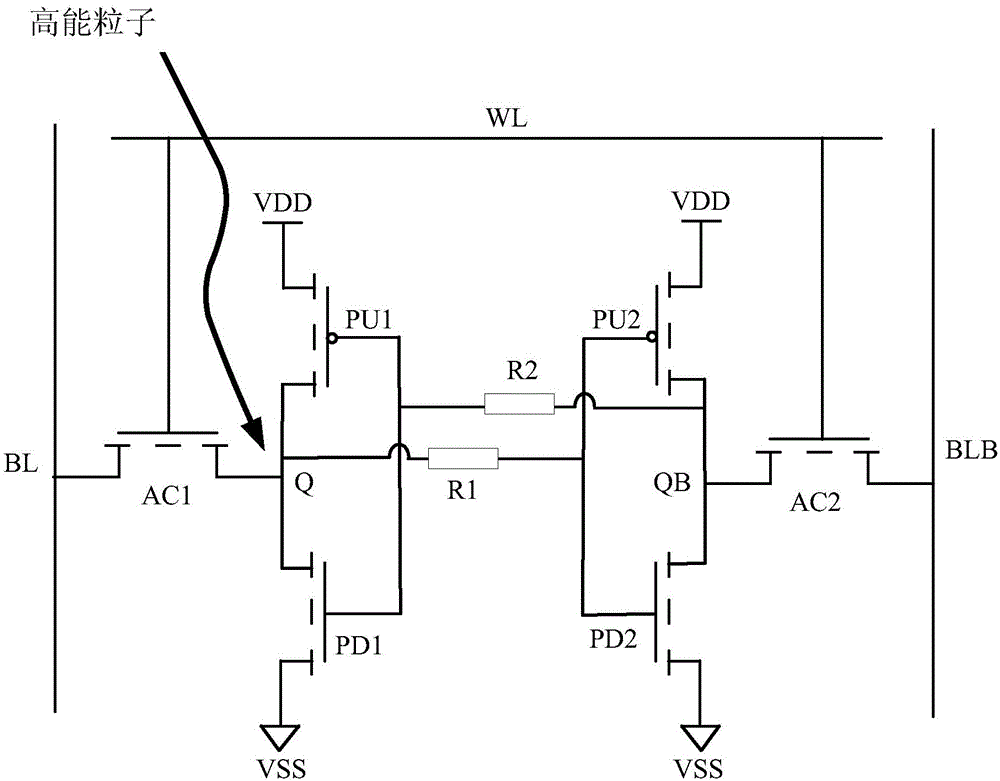

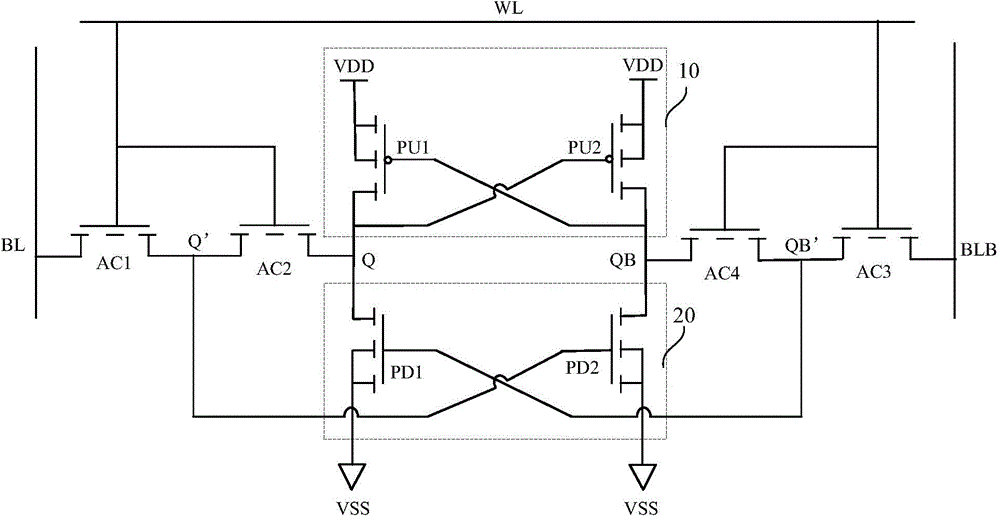

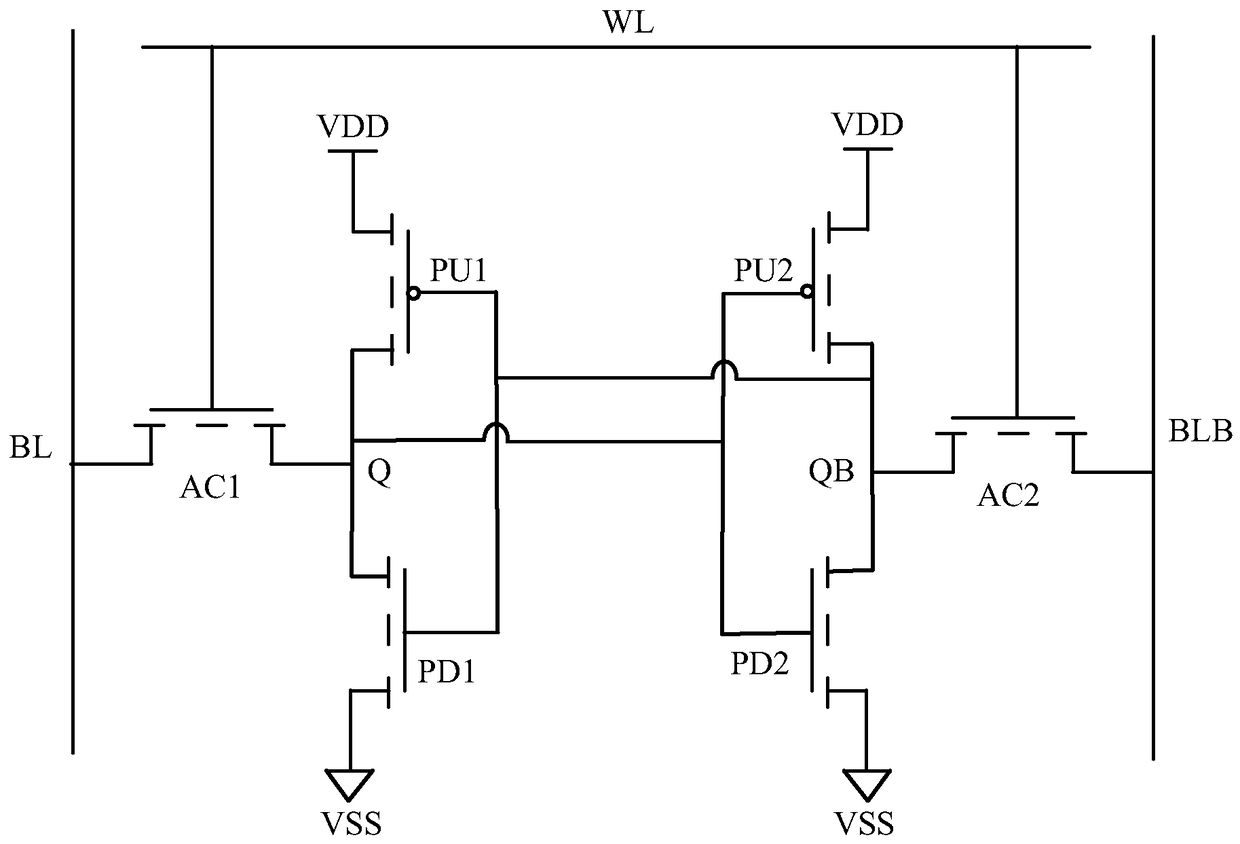

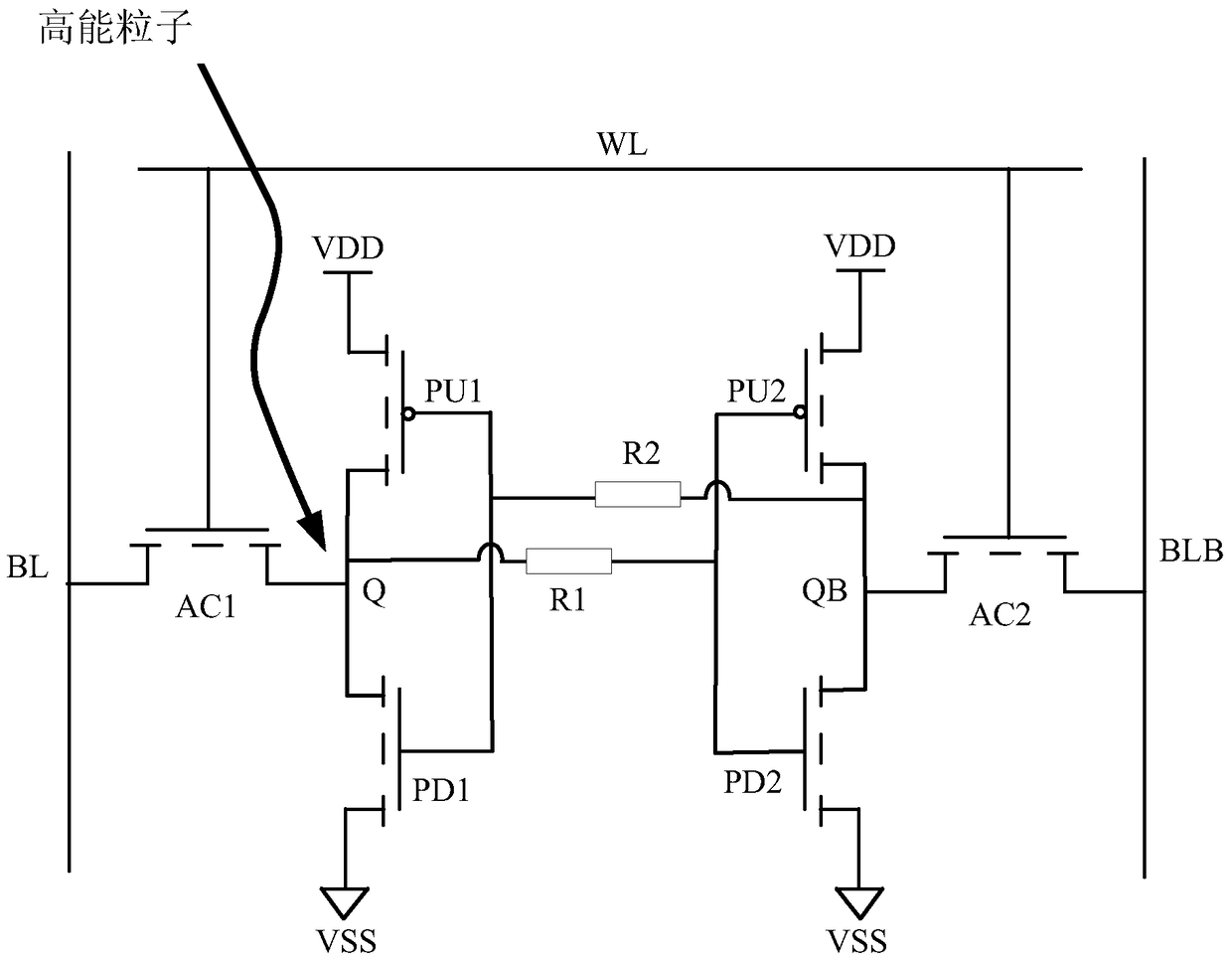

Static random memory unit having anti-single event effect

ActiveCN105321553AExtended feedback timeImproved resistance to single event upsetDigital storageSingle effectEngineering

The invention provides a static random memory unit having an anti-single event effect. The memory unit at least comprises: a first cross-coupling phase inverter being composed of a first pull-up transistor and a second pull-up transistor; a second cross-coupling phase inverter being composed of a first pull-down transistor and a second pull-down transistor; and a pass transistor which is composed of a first access transistor, a second access transistor, a third access transistor and a fourth access transistor. The static random memory unit can effectively prolong the feedback time required of turning the memory unit, so that the anti-single event upset capability of the memory unit can be improved in the situation that recovery time is not changed. The processes of the static random memory unit are completely compatible with digital logic process. The static random memory unit is less in parasitic capacitance, is low in power consumption, has a natural anti-single event latch-up capability and is free of increase of extra process cost.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

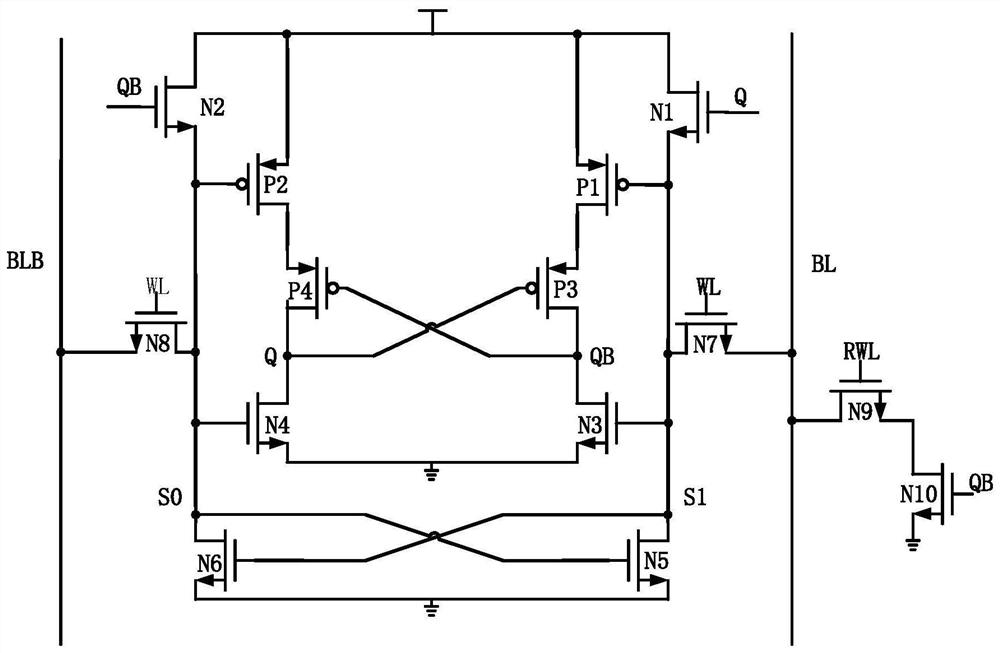

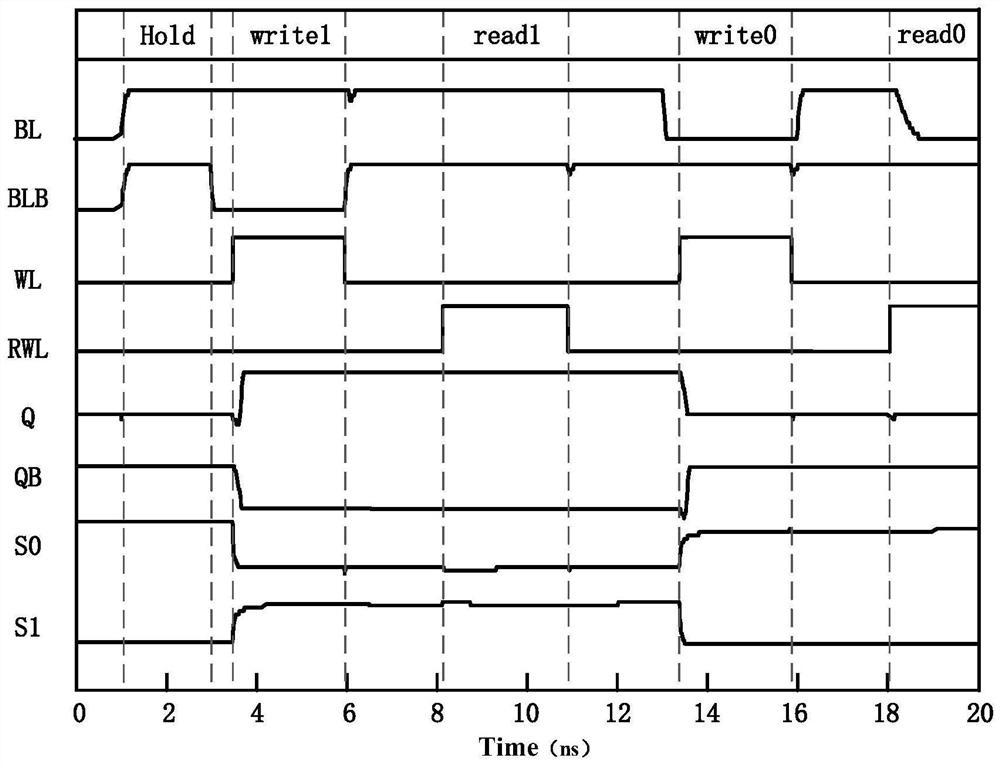

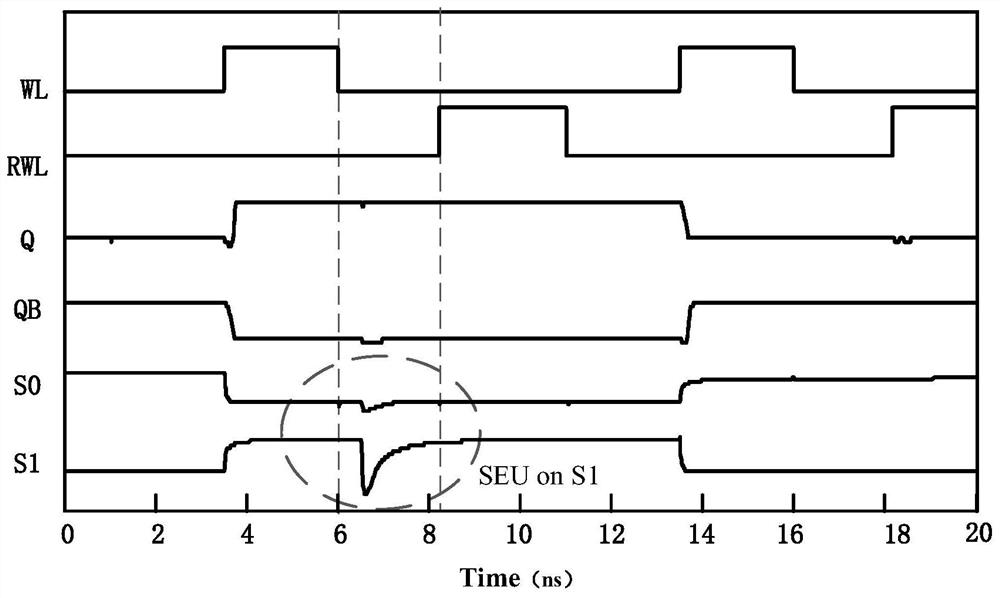

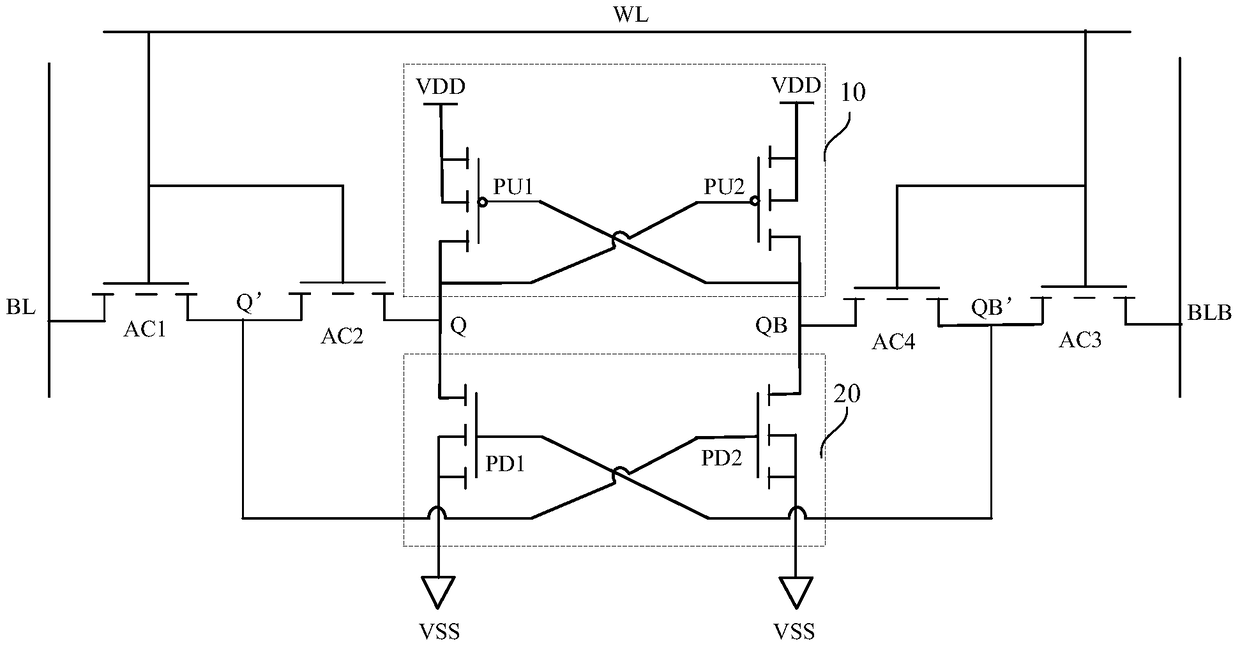

Read-write separated 14T radiation-resistant SRAM (Static Random Access Memory) storage unit circuit structure

ActiveCN112259143AImprove stabilityImprove read and write performanceDigital storageStatic random-access memoryHemt circuits

The invention discloses a read-write separated 14T radiation-resistant SRAM (Static Random Access Memory) storage unit circuit structure which comprises ten NMOS (N-channel Metal Oxide Semiconductor)transistors and four PMOS (P-channel Metal Oxide Semiconductor) transistors which are sequentially marked as N1 to N10 and P1 to P4, the PMOS transistors P1 and P2 are used as pull-up tubes, peripheral storage nodes are controlled by S1 and S0, and the PMOS transistors P3 and P4 are crossly coupled; NMOS transistors N3 and N4 are used as pull-down tubes, and peripheral nodes are cross-coupled by NMOS transistors N5 and N6; NMOS transistors N1 and N2 serve as pull-up tubes, peripheral storage nodes S0 and S1 reinforce internal nodes Q and QB by controlling NMOS transistors N3 and N4, peripheralnodes are all surrounded by the NMOS transistors, and the structure is called as a polarity reinforcing structure. The circuit structure can effectively optimize the stability of the unit, improve the read-write capability of the unit, and improve the single-particle and multi-particle upset resistance of the storage unit.

Owner:ANHUI UNIVERSITY

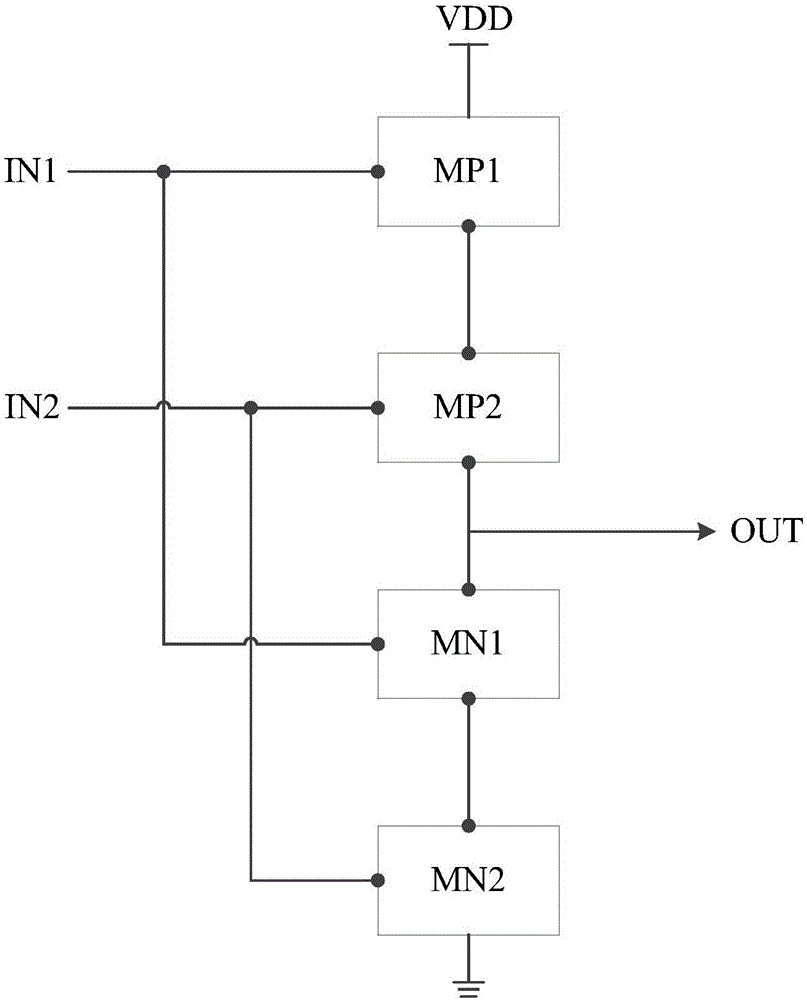

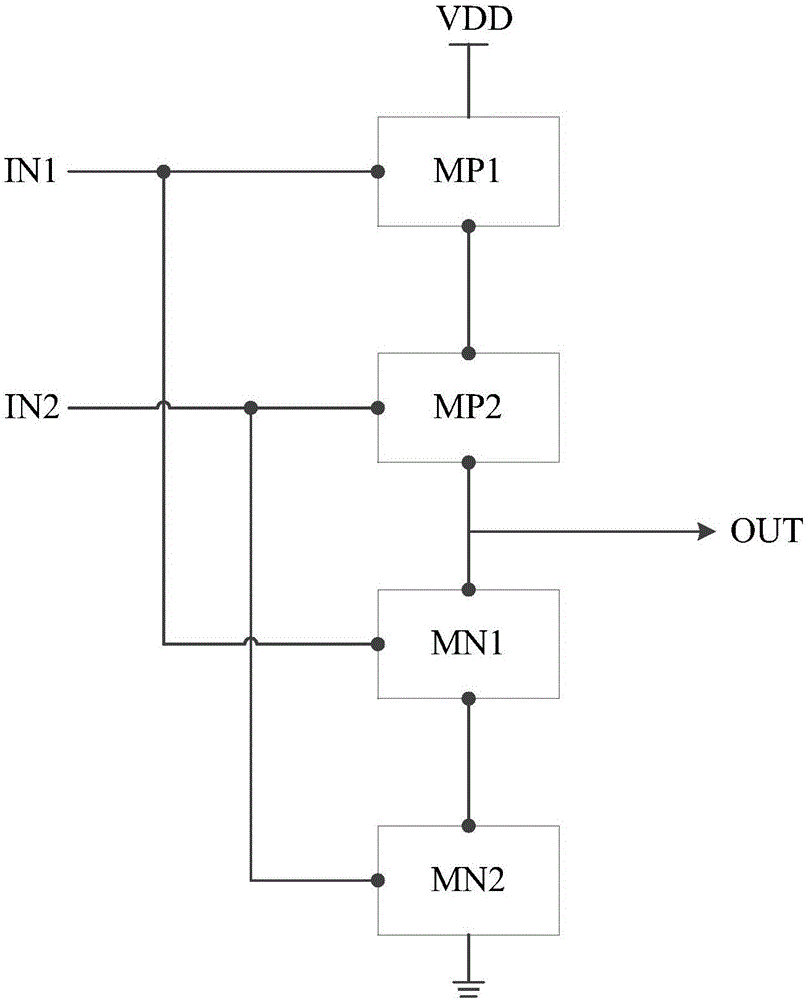

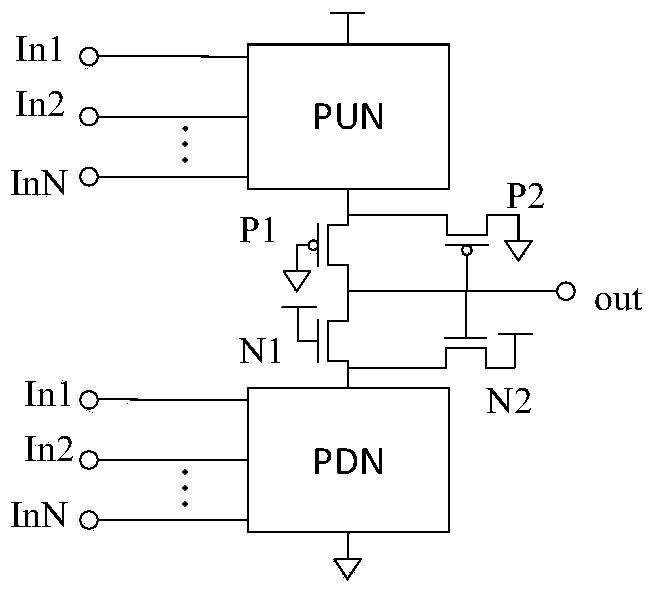

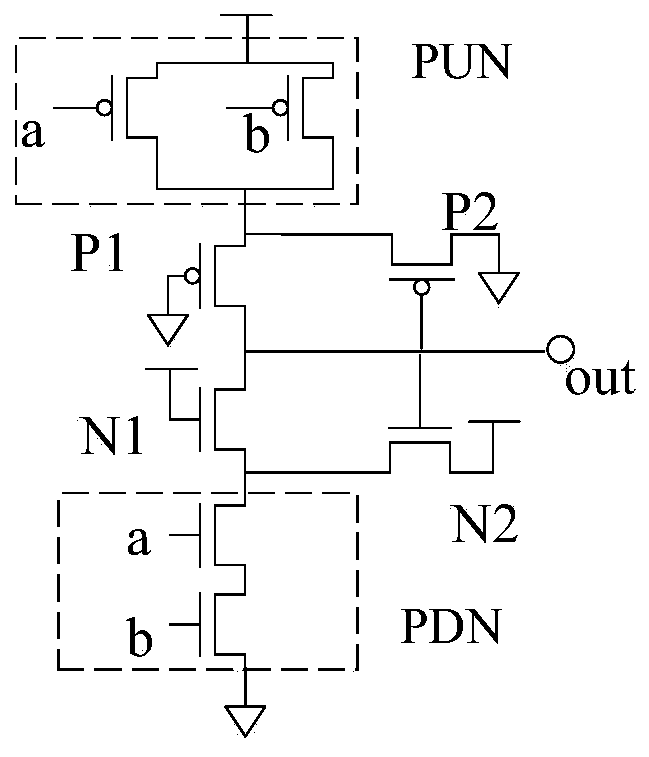

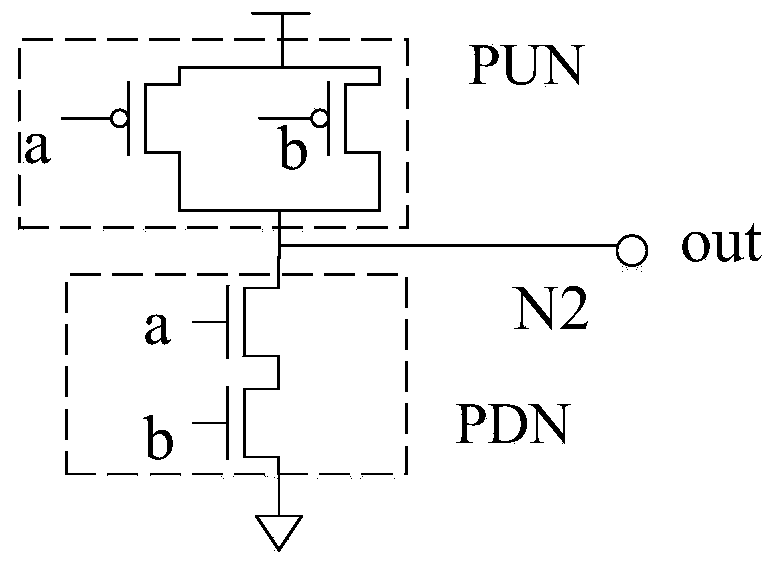

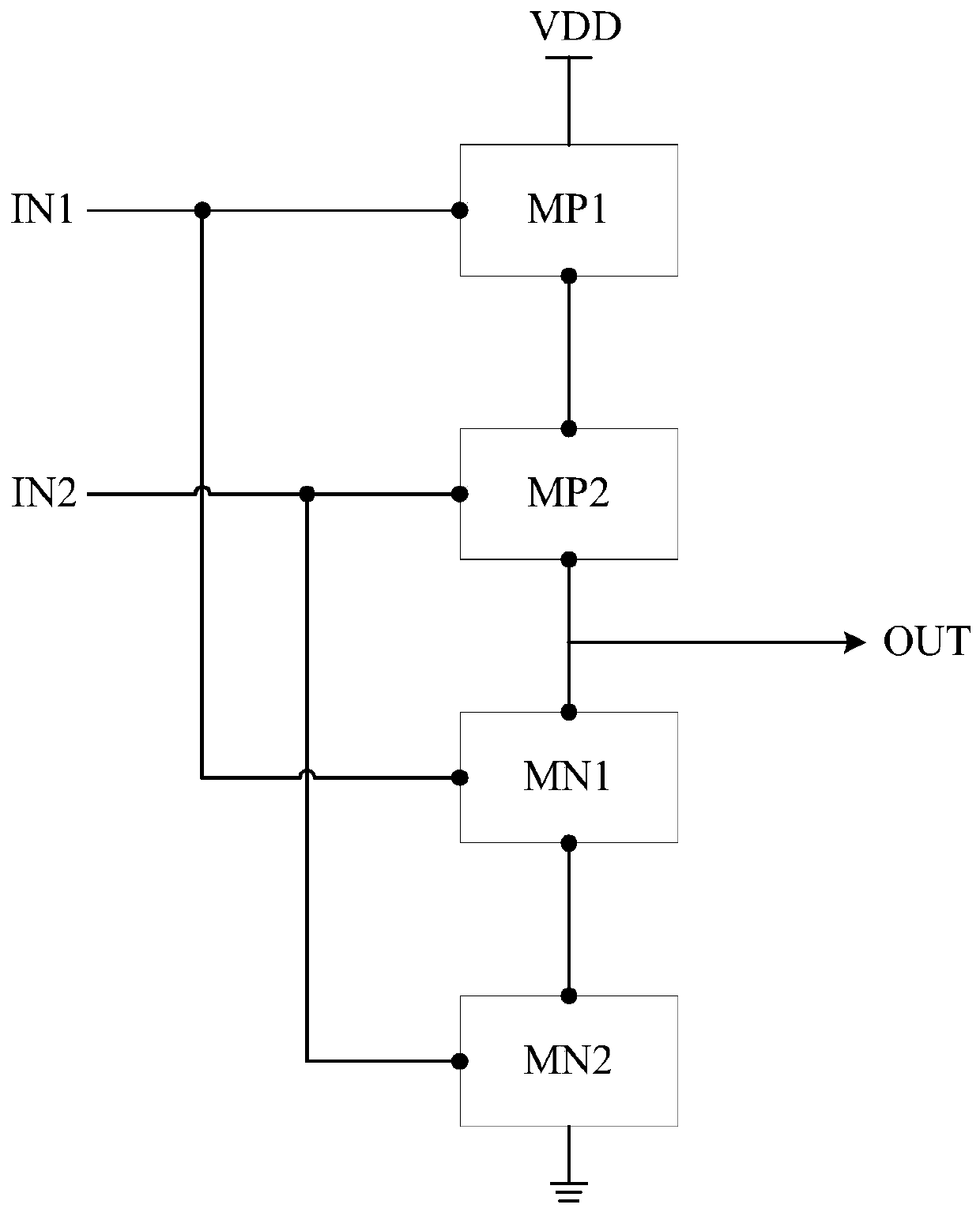

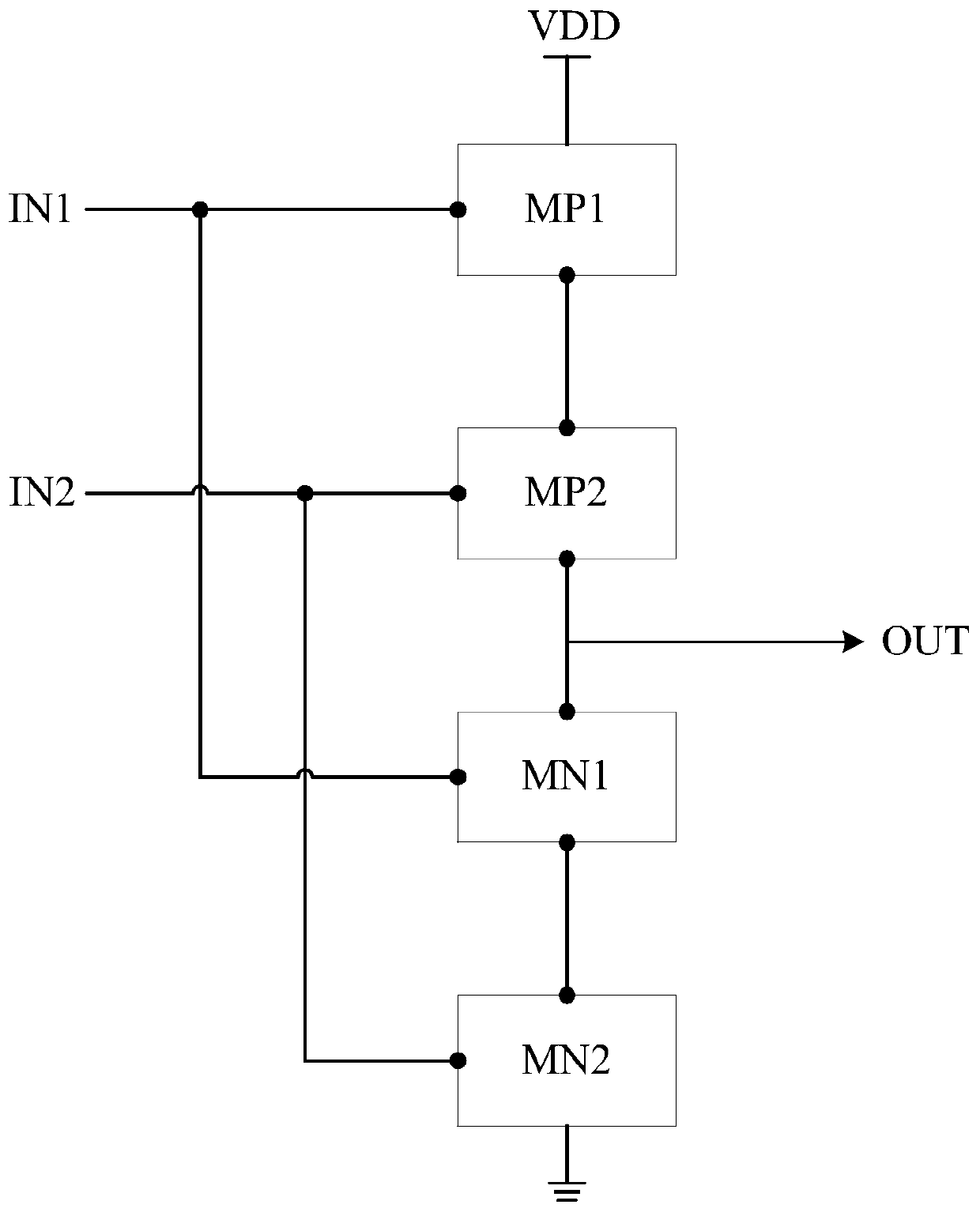

Radiation-proof reinforced circuit for a CMOS standard unit

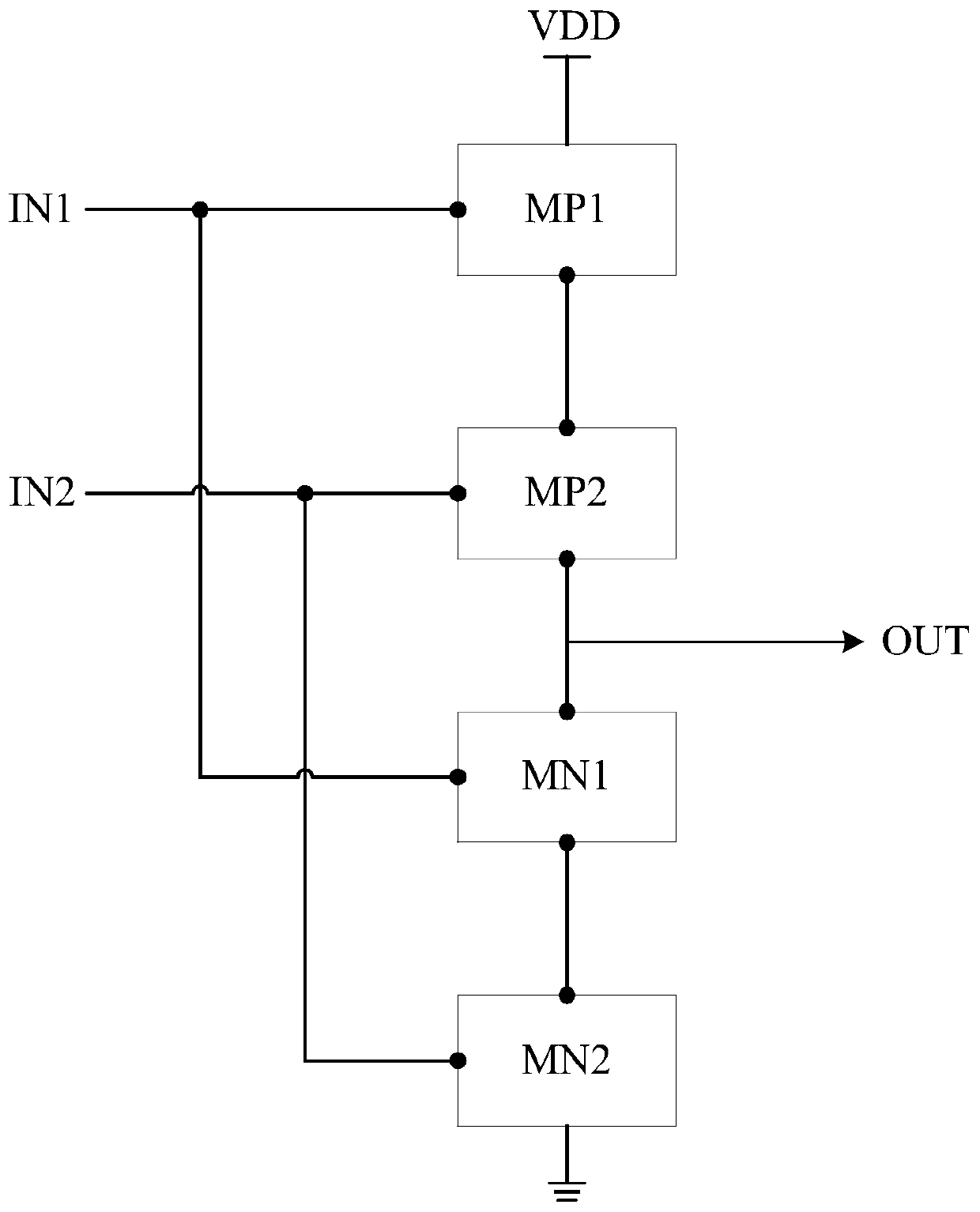

PendingCN110880928AImproved resistance to single-event upsetsSmall area overheadReliability increasing modificationsComputational physicsCMOS

The invention discloses a radiation-proof reinforced circuit for a CMOS standard unit. The radiation-proof reinforced circuit comprises a pull-up network (PUN) and a pull-down network (PDN) for realizing a logic function, two p-type channel field effect transistors P1 and P2, and two n-type channel field effect transistors N1 and N2. Figure 1 shows a universal logic gate unit with N inputs, and all inputs of the logic gate unit are simultaneously distributed to pull-up and pull-down networks. The grid electrode of a P1 is connected with a low level, and the grid electrode of an N1 is connectedwith a high level. The grid electrode of a P2 is connected with the output port, the source electrode is connected with the source electrode of P1, the drain electrode is connected with low level, the grid electrode of N2 is connected with the output port, the drain electrode is connected with high level, and the source electrode is connected with the drain electrode of N1. The sensitive nodes ofthe standard unit are subjected to radiation-proof reinforcement, so that the single event upset resisting effect of the standard unit is obviously improved on the premise that the area overhead is not large.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

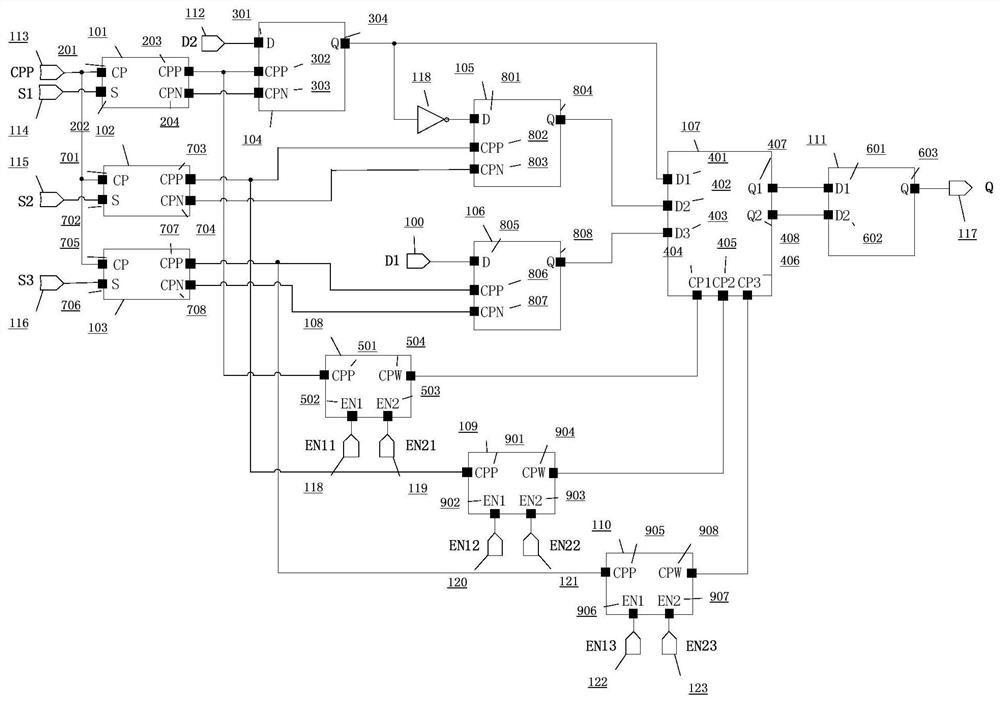

A Single Event Reinforced Programmable Double Data Rate Register Circuit and Control Method

ActiveCN108335708BImproved resistance to single event upsetImprove Flip EffectDigital storageDouble data rateFlip-flop

Owner:BEIJING MXTRONICS CORP +1

Single event hardening-based programmable double-data-rate register circuit and control method

ActiveCN108335708AImproved resistance to single event upsetImprove Flip EffectDigital storageDouble data rateOrder of magnitude

The invention discloses a single event hardening-based programmable double-data-rate register circuit and a control method. A circuit with a dual-redundancy interlocking structure is adopted for a conventional latch to realize single event hardening design of a register storage unit; and based on this, a clock generation circuit, a data multiplexer and a data retaining circuit are added for controlling a time sequence of multiple registers with dual-redundancy interlocking structures, so that multi-mode double-data-rate register functions can be realized. A single event hardening index is improved by three orders of magnitude in comparison with that of a conventional register, and programmable functions of a level latch, a single-data-rate edge trigger, a reverse-edge-mode double-data-rateedge trigger, a same-edge-mode double-data-rate edge trigger and the like can be realized, so that higher flexibility, better time sequence performance and extremely high anti-single event hardeningindex are achieved during use of a programmable user register by a user.

Owner:BEIJING MXTRONICS CORP +1

A kind of asynchronous set d flip-flop resistant to single event upset

ActiveCN106788380BImproved resistance to single event upsetAvoid feedback loopsReliability increasing modificationsElectric pulse generatorCMOSTransmission gate

Owner:SHENZHEN UNIV

A Static Random Access Memory Unit Anti-Single Event Effect

ActiveCN105321553BReduce power consumptionNatural Latch CapabilityDigital storageCouplingParasitic capacitance

The invention provides a static random memory unit having an anti-single event effect. The memory unit at least comprises: a first cross-coupling phase inverter being composed of a first pull-up transistor and a second pull-up transistor; a second cross-coupling phase inverter being composed of a first pull-down transistor and a second pull-down transistor; and a pass transistor which is composed of a first access transistor, a second access transistor, a third access transistor and a fourth access transistor. The static random memory unit can effectively prolong the feedback time required of turning the memory unit, so that the anti-single event upset capability of the memory unit can be improved in the situation that recovery time is not changed. The processes of the static random memory unit are completely compatible with digital logic process. The static random memory unit is less in parasitic capacitance, is low in power consumption, has a natural anti-single event latch-up capability and is free of increase of extra process cost.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

A Synchronous Reset D Flip-Flop Resistant to Single Event Upset

ActiveCN106712743BImproved resistance to single event upsetAvoid feedback loopsElectric pulse generatorDual modeFlip-flop

The invention is suitable for the technical field of D triggers, and provides a synchronous reset D trigger for preventing single event upset. The D trigger comprises: a clock signal input circuit, a reset signal input circuit, a master latch buffer circuit, a slave latch buffer circuit, a master latch and a slave latch, and both of the master latch and slave latch are dual mode redundancy reinforcement latches. Compared with the prior art, in the synchronous reset D trigger provided by the invention, the buffer circuits are added in front of the master latch and slave latch, so the single event upset ability of the synchronous reset D trigger is improved, dual mode redundancy reinforcement is carried out on the master latch and slave latch, namely the master latch and slave latch are separated to a pull up PMOS tube and a pull down PMOS tube in a C2MOS circuit, which are redundant to each other, therefore a possible feedback circuit caused by single event transient pulses is avoided, the C2MOS circuits in the circuits of the master latch and slave latch are improved, clock signals control the circuits through SMOS transmission rates, and the single event upset ability of the synchronous reset D trigger is further improved.

Owner:SHENZHEN UNIV

A Single Event Hardened Programmable User Register Circuit

ActiveCN105790755BImprove Flip EffectImproved resistance to single event upsetLogic circuits using elementary logic circuit componentsControl powerProcessor register

The invention relates to a single-particle reinforced programmable user register circuit. Single-particle reinforcement design of a user register is realized by adopting a circuit having a dual-redundant interlocking structure in the traditional latch; on the basis, a multi-mode programmable control switch is additionally provided, such that the user register can be switched among multiple working modes; a multi-power and multi-mode controller circuit is adopted; a user logic power supply is used in a data path; and a multi-mode switching control power supply is used on a programmable switch, such that time sequence influence generated by the single-particle reinforcement design of the dual-redundant interlocking structure and the programmable switch can be completely eliminated. Compared with the traditional register, the single-particle reinforcement index in the invention is increased by three orders of magnitude; furthermore, programmable functions, such as an edge trigger, a level latch, synchronous / asynchronous setting / resetting and data retention, can be realized; and thus, users have relatively high flexibility, better time sequence performance and ultra-high single-particle reinforcement resistant index while using the programmable user register.

Owner:BEIJING MXTRONICS CORP +1

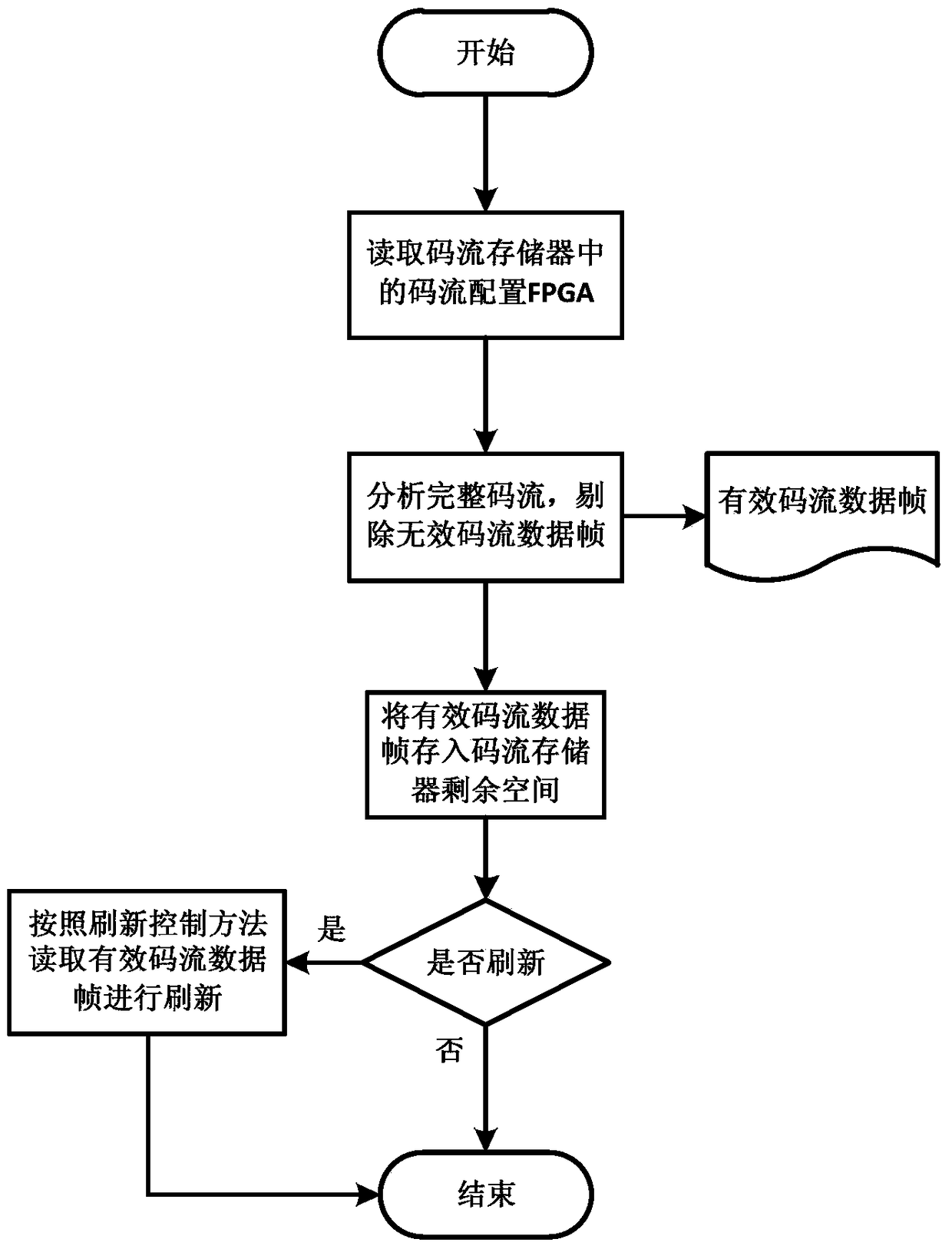

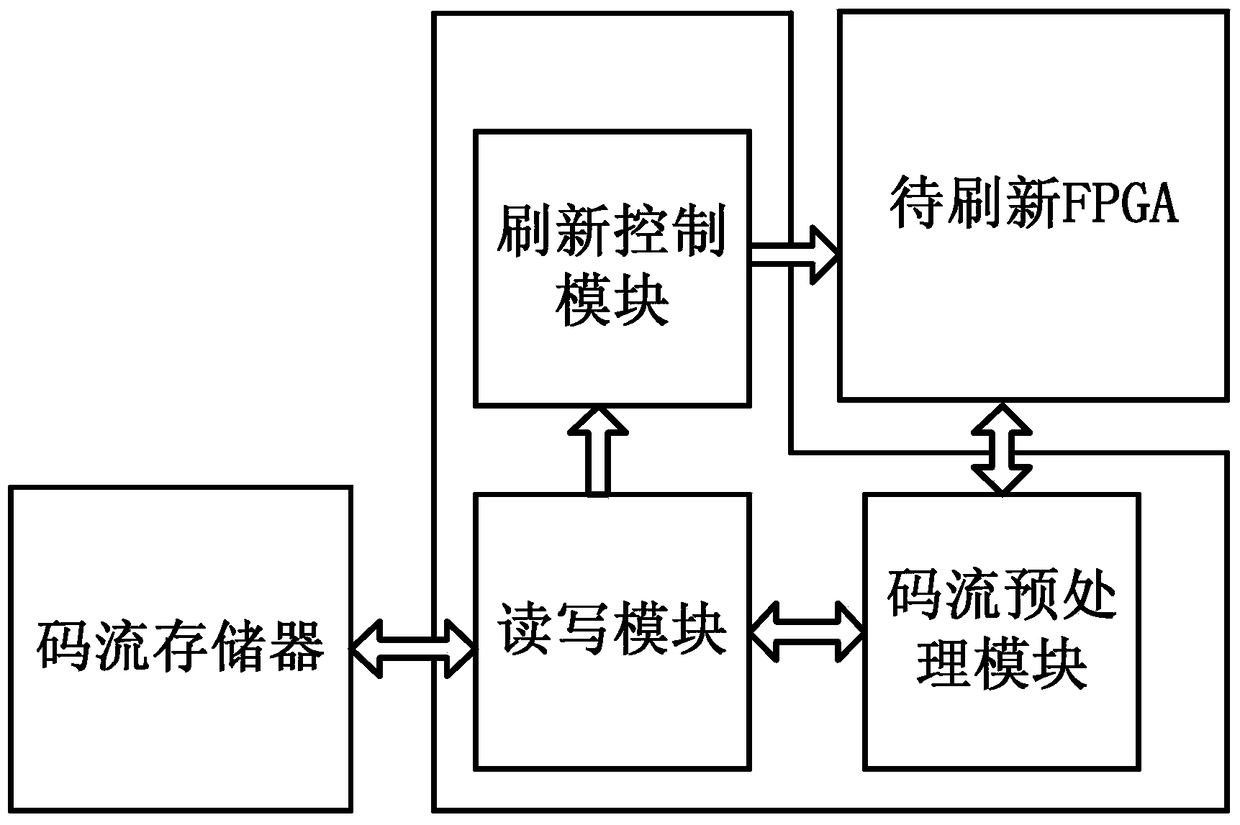

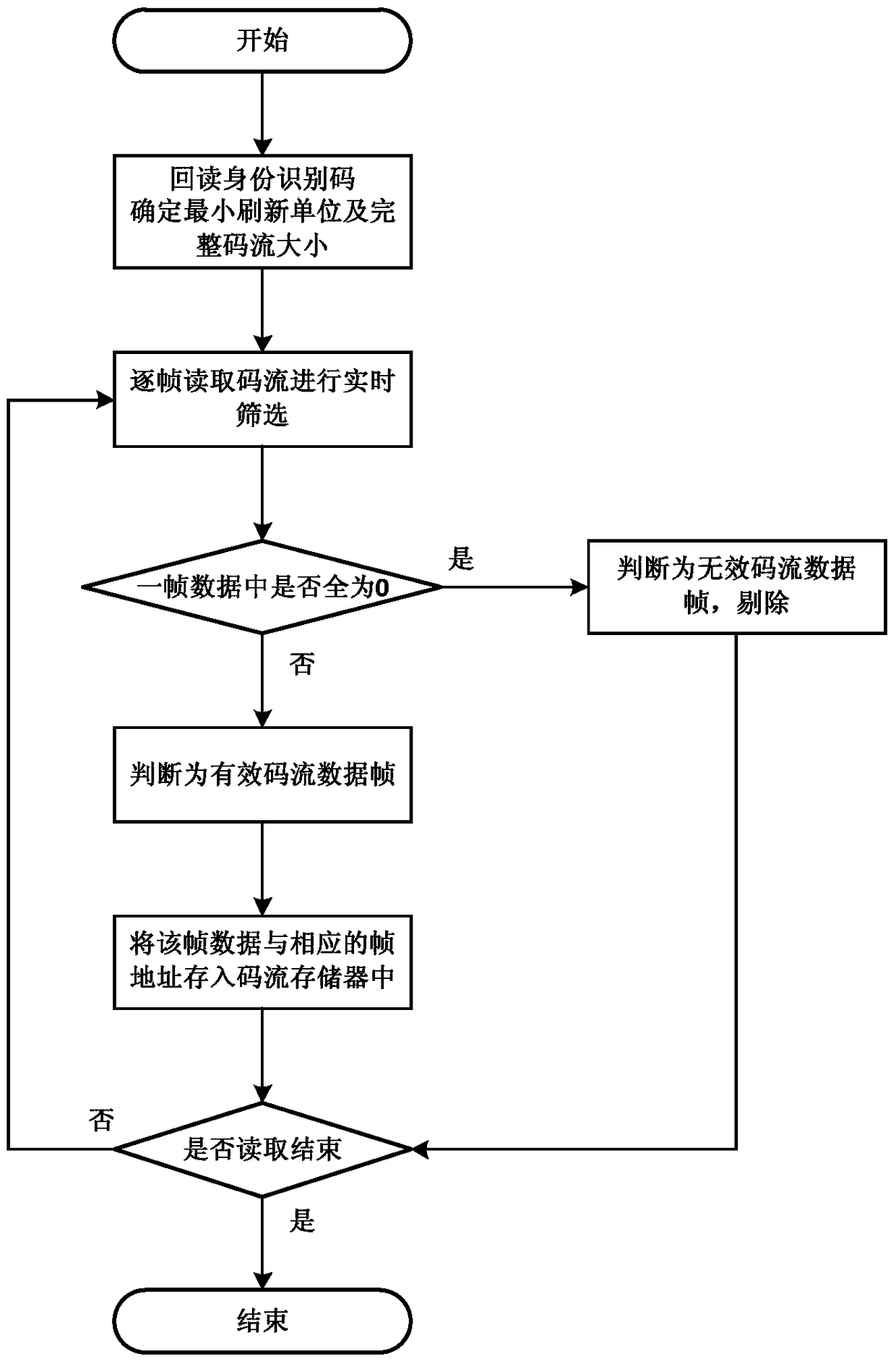

An Intelligent Refresh Control Method Based on Code Stream Preprocessing

ActiveCN105760243BImproved resistance to single event upsetReduce data volumeNon-redundant fault processingControl systemInvalid Data

The invention relates to an intelligent refreshing control method based on code stream preprocessing.The method is achieved through a refreshing control system which comprises a code stream memory, a refreshing module and an FPGA; the refreshing module reads code streams in the code stream memory and screens data frames of the code streams in real time to remove invalid code stream data frames and write the remaining valid code stream data frames in remaining space of the code stream memory in real time, and when refreshing is needed, the refreshing module reads the valid code stream data frames in the code stream memory to refresh the FPGA.According to the method, the invalid data is completely removed before the FPGA is refreshed, only the valid data is refreshed, the transmitted data volume during refreshing is significantly decreased, therefore, the actual refreshing period can be effectively shortened on the premise that the refreshing basic frequency of a clock is not increased, the actual refreshing frequency is increased, and then the anti-single particle turnover capacity of an SRAM-type FPGA device to be refreshed is improved.

Owner:BEIJING MXTRONICS CORP +1

A d-flip-flop resistant to single-event upset

ActiveCN106505976BImproved resistance to single event upsetImprove Flip EffectElectric pulse generatorCMOSTransmission gate

The present invention is applied to the D trigger technology field, and provides an anti-single-event upset D trigger. The D trigger comprises a clock signal input circuit, a main latch buffer circuit, a slave latch buffer circuit, a main latch and a slave latch. The main latch and the slave latch are both dual-mode redundant reinforcing latches. Compared to the prior art, buffer circuits are added at the fronts of the main latch and the slave latch to improve the anti-single-event upset capacity of the D trigger, the main latch and the slave latch are subjected to dual-mode redundant reinforcing to separate into pull-up PMOS tubes and pull-down NMOS tubes, which are mutually redundant, in C2MOS circuits so as to avoid the feedback loop caused by the single-particle transient pulse in the slave latch, the C2MOS circuits in the main latch and the slave latch circuits are improved, and the control of the circuits through clock signals is realized through the CMOS transmission gate so as to further improve the anti-single-event upset capacity of the D trigger.

Owner:SHENZHEN UNIV

A d-flip-flop resistant to single-event upset

ActiveCN105897223BSmall area overheadEliminate Single Event Sensitivity IssuesElectric pulse generatorEngineeringSingle event upset

The invention discloses a D trigger resistant to single event upset. The D trigger is formed by master and slave latches connected in series. The master latch and the slave latch have completely same structure. The core of a latch is no longer composed of two end-to-end inverters, but six PMOS transistors P1 to P6 and six NMOS transistors N1 to N6. The master latch or the slave latch of the invention can be formed by adding a clock-controlled transistor to the core of the latch. Compared with triplication redundancy in the prior art, the D trigger not only save the area of an election circuit, but also eliminate single event sensitivity due to the election circuit. Further, the D trigger is lower in single event sensitivity and better in single event upset resistance when storing a numerical value 0. Since many triggers are required to hold the same numerical value for a long time in practical application, the invention is significant to enhance the single event upset resistance of the kind of the triggers.

Owner:NAT UNIV OF DEFENSE TECH

Settable-reset scan-structured d-flip-flops resistant to single-event upsets and single-event transients

ActiveCN103825586BExcellent anti-single event upset abilityImproved resistance to single event upsetElectric pulse generatorDual modeSingle event upset

Owner:NAT UNIV OF DEFENSE TECH

D trigger provided with scanning structure and resisting single event upset

ActiveCN102394601BExcellent anti-single event upset abilityImproved resistance to single event upsetReliability increasing modificationsElectric pulse generator circuitsAviationSingle event upset

The invention discloses a D trigger provided with a scanning structure and resisting single event upset, and aims to improve the single event upset resistance of the D trigger provided with the scanning structure. The D trigger comprises a clock circuit, a scanning control buffer circuit, a main latch, a slave latch, a first phase inverter circuit and a second phase inverter circuit, wherein the main latch comprises 16 PMOS (P-channel Metal Oxide Semiconductor) tubes and 16 NMOS (N-Mental-Oxide-Semiconductor) tubes; the slave latch comprises 10 PMOS tubes and 10 NMOS tubes; both the main latch and the slave latch adopt bimodule redundant reinforcement; and in the main latch and the slave latch, C2MOS circuits are improved, that is, a pull-up circuit and a pull-down circuit in redundant relation in each C2MOS circuit are separated. The D trigger has strong single event upset resistance, is suitable for standard cell library for a reinforced integrated circuit resisting single event upset, and is used in the fields of aviation, aerospace, and the like.

Owner:NAT UNIV OF DEFENSE TECH

Single event upset resistant settable and resettable scan structure D flip-flop

ActiveCN102394599BExcellent anti-single event upset abilityImproved resistance to single event upsetReliability increasing modificationsElectric pulse generator circuitsComputer architectureHemt circuits

Owner:NAT UNIV OF DEFENSE TECH

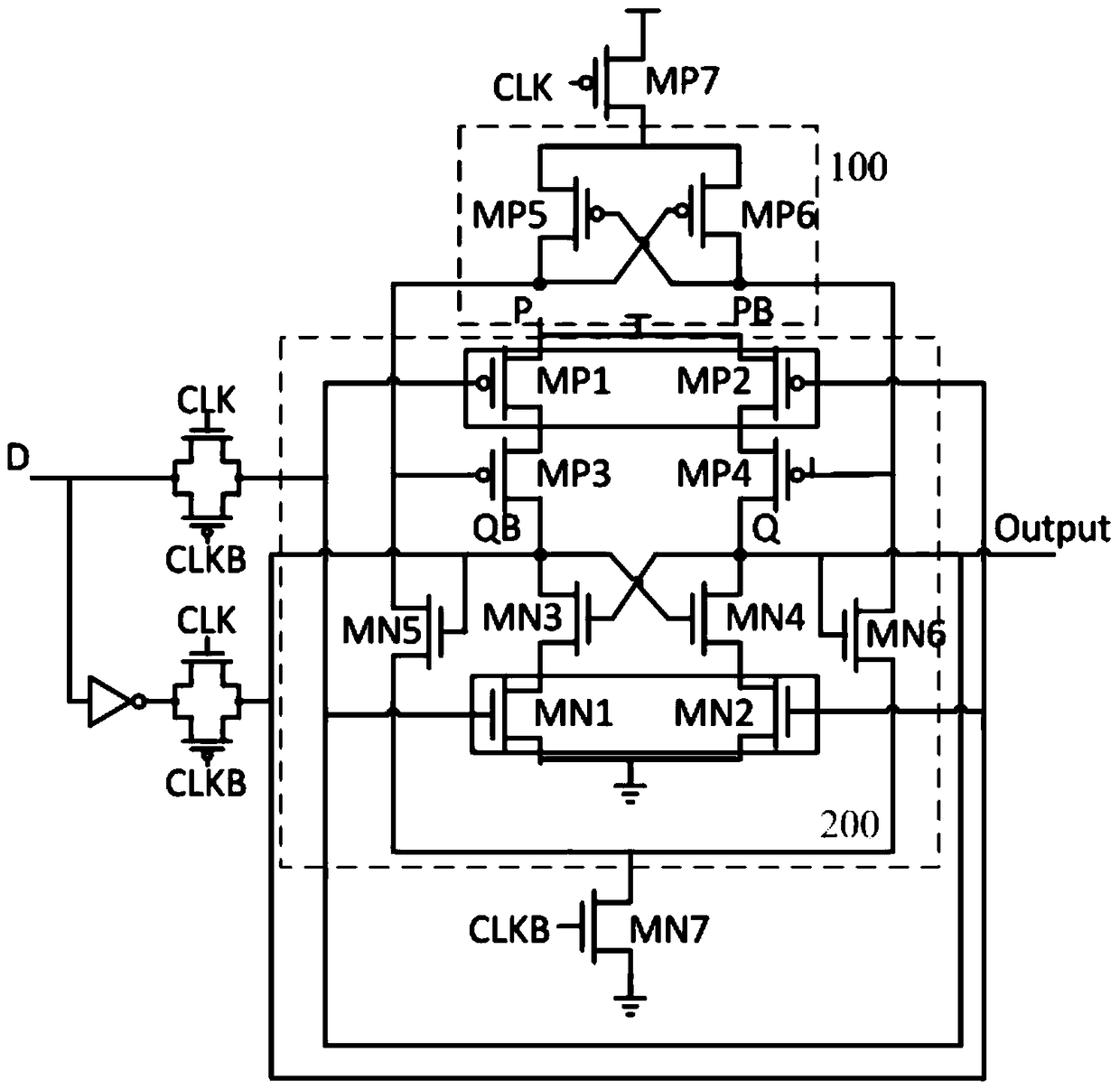

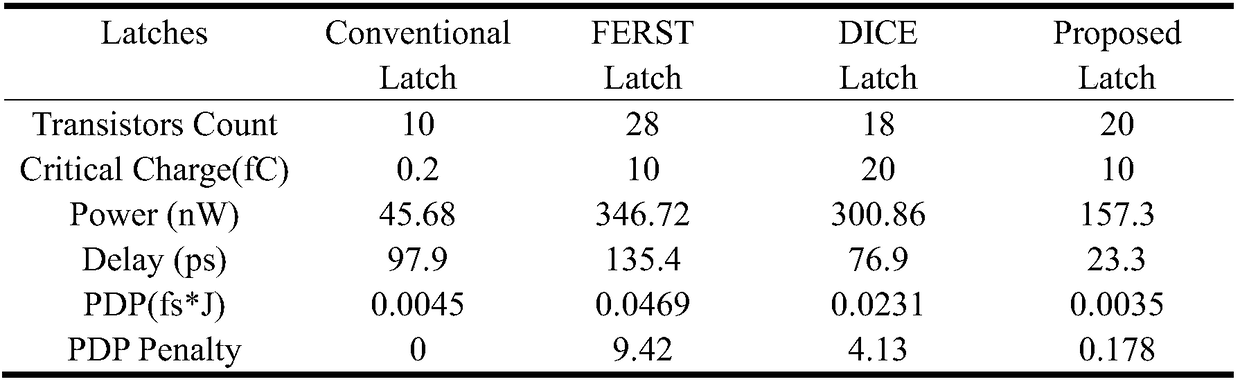

A single-event upset-resistant latch with low delay power product

ActiveCN105577146BIncrease write speedGood resistance to single event upsetElectric pulse generatorNegative feedbackCMOS

The invention discloses an anti-single-event-upset latch register with a low delay-power product. By use of a novel cross coupling structure capable of isolating an upset state, recovery of the upset state is accelerated through design of a reasonable negative feedback passage. In case of a data transparent mode, negative feedback is cut off so as to improve the writing speed of a circuit. A simulation result under a 40nm CMOS technology shows that the critical charge ratio of the latch register provided by the invention is more than 50 times higher than that of a conventional latch register. The delay-power product is only 0.0035fs*J, and the propagation time delay under the non-loaded condition is only 23.3ps, which is lower than that of a same-type latch register.

Owner:XI AN JIAOTONG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com