A single-event upset-resistant latch with low delay power product

An anti-single-event, latch technology, applied in the field of latches against single-event flip, can solve the problems of latch flip, circuit high power consumption delay product hardware overhead, large hardware overhead, etc., to speed up writing speed, improving the ability of anti-single-event flipping, and the effect of good anti-single-event flipping ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention is described in further detail below in conjunction with accompanying drawing:

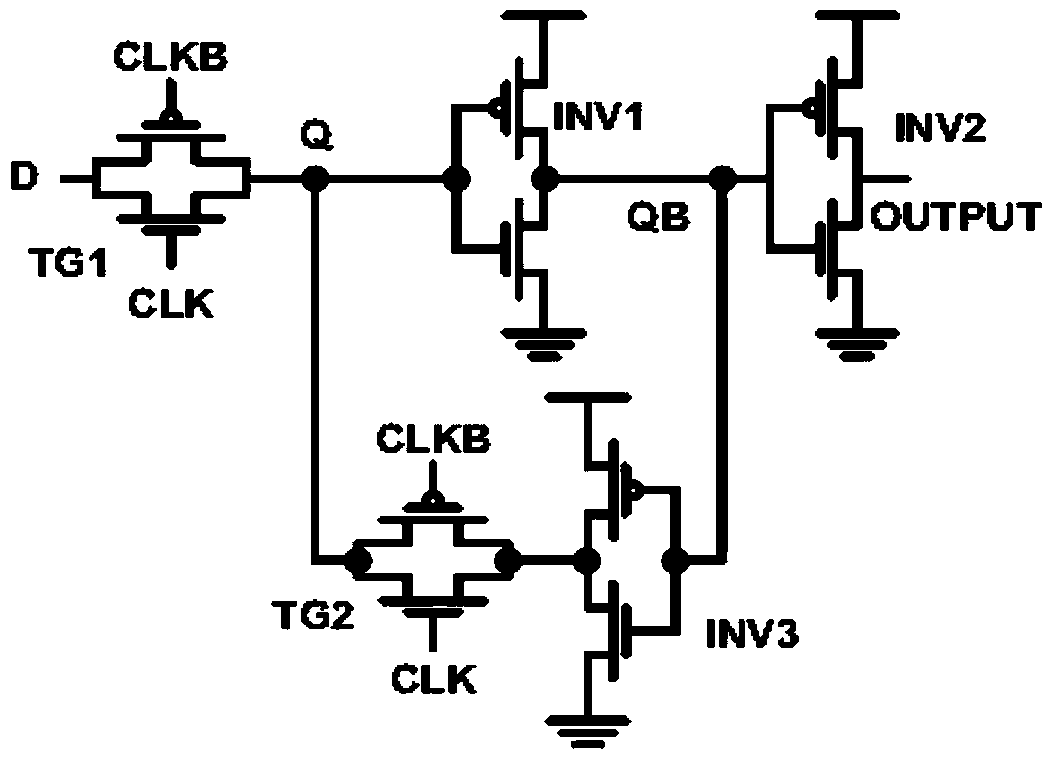

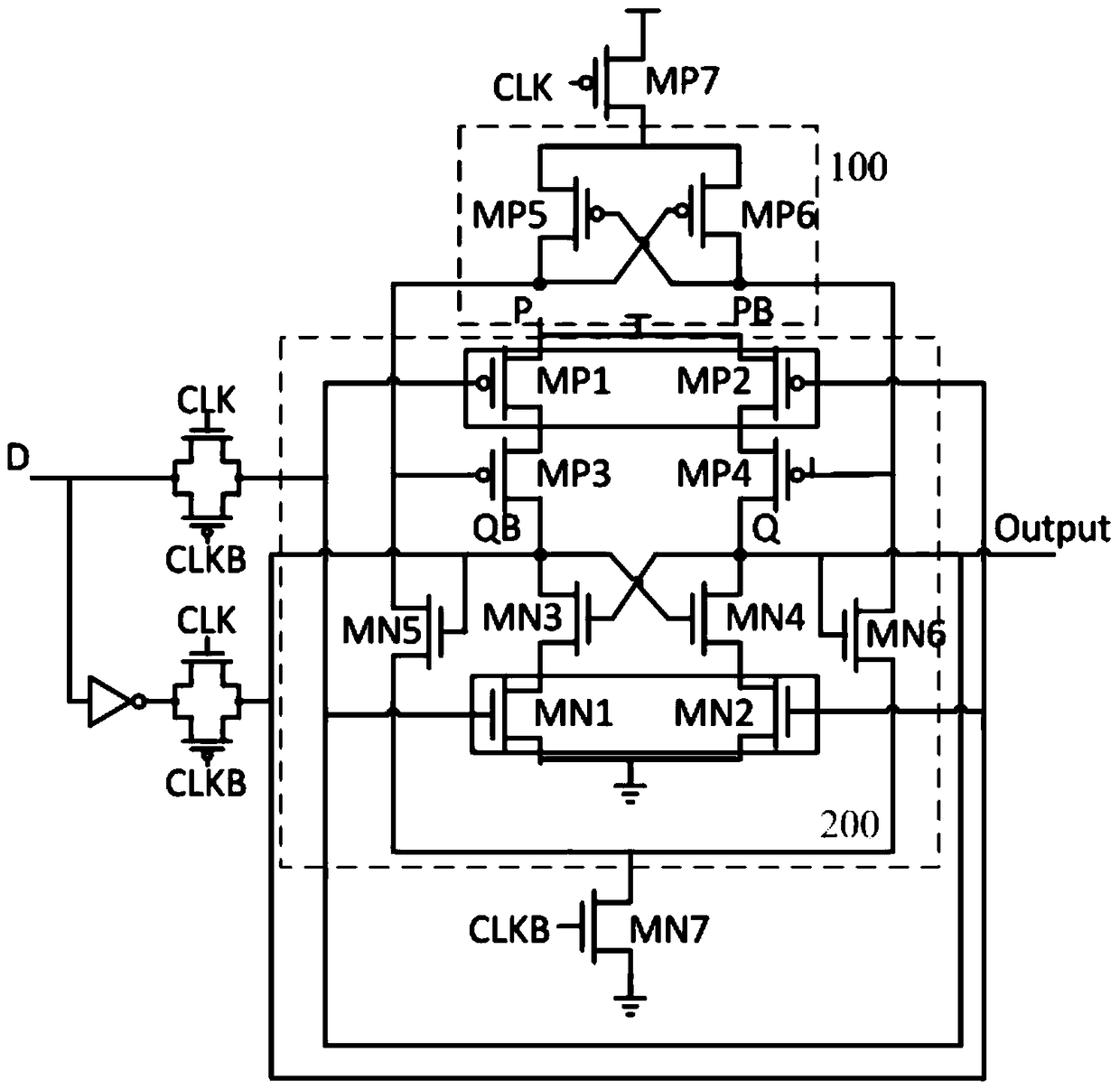

[0019] see figure 1 and figure 2 , the present invention is based on the traditional latch (such as figure 1 As shown), two cross-coupled transistors are used to form a negative feedback path to speed up the recovery speed of the flipped sensitive node. The entire anti-radiation D latch circuit has four external ports, two input ports (D, CLK), and two complementary output ports (Q, QB).

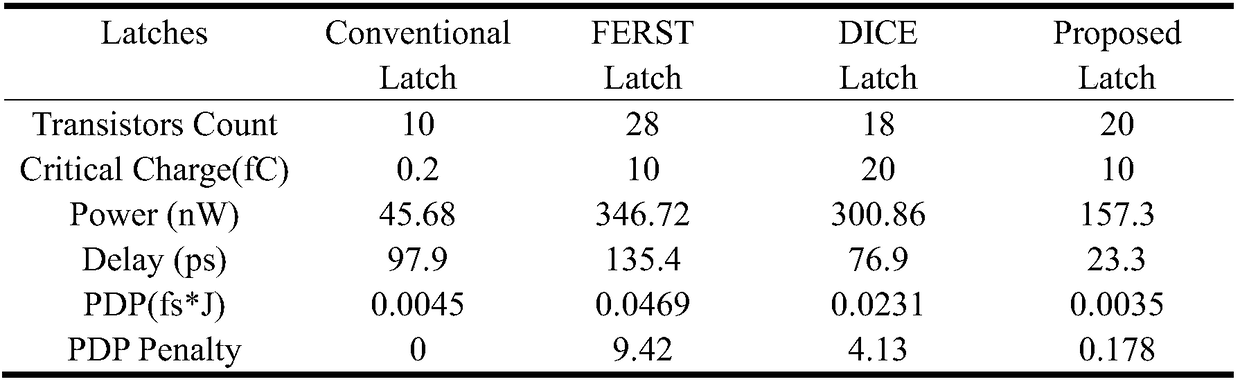

[0020] Add four redundant transistors (MP1, MP2, MN1, MN2), when the latch is working in the normal data writing stage, the four transistors controlled by the storage nodes Q and QB will be turned off, thus cutting off the negative circuit. The feedback path can effectively block the interference of the negative feedback path to data writing, and improve the writing speed of the circuit. When the circuit works in the latched state, the node flipping state caused by the single ev...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More