Verification method and system for memory disambiguation in processor

A verification method and processor technology, applied in the field of processors, can solve problems such as outdated data, and achieve the effect of fast and effective debugging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

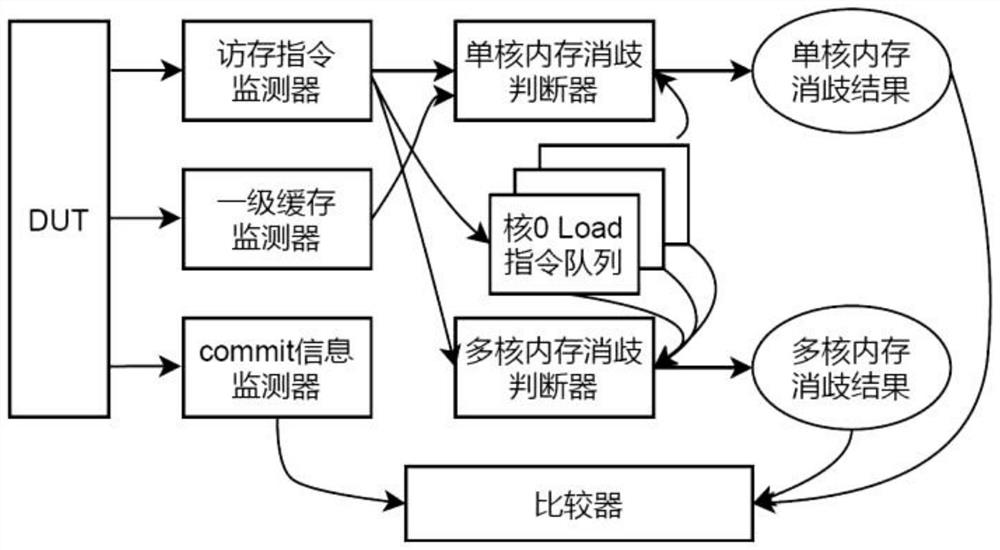

[0067] This embodiment provides a method for verifying memory disambiguation in a processor. The method verifies the memory disambiguation logic caused by single-core, multi-core and unaligned access by monitoring the execution information of the load instruction and the store instruction in the DUT. By comparing the memory disambiguation results of the DUT and the memory disambiguation results of the checker, it is judged whether it is necessary to re-flash the pipeline and from which instruction to re-flash. If the re-flash pipeline information is inconsistent with the DUT, an error message will be reported immediately.

[0068] The method of this embodiment supports the verification of memory disambiguation in the case of a single core, including memory disambiguation caused by a store instruction and memory disambiguation caused by a level-1 cache line being kicked out.

[0069] The method of this embodiment supports memory disambiguation verification in a multi-core system...

Embodiment 2

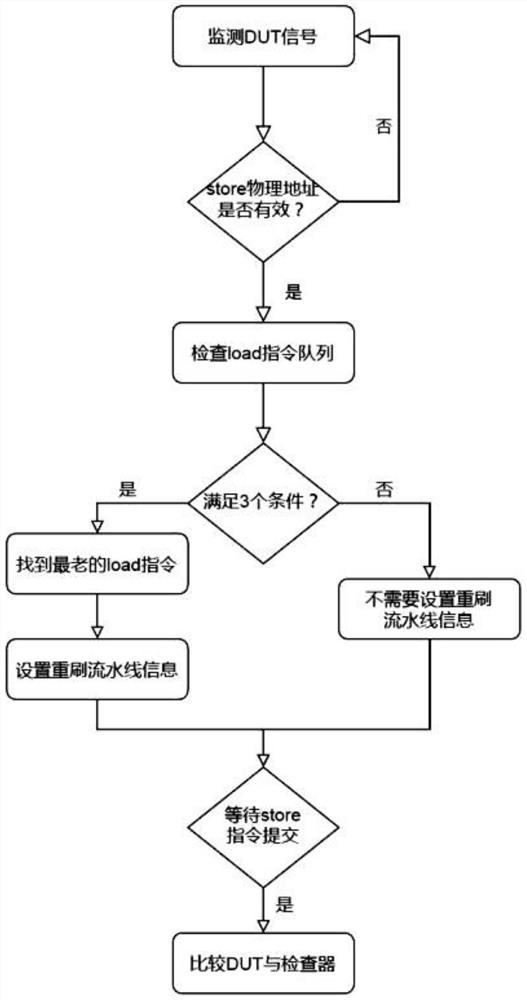

[0073] On the basis of Embodiment 1, this embodiment provides a memory disambiguation verification process caused by a store instruction in a single core, refer to figure 2 As shown, the details are as follows:

[0074] Monitor the store instruction in the DUT. After the store instruction obtains the physical address, the single-core memory disambiguation judger starts to find whether there is a load instruction that meets the following three conditions in the core;

[0075] a) The access scope of the Load instruction overlaps with the access scope of the store instruction;

[0076] b) The Load command has obtained the data;

[0077] c) Load instructions are younger than store instructions in program order.

[0078] If there is a load instruction that satisfies the above conditions, the single-core memory disambiguation judger performs the following operations:

[0079] a) Compare the age information of these load instructions and find out the oldest one;

[0080] b) Stor...

Embodiment 3

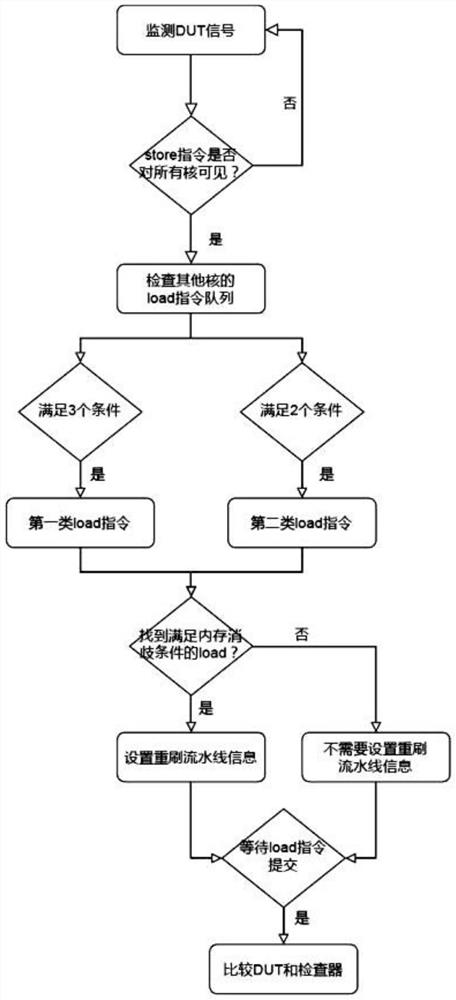

[0084] On the basis of Embodiment 2, this embodiment provides a memory disambiguation verification process caused by cache kicking rows in a single core as follows:

[0085] Monitor whether there is a first-level cache line being kicked out in the DUT. If so, the single-core memory disambiguation judge starts to find out whether there are two types of load instructions that meet the conditions in the core;

[0086] If the first type of load instruction meets the following three conditions, the load instruction flag needs to re-refresh the pipeline flag:

[0087] a. The physical address of the Load instruction is the same cache line as the cache line being kicked out;

[0088] b.Load instruction has obtained data;

[0089] c. The data of the Load command is not obtained from the core forward;

[0090] If the second type of load instruction meets the following two conditions, the load instruction may need to bring reflashing pipeline information when committing:

[0091] a. T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More