Method for improving STI and FG poly filling hole process window simultaneously

A process window and cavity filling technology, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of unrecorded EM combination AA and silicon nitride morphology adjustment, and achieve the effect of reducing cost and debugging cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

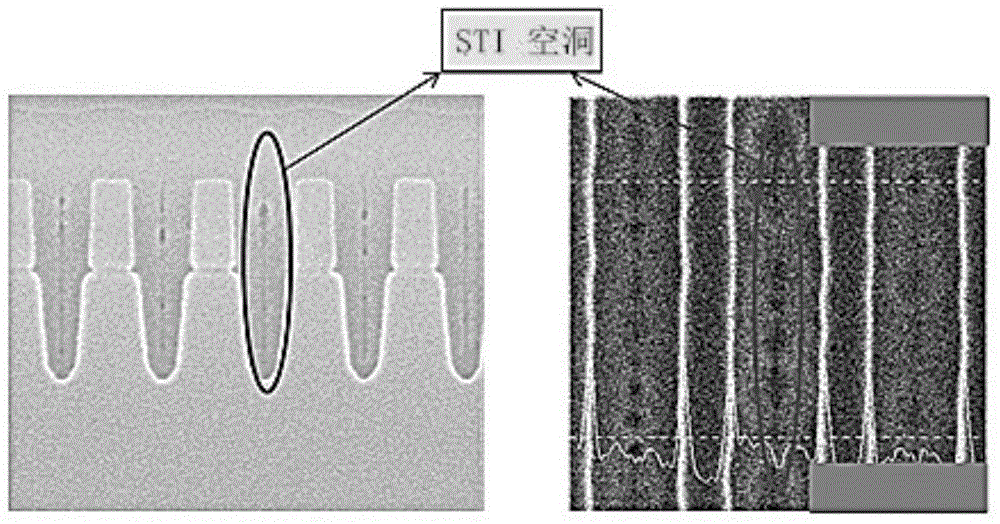

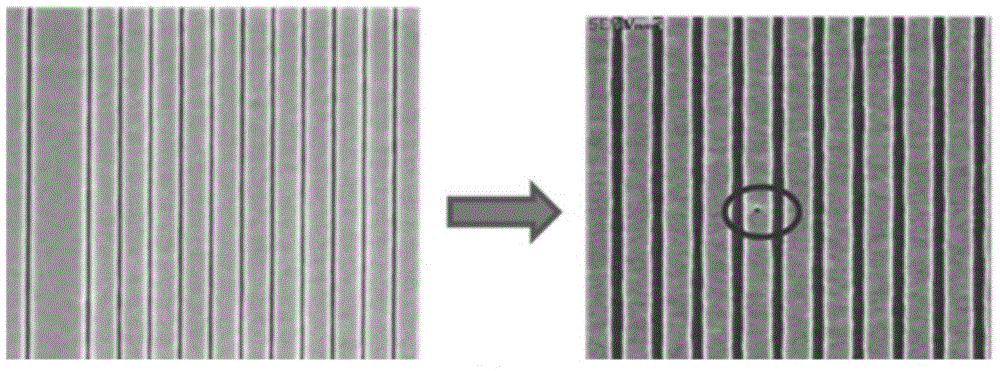

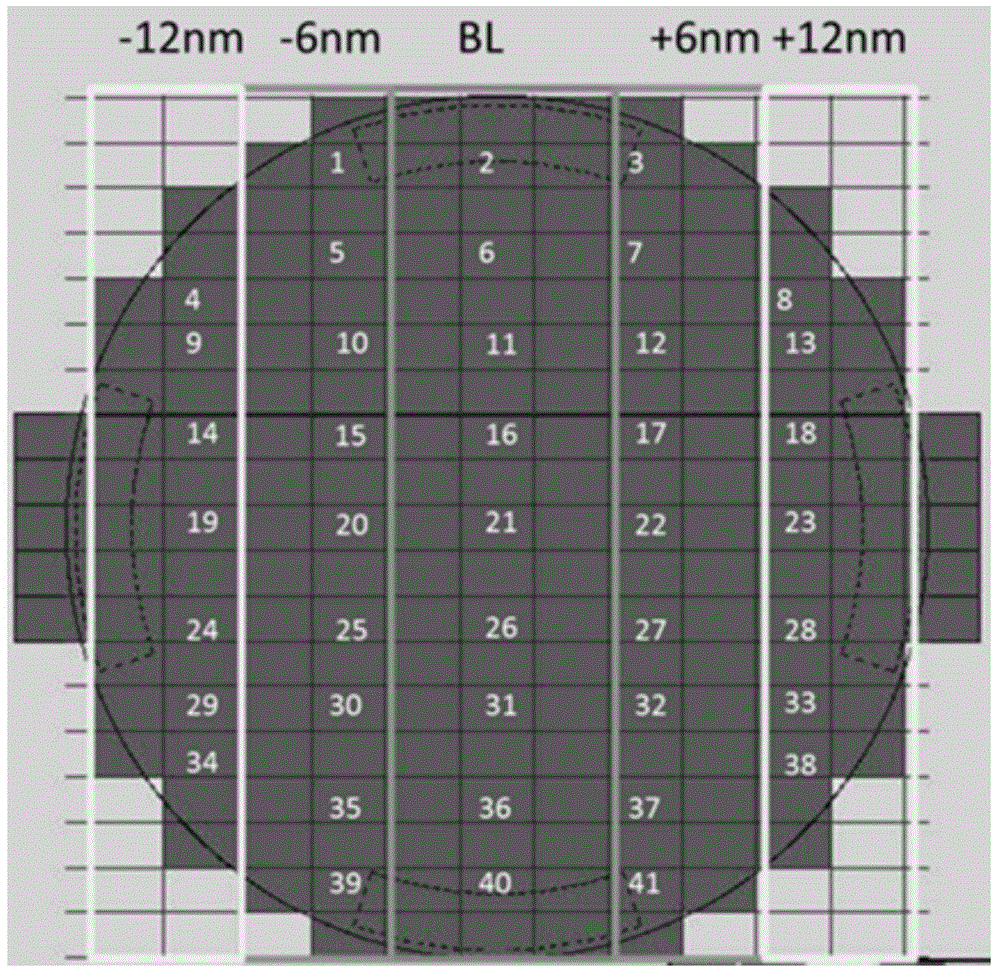

[0027] The present invention provides a method for simultaneously improving the process window of STI and FGPoly filling voids, which can be applied in the field of semiconductor production, and can preferably be applied to technologies such as 65 / 55nm and 45 / 40nm technology nodes, and applied to technology platforms such as MemoryFlasheFlash And in the technical module of PIE, when this method is used, the active region and the morphology of silicon nitride can be adjusted by lithography size EM, combined with FGCMP post-wet chemical solvent etching, and then scanning electron microscopy can be used to quickly and effectively Debugging and observing the process window of STI and FG filling voids accurately, which greatly reduces the cost and debugging cycle compared with the single-step traditional method.

[0028] The core idea of the present invention is to first define the size of the active area from small to large by using the active area photolithography process EM, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com