Semiconductor structure and forming method thereof

A semiconductor and device structure technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve the problems of difficult channel and poor control ability of gate to channel, so as to reduce the probability of blocking and realize The effect of electrical isolation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

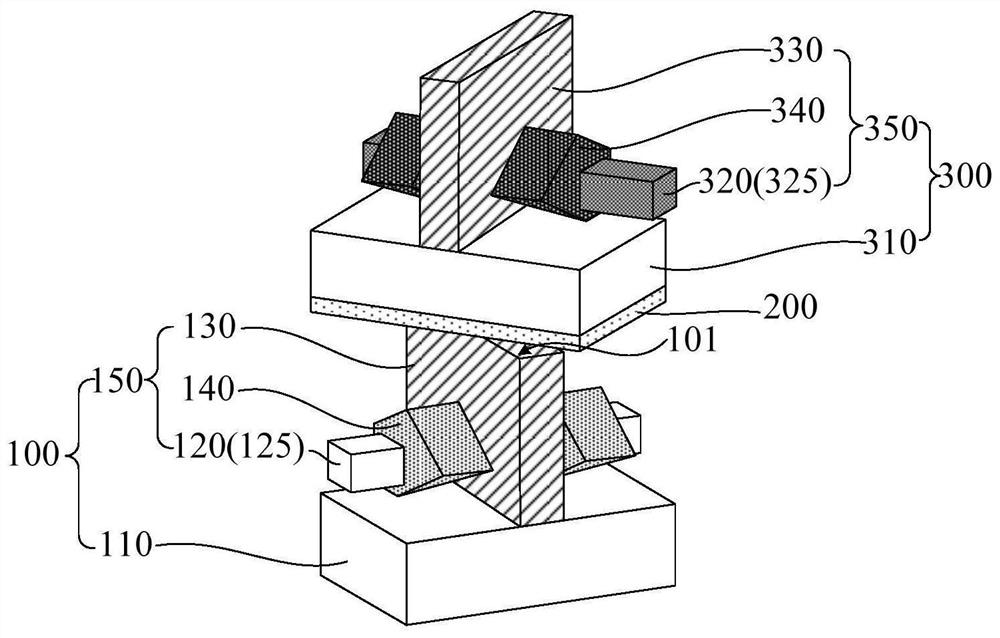

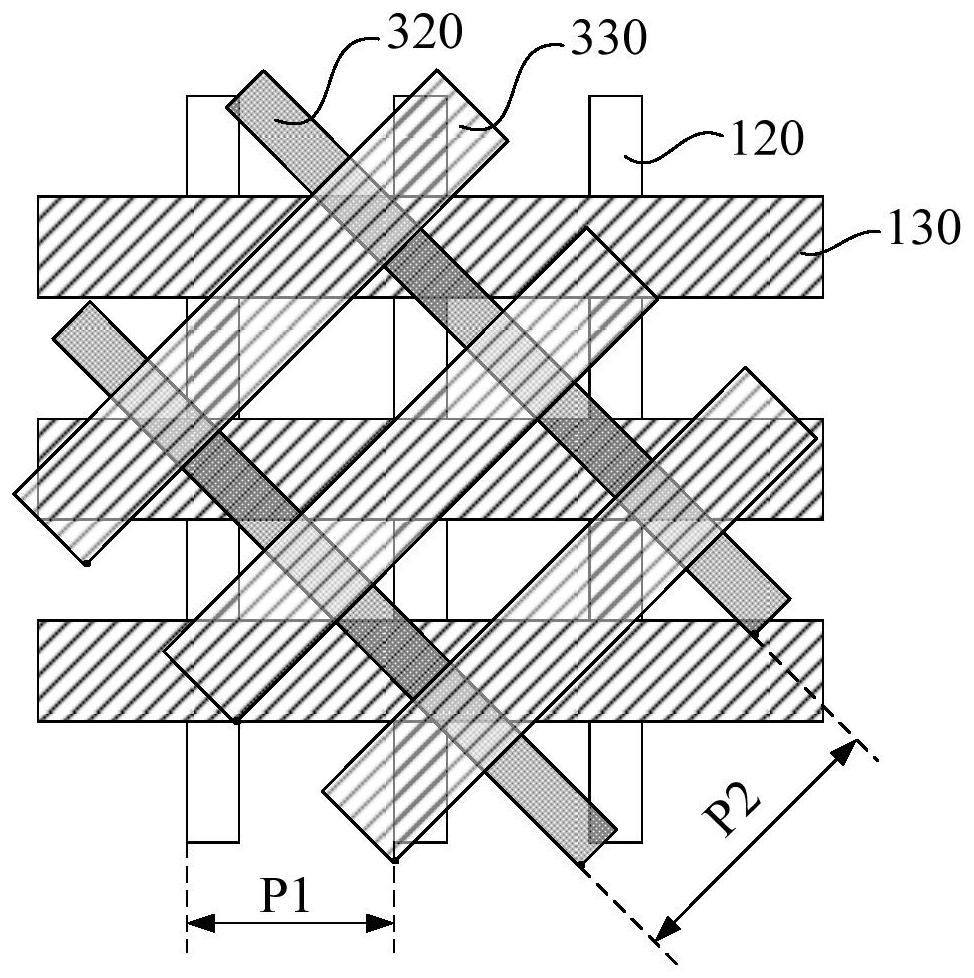

[0016] As known from the background art, the CFET device structure includes a PMOS transistor and an NMOS transistor stacked vertically on each other. However, it is currently difficult to extract the electrical properties of the underlying transistors in the CFET device structure.

[0017] Combining with a semiconductor structure, the reason why it is difficult to extract the electrical properties of the lower layer transistor in the CFET device structure is analyzed.

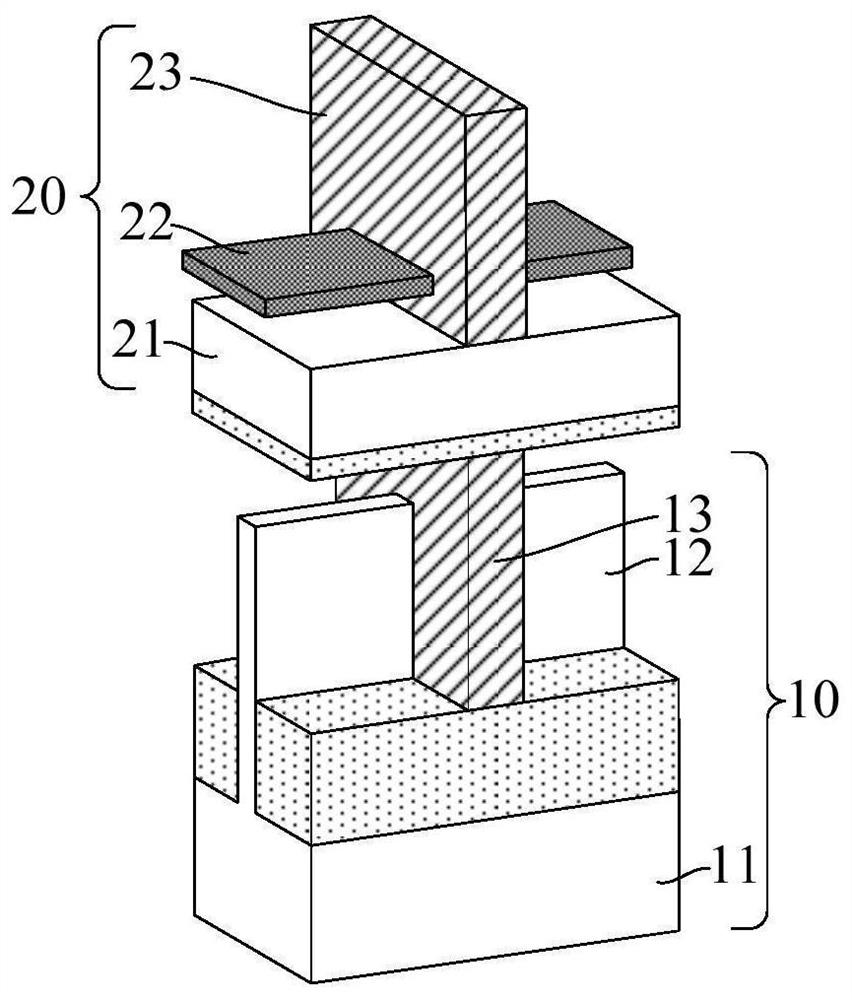

[0018] combined reference figure 1 , showing a perspective view of a semiconductor structure.

[0019] The semiconductor structure includes: a first device structure 10, including a first substrate 11, and a first device (not marked) formed on the first substrate 10, the first device includes a first device located on the first substrate 11 A channel layer structure 12, a first device gate structure 13 across the first device gate structure 12, and a first source and drain in the first channel layer structur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More