Capacitance calibration method for successive approximation type ADC (Analog to Digital Converter)

A technique of successive approximation and calibration method, which is applied in the direction of analog/digital conversion calibration/test, electrical components, code conversion, etc. It can solve the problems of capacitance mismatch, increase layout area, and huge area, so as to avoid capacitance mismatch. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The present invention will be further described below in conjunction with accompanying drawing.

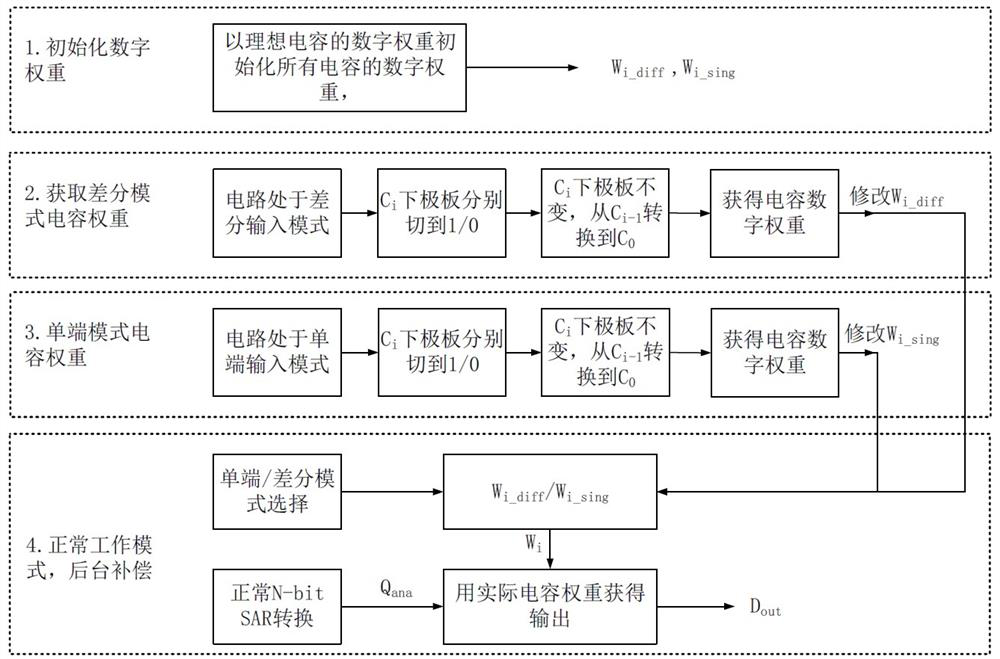

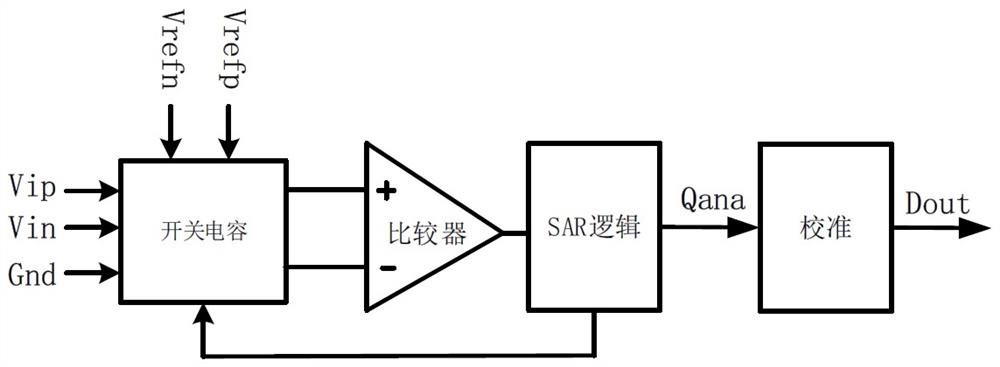

[0056] see figure 1 , image 3 and Figure 4 , the capacitor calibration method of the successive approximation ADC of the present invention, the successive approximation ADC includes a switched capacitor module, a comparator and a SAR logic module connected in sequence.

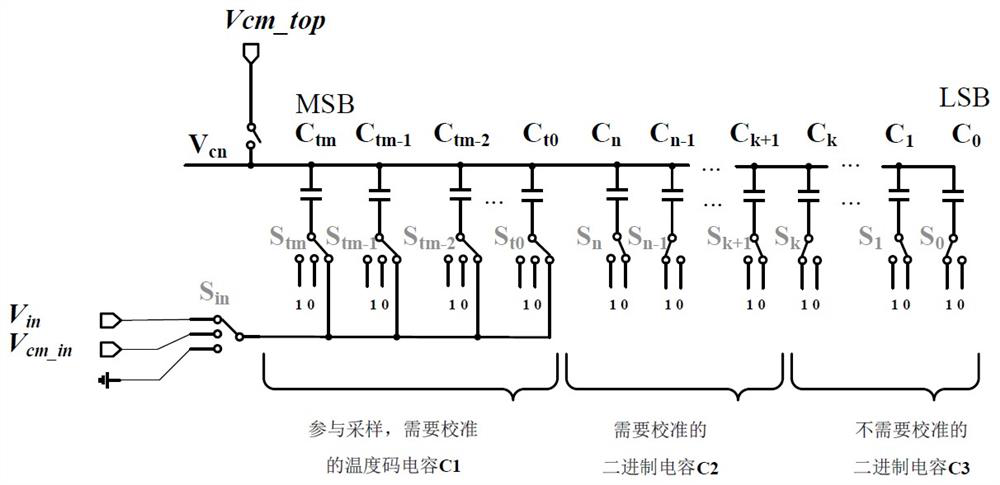

[0057] The capacitor array in the switched capacitor module includes an array of capacitors to be calibrated in sequence and a binary capacitor array C3 that does not need to be calibrated; the array of capacitors to be calibrated includes a temperature code capacitor array C1 to be calibrated in sequence and a binary capacitor to be calibrated Array C2. Capacitance sequence C in temperature code capacitor array C1 tm to C t0 , the capacitor sequence C in the binary capacitor array C2 n to C k+1 , the capacitor sequence C in the binary capacitor array C3 k to C 0 ;Switch S tm -S t0 ; Among the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More