Dynamic successive approximation register (SAR) analog-to-digital converter (ADC) (SAR-ADC) clock delay calibration system and method

A technology of SAR-ADC and analog-to-digital converter, which is applied in the direction of analog/digital conversion calibration/test, analog-to-digital converter, analog-to-digital conversion, etc., and can solve the problem that time-varying analog signals cannot accurately represent transmission data, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

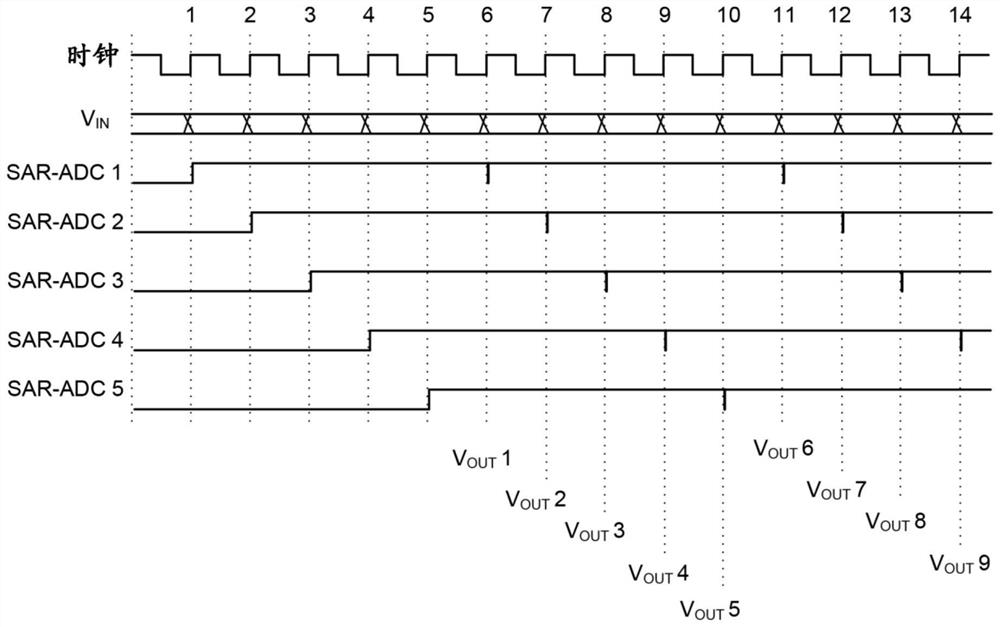

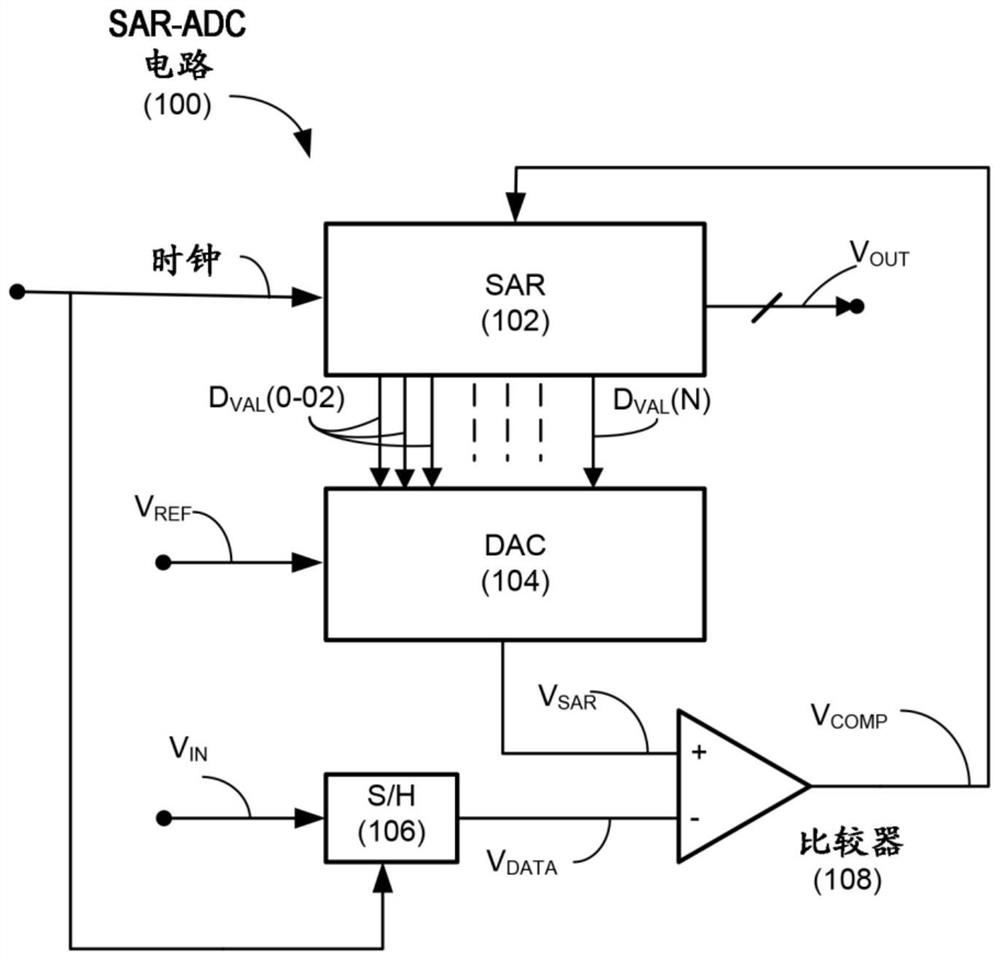

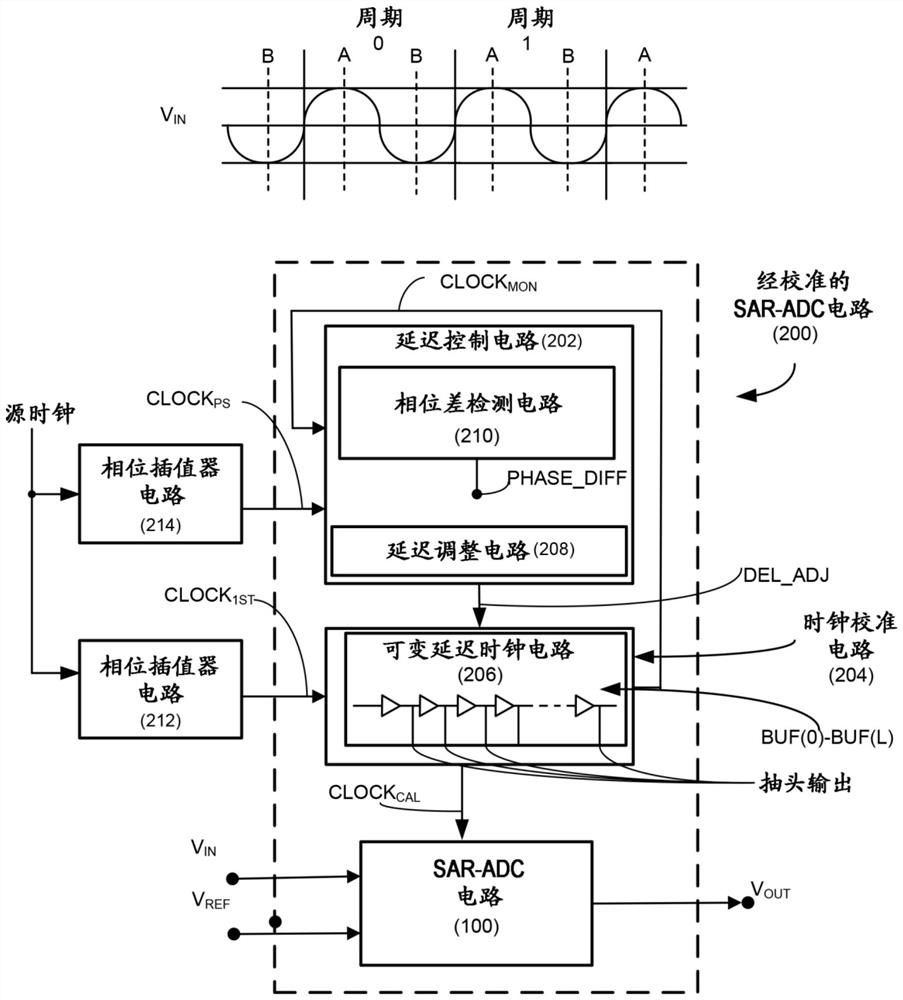

[0022] Exemplary aspects disclosed herein include dynamic successive approximation register (SAR) analog-to-digital converter (ADC) (SAR-ADC) clock calibration systems and methods. The time-interleaved SAR-ADC on the IC employs separate SAR-ADCs to sample the voltage levels of the analog signal at corresponding sampling points in sequential data cycles in a time-interleaved manner. A time-interleaved SAR-ADC converts the sampled voltage levels into serial digital data. The voltage level of a time-varying analog signal sampled outside of the sampling point in the data clock cycle may not accurately represent the transmitted data. Therefore, each individual SAR-ADC must be individually synchronized to the corresponding sampling point in the data clock cycle. To achieve synchronization, a clock source provides each individual SAR-ADC with a clock signal at a corresponding clock input that is synchronized to the sampling point(s) of the sequential data period. Clock traces (eg, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com