Sparse accelerator applied to on-chip training

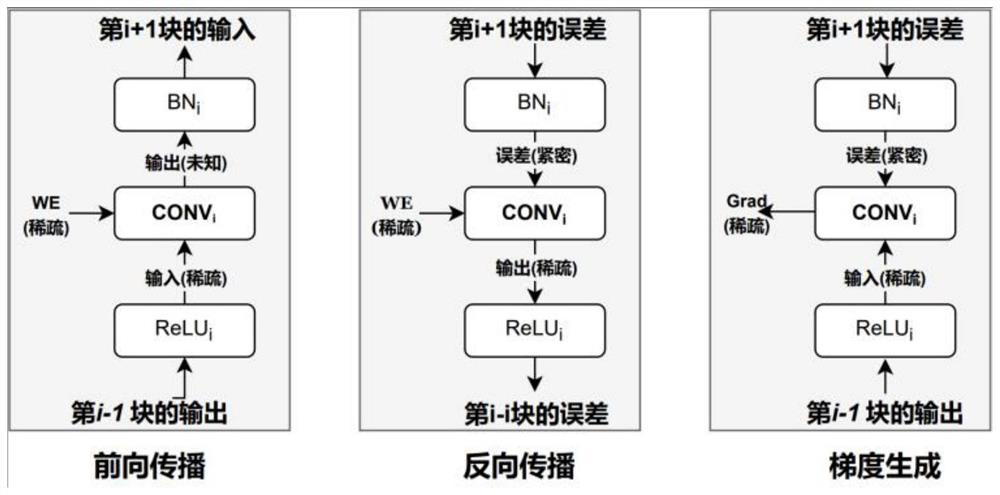

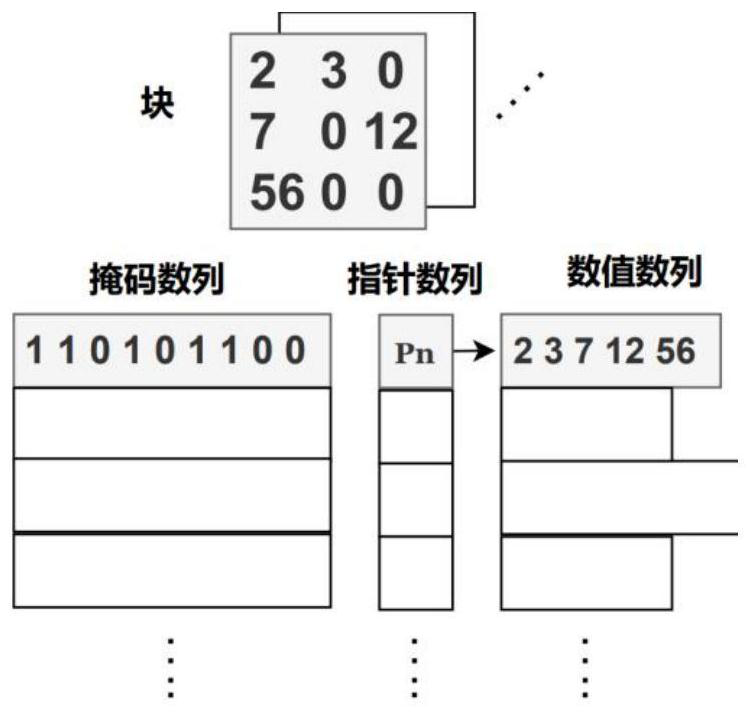

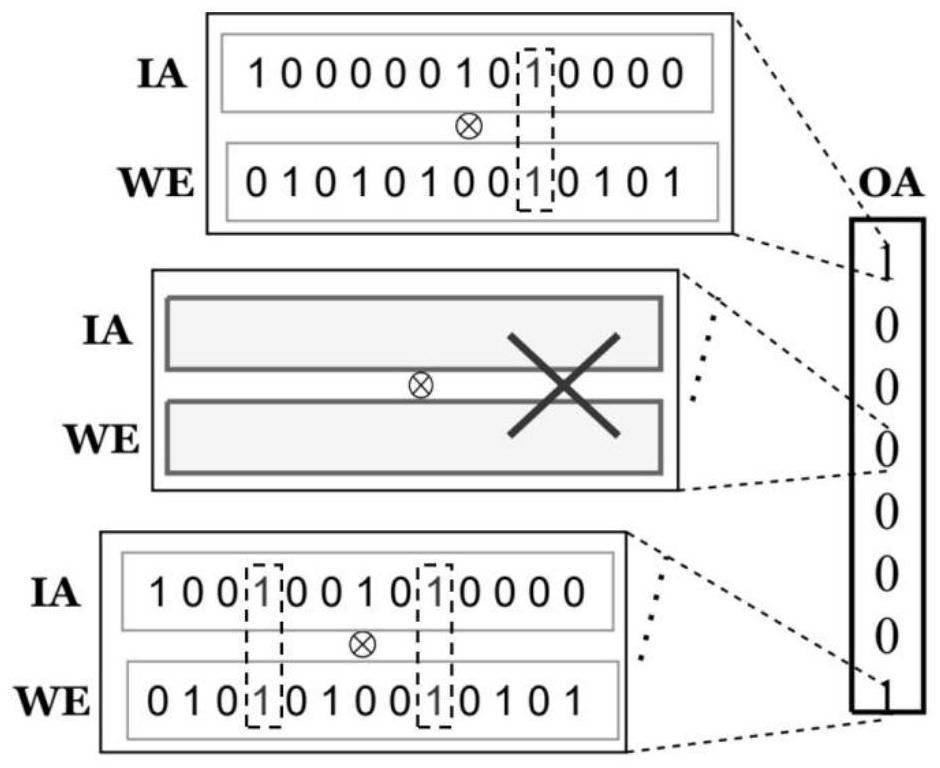

An accelerator, sparse technology, applied in biological neural network models, neural architectures, neural learning methods, etc., can solve the problems of ineffective operations on-chip training, inability to guarantee on-chip training, etc., to improve hardware utilization and accurate elimination.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] In order to make the purpose, technical solution and advantages of the present application clearer, the implementation manners of the present application will be further described in detail below in conjunction with the accompanying drawings.

[0058] The terms used in the following examples are for the purpose of describing particular examples only, and are not intended to limit the application. As used in the specification and appended claims of this application, the singular expressions "a", "an", "said", "above", "the" and "this" are intended to also Expressions such as "one or more" are included unless the context clearly dictates otherwise. It should also be understood that in the following embodiments of the present application, "at least one" and "one or more" refer to one, two or more, and "multiple" refers to two or more. The term "and / or" is used to describe the relationship between associated objects, indicating that there may be three relationships; for ex...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More