Three-dimensional packaging structure for multi-chip device integration

A three-dimensional packaging and chip packaging technology, which is applied in semiconductor devices, electric solid state devices, semiconductor/solid state device components and other directions, and can solve problems such as the influence of chip electrical performance and heat dissipation pressure.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

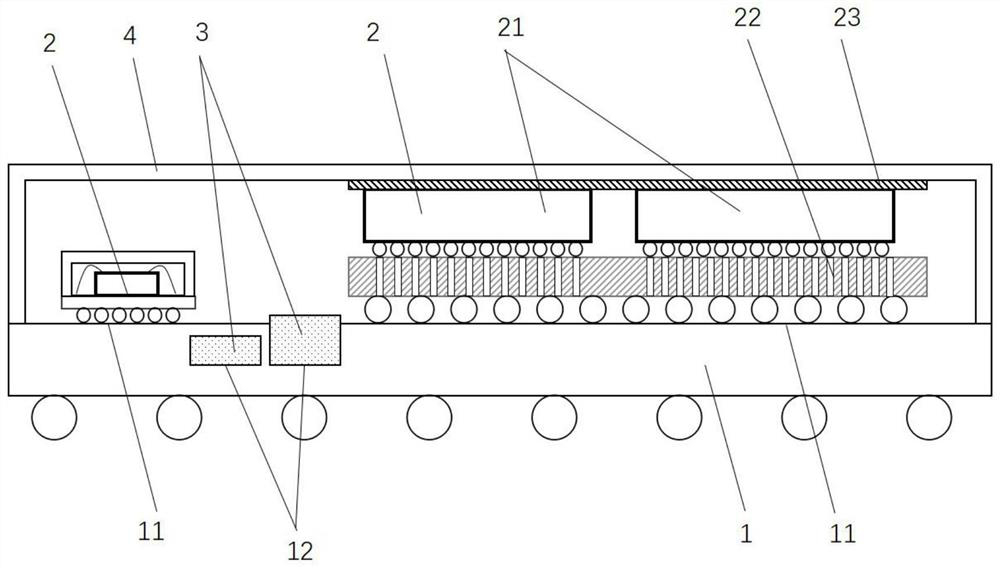

[0021] like figure 1 As shown, the three-dimensional packaging structure for multi-chip device integration in this embodiment includes a substrate 1, a chip packaging unit 2 and a working device 3. The surface of the substrate 1 is provided with a plurality of packaging areas 11 and a plurality of concave embedded In area 12, each chip packaging unit 2 is packaged and connected at the packaging area 11, and each working device 3 is embedded and connected in the embedded area 12; at least one chip packaging unit 2 includes a chip 21 and a passive silicon interposer 22, and the chip 21 is flipped and connected The top surface of the passive silicon interposer 22 is bonded and connected, and the passive silicon interposer 22 is connected to the substrate 1 through the bumps provided on the bottom surface.

[0022] In the packaging structure of this embodiment, the substrate 1 and the chip 21 are no longer correspondingly arranged, and the chip 21 and the substrate 1 are no longer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More