Sampling compensation method and device of digital channel logic analyzer

A logic analyzer and digital channel technology, applied in measuring devices, instruments, measuring electronics, etc., can solve the problems of high price, high cost of delay chips, limited number of high-speed transmission interfaces, etc., achieve high resolution and small hardware changes , the effect of low sampling cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

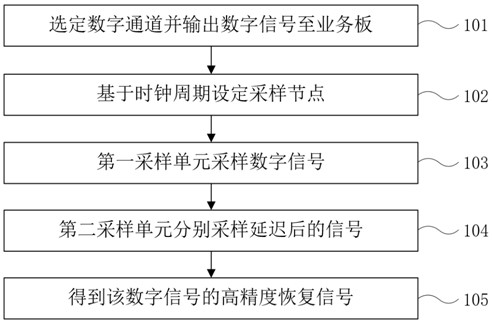

[0060] Embodiment 1 of the present invention discloses a sampling compensation method for a digital channel logic analyzer in an ATE device, which can realize high-resolution sampling. The flow chart of the sampling compensation method is attached to the instruction manual figure 1 As shown, the specific scheme is as follows:

[0061] A sampling compensation method for a digital channel logic analyzer in ATE equipment, comprising the following steps:

[0062] 101. Select the digital channel of the chip, and output the digital signal to the service board through the digital channel;

[0063] 102. Set a sampling node based on the clock cycle of the preset clock signal, and control the first sampling unit and the second sampling unit to perform sampling when each clock cycle passes through the sampling node;

[0064] 103. Sampling the digital signal by the first sampling unit to obtain first sampling data;

[0065] 104. Delay the digital signal through each sub-chain of the de...

Embodiment 2

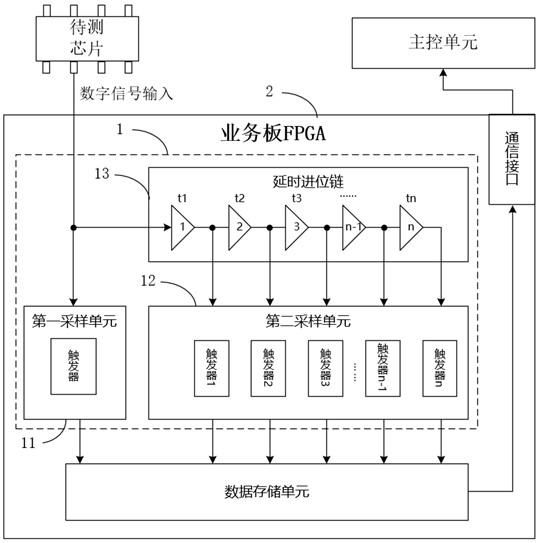

[0094] Embodiment 2 of the present invention discloses a sampling compensation device for a digital channel logic analyzer in ATE equipment, which is used to implement the sampling method of Embodiment 1. The sampling compensation device is shown in Figure 2 of the specification, and the specific scheme is as follows:

[0095] A sampling compensation device for a digital channel logic analyzer in ATE equipment, the sampling compensation device 1 is located on a service board FPGA2, and includes a first sampling unit 11, a second sampling unit 12 and a delay carry chain 13;

[0096] The first sampling unit 11 is configured with a trigger for directly sampling the digital signal received by the service board FPGA to obtain the first sampling data;

[0097] The delay carry chain 13 is composed of a plurality of sub-chains connected in series in sequence, and the output end of each sub-chain is connected to the second sampling unit, and is used for delaying the received digital si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More