DMA controller and method

A DMA controller and controller technology, applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problems of low data transmission efficiency, inability to meet multi-dimensional data, and large time consumption, so as to improve data transmission performance, high-efficiency data transmission, The effect of meeting the needs of multidimensional data

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

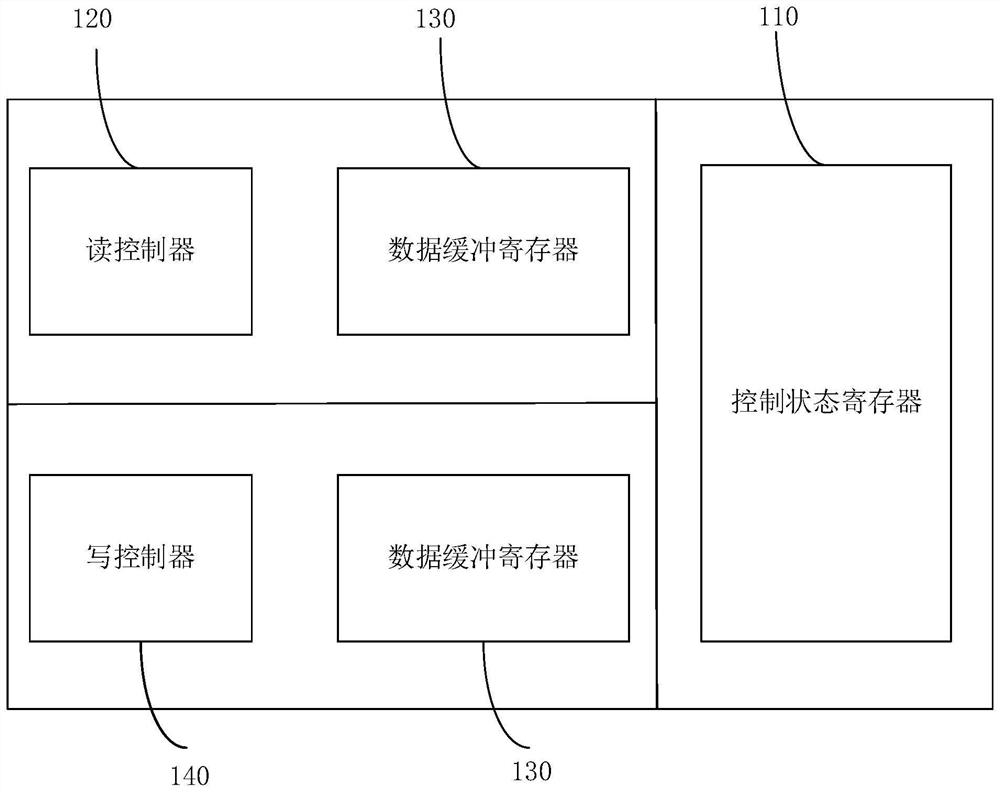

[0020] figure 1 It is a schematic diagram of a DMA controller provided by the first embodiment of the present invention. This embodiment can be applied to the situation of data transmission, and can generally be integrated in a computer, such as figure 1 shown:

[0021] Specifically, the DMA controller may include: a control status register 110 (Control Status Register, CSR), a read controller 120 (read control), and a data buffer register 130 (date buffer), wherein:

[0022] The control state register 110 is used to store the control instruction corresponding to the preset transmission mode.

[0023] The preset transmission mode may be a transmission mode preset according to the multi-dimensional data transmitted by the DMA controller. The control instruction may be an instruction that the CPU sends to the DMA controller through the bus to transmit multi-dimensional data. It can be understood that the DMA controller obtains the data address and transmission direction of the...

Embodiment 2

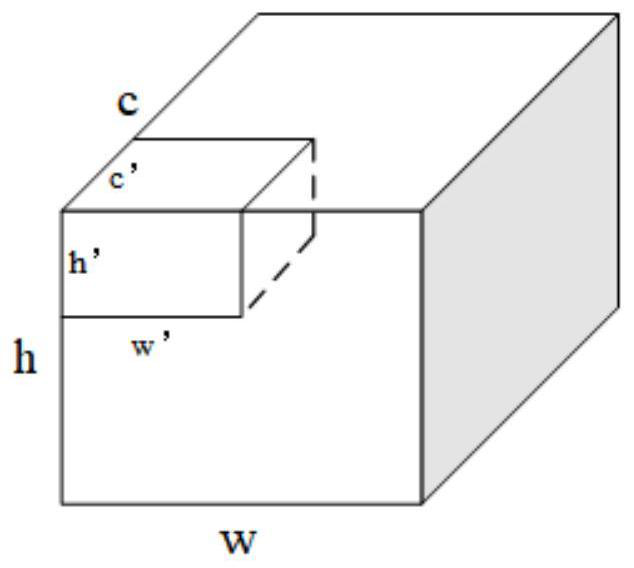

[0038] This embodiment is embodied on the basis of the above-mentioned embodiment, and further describes the control instruction of the preset transmission mode including multi-dimensional data in the DMA controller in the above-mentioned embodiment, wherein the control instruction at least includes: the reference address of the multi-dimensional data , the first cycle offset, the first cycle upper limit, and the second cycle upper limit, where:

[0039]The reference address of the multi-dimensional data may be the data address where the multi-dimensional data is stored; the upper limit of the first cycle may be the upper limit of the number of multi-dimensional data read by the first cycle; the upper limit of the second cycle may be the upper limit of the number of multi-dimensional data read by the second cycle Quantity; the first cycle offset may be the offset of the reference address after the first cycle read ends.

[0040] Step 1: Read the reference address of the multi-...

Embodiment 3

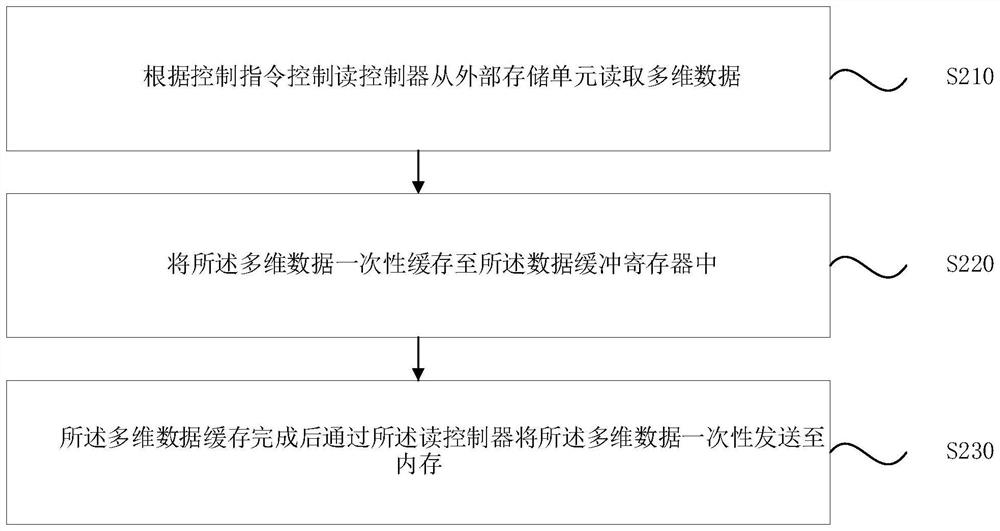

[0065] image 3 This is a schematic diagram of a DMA control method provided by Embodiment 3 of the present invention. This embodiment is applicable to the case of DMA control data transmission. The method can be executed by a DMA controller, which can generally be integrated in a computing device. like image 3 As shown, the method includes the following steps:

[0066] S210: Control the read controller to read multi-dimensional data from the external storage unit according to the control instruction.

[0067] S220, caching the multi-dimensional data in the data buffer register at one time;

[0068] S230. After the multi-dimensional data cache is completed, the read controller sends the multi-dimensional data to the memory at one time.

[0069] Optionally, the method further includes:

[0070] Controlling the write controller to obtain the multi-dimensional data from the data buffer register at one time according to a control instruction;

[0071] After the multi-dimensi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More