Pulse generator circuit

A technology of pulse generation circuit and circuit, applied in the direction of pulse processing, pulse shaping, pulse technology, etc., to achieve the effect of strong ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

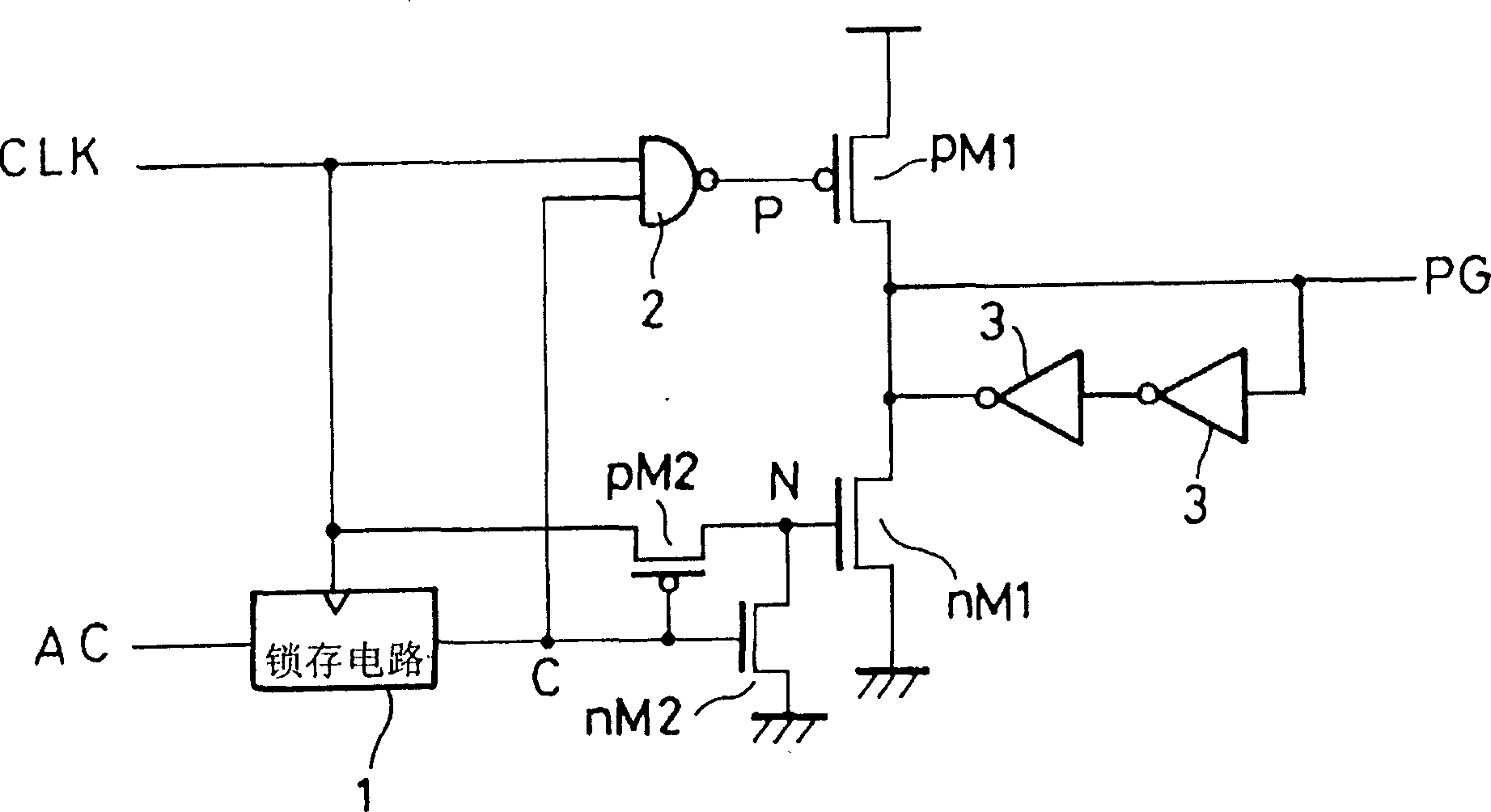

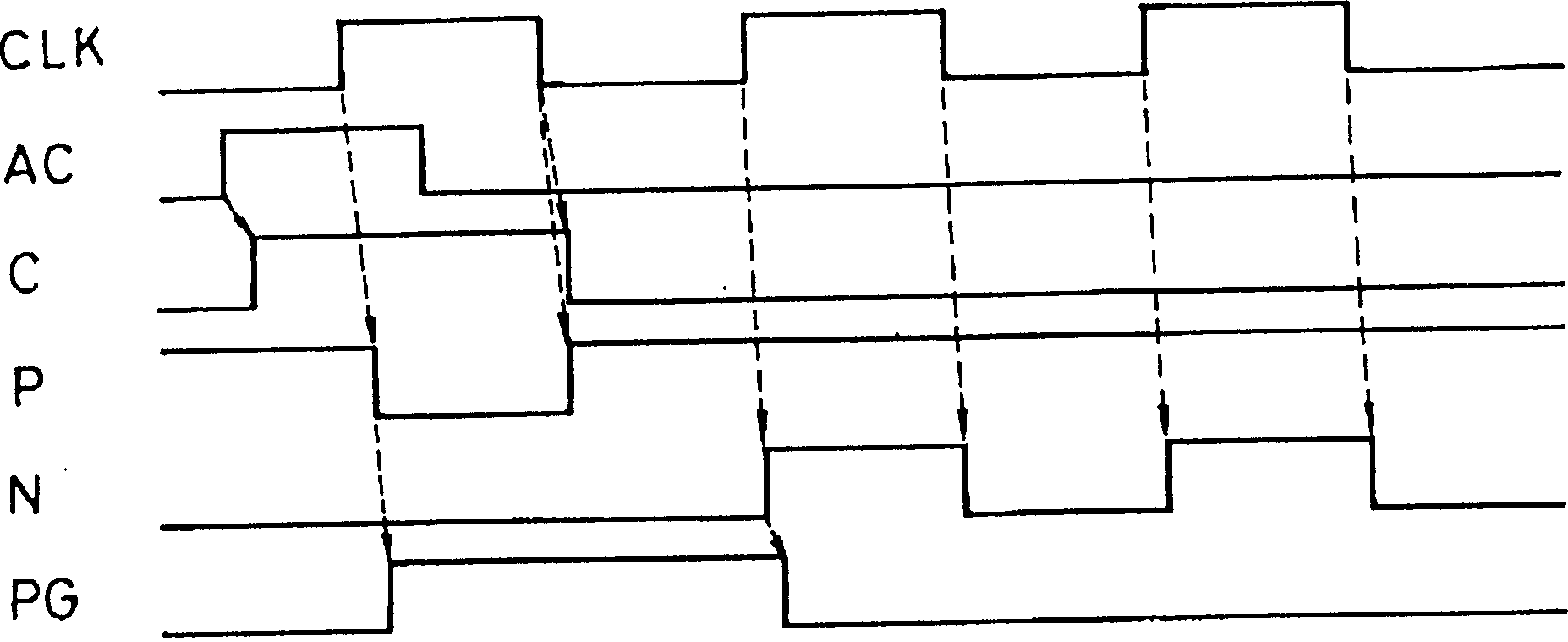

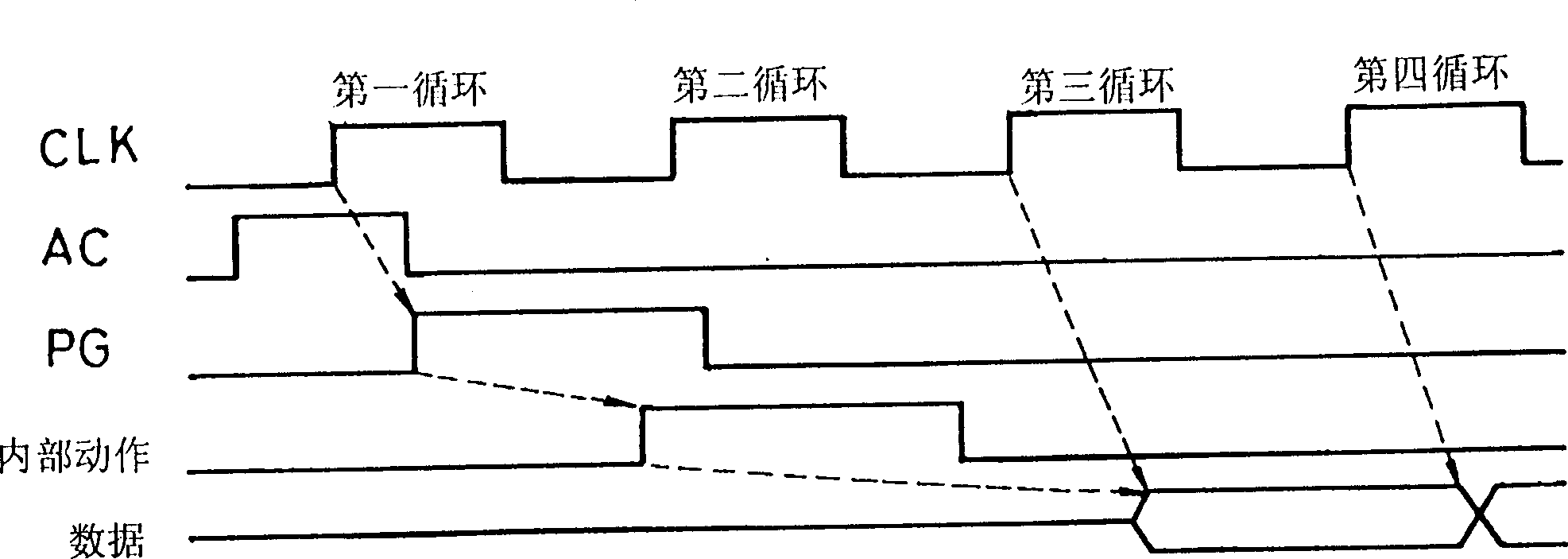

[0024] Hereinafter, embodiments of the present invention will be specifically described with reference to the drawings. figure 1 Is a circuit diagram showing a pulse generating circuit of an embodiment of the present invention, figure 2 It is a timing chart of the circuit operation.

[0025] The operation start signal AC and the clock signal CLK are input to the latch circuit 1, and a signal C that rises when the signal AC is high (burst start signal) and falls when the clock signal CLK falls. Therefore, the latch circuit 1 generates a signal C that expands the high level of AC (burst start signal) to the lower edge of CLK.

[0026] The output C of the latch circuit 1 is input to the gates of the n-type MOS transistor nM2 and the p-type MOS transistor pM2. In addition to inputting the clock signal CLK to the latch circuit 1, it is also input to the NAND circuit 2 and the transistor pM2. The output C of the latch circuit 1 is input to the other input terminal of the NAND circuit ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More