Iterative model establishment method and simulation method of cross-point storage array

A storage array and model building technology, applied to CAD circuit design, etc., can solve the problems of high simulation overhead, high time complexity and space complexity, and low simulation efficiency, so as to reduce simulation overhead, improve simulation efficiency, and reduce time The effect of space complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

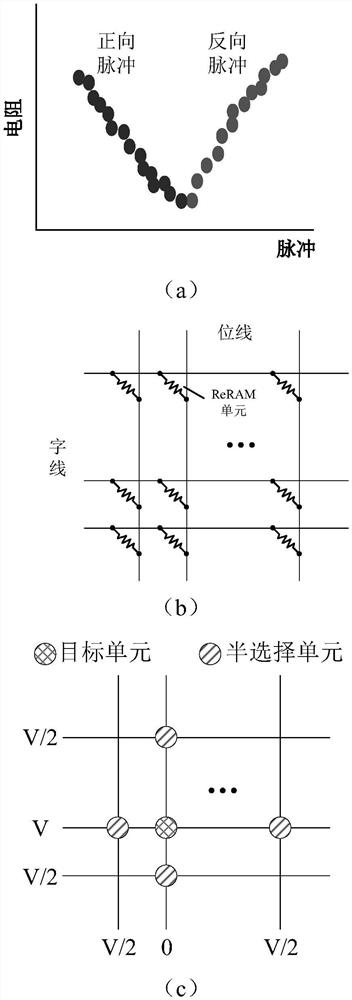

[0048] An iterative model building method for a cross-point storage array; in this embodiment, the cross-point storage array uses the high and low values of memory cell resistances to represent stored information, and the total number of word lines m and the total number of bit lines n of the cross-point storage array satisfy :

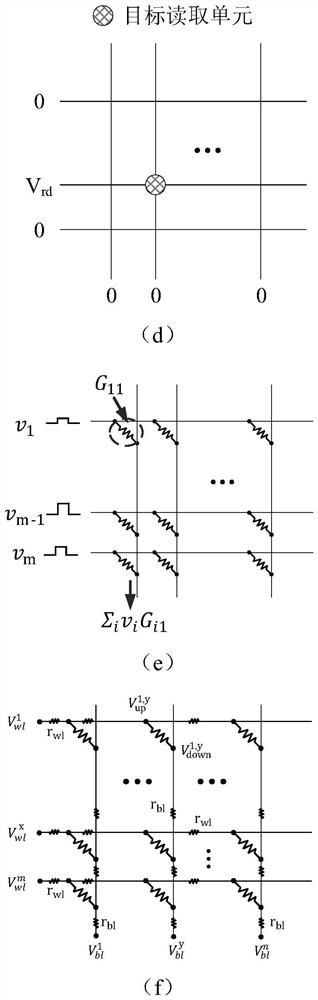

[0049] In this embodiment, the method for establishing an iterative model of a cross-point storage array includes: for a target memory cell located at (x, y) in the cross-point storage array, establishing the following iterative model based on Kirchhoff's voltage law:

[0050]

[0051] Among them, x and y respectively represent the number of the word line and bit line where the target memory cell is located, 1≤x≤m, 1≤y≤n; represents the voltage applied on the word line where the target memory cell is located, Represents the voltage applied on the bit line where the target memory cell is located; r wl Represents the line resistance between t...

Embodiment 2

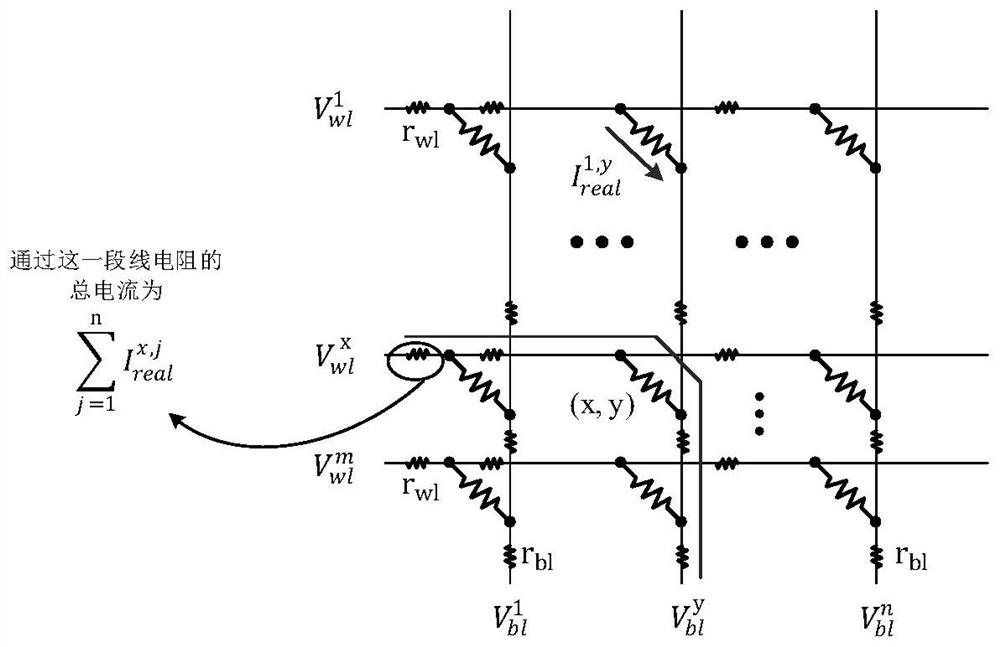

[0089] A method for simulating a cross-point storage array, this embodiment is proposed based on the method for establishing an iterative model of a cross-point storage array provided in the above-mentioned Embodiment 1, refer to image 3 and Figure 4 , this embodiment includes the following steps:

[0090] (S1) Initialize the voltage of each node in the cross-point memory array according to the word line voltage and bit line voltage to be applied, and form a voltage matrix V by the voltage of the upper node of each memory cell up , the voltage matrix V is formed by the voltage of the lower node of each memory cell down , and initialize the current number of iterations to k=1;

[0091] The upper node of the storage unit is the node formed by the intersection of the storage unit and the word line where it is located, and the lower node of the storage unit is the node formed by the intersection of the storage unit and the bit line where it is located;

[0092] As an optional...

Embodiment 3

[0114] A method for simulating a cross point memory array, this embodiment is similar to the above-mentioned Embodiment 2, the difference is that in step (S1) of this embodiment, according to the word line voltage and the bit line voltage to be applied, the cross point is initialized The voltage of each node in the point storage array, including:

[0115] According to the word line voltage and bit line voltage to be applied, and the conductance matrix G of each memory cell, the corresponding node initial voltage matrix is searched from the pre-established mapping table, and the corresponding initial voltage matrix of each node is initialized according to the node initial voltage matrix. Voltage;

[0116] The node initial voltage matrix is used to record the initial voltage value of each node in the simulation process, and the mapping table is used to record the correspondence between the combination of word line voltage, bit line voltage and conductance matrix and the node...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More