Interleave address generating device and interleave address generating method

An address generation and address technology, applied in the direction of error correction/detection, encoding, electrical components, etc. using interleaving technology, can solve the problems of large memory space and large interleaved address pattern generation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0051] The interleaving address generating apparatus of Embodiment 1 performs row sorting processing and column sorting processing in parallel.

[0052] FIG. 4 is a block diagram showing the structure of the apparatus for generating interleaved addresses according to Embodiment 1 of the present invention.

[0053] The interleave address generation apparatus 100 shown in FIG. 4 mainly includes a counter control unit 101 , a bit inversion unit 102 , a column conversion unit 103 , a shift register 104 , an adder 105 , and a size comparison unit 106 .

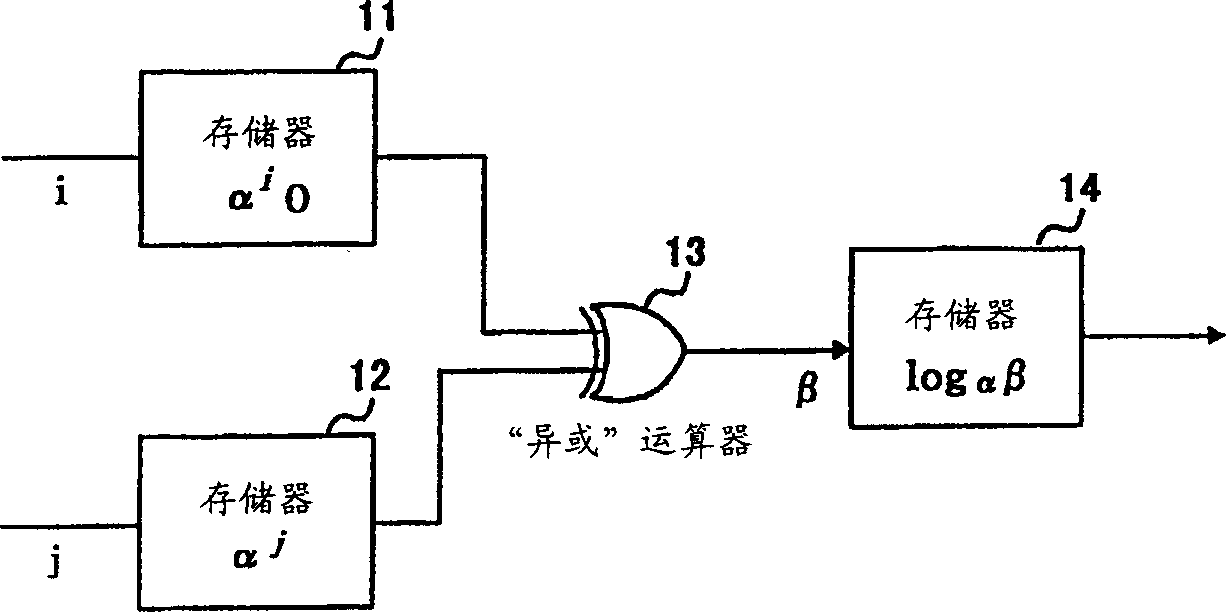

[0054] In addition, the column transformation device 103 includes a memory 110 , a memory 111 , a memory 113 , and an exclusive-OR operator 112 .

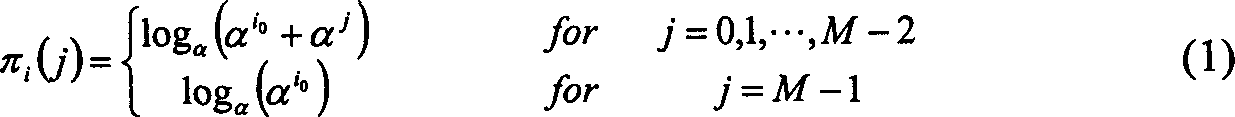

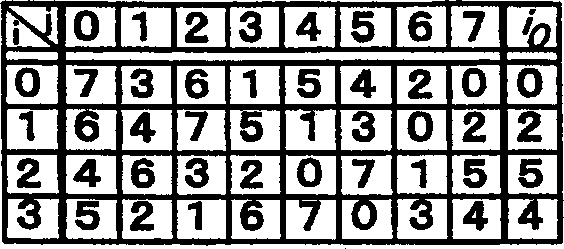

[0055] In FIG. 4, the counter control unit 101 assigns the row number i of the two-dimensional array (0≤i2 ) is output to the bit inversion device 102, and the column number j of the two-dimensional array (0≤03 ) are output to the memory 111 .

[0056] For example, the counter control ...

Embodiment 2

[0089] FIG. 7 is a block diagram showing an example of the configuration of the interleave address generating apparatus according to the second embodiment. Here, the same reference numerals as those in FIG. 4 are attached to the same structures as those in FIG. 4 , and detailed descriptions thereof are omitted.

[0090] The interleaving address generating apparatus 150 of FIG. 7 is different from that of FIG. 4 in that it includes a memory cell array 151 and adds offset addresses according to the timing of the output from the memory 113 .

[0091] In FIG. 7, the memory cell array 151 temporarily stores the row number i' output from the bit inversion device 102, and then outputs it to the shift register 104.

[0092] For example, with respect to the output value i' from the bit inversion device 102, the memory cell array 151 is composed of a two-stage memory cell array in order to match the timing of the output from the column conversion device 103 and the output from the shift...

Embodiment 3

[0097] FIG. 8 is a block diagram showing an example of the configuration of the interleave address generating apparatus according to the third embodiment.

[0098] In FIG. 8 , the counter control unit 201 outputs the row number i of the two-dimensional array to the memory 202 , and outputs the column number j of the two-dimensional array to the memory 203 .

[0099] The memory 202 stores N(i) corresponding to the input i, and outputs N(i) corresponding to the i output from the counter control unit 201 to the multiplier 204 .

[0100]The memory 203 stores M(j) corresponding to the input j, and outputs M(j) corresponding to the j output from the counter control unit 201 to the adder 205 .

[0101] The adder 205 adds the multiplication result output from the multiplier 204 to M(j) output from the memory 203 , and outputs the addition result to the size comparison unit 206 .

[0102] The size comparison unit 206 outputs the addition result as the interleaving address when the add...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More